ultrascale gty transceiver 笔记

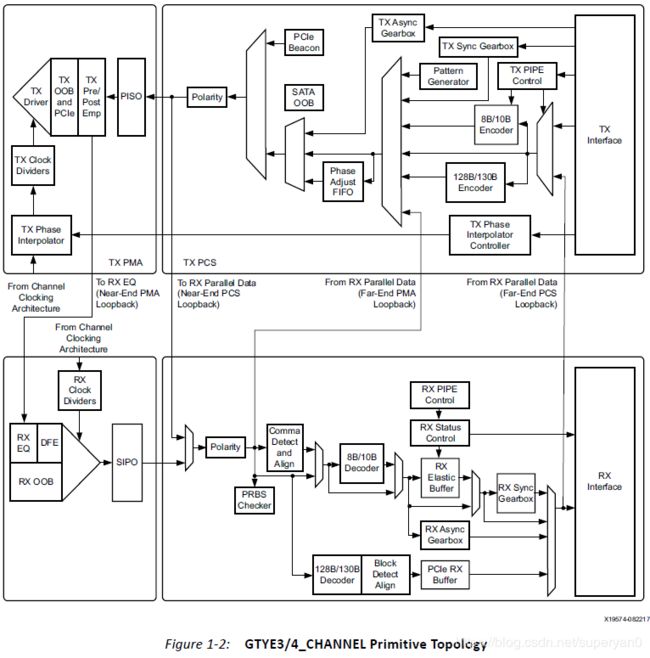

Xilinx的高速串行收发器中包括PMA和PCS两个子层,其中PMA子层主要用于串行化和解串,PCS主要包括线路编码和CRC校验编码。

PCS(Physical Coding Sublayer) 物理编码子层

PCS子层负责8b/10b编码解码和CRC校验,并集成了负责channel绑定和时钟修正的弹性缓冲。8b/10b编码可以避免数据流中出现连0连1的情况,便于时钟的恢复。channel绑定通过在发送数据流中加入P字符来将几个RocketIO通道绑定成一个一致的并行通道,从而来提高数据的吞吐率。最多支持24个通道的绑定。弹性缓冲可以解决恢复时钟与本地时钟的不一致问题,并进行数据率的匹配,从而使得channel绑定成为可能。对Rocket IO模块的配置,可以通过下面两种方式进行:静态特性可以通过HDL代码设置;动态特性可以通过RocketIO的原语端口进行配置。

PCS 层的功能是负责产生空闲序列、通道分段、发送编码、接收解码、通道对齐和在接收时进行通道合并[11]。PCS层使用8B/10B 编码在整个链路上发送数据。

状态的方法。该层容许在发送端和接收端之间存在时钟差异而无需流量控制。

在发送端PCS 层主要执行以下功能:

? 将队列中等待发送的包和定界控制符号提取出来组成字符流。

? 分段发送字符流到可用通道上。

? 当没有等待发送的包和定界控制符号时,产生空闲序列并将其插入到每个

通道发送的字符流中。

? 将每个通道的字符流独立编码为 10 组并行码组。

? 将形成的 10 位并行码组传递给PMA 层。

在接收端PCS 层主要执行以下功能:

? 解码 10 位并行码组的接收流为各通道独立的符号。

? 把从无效码组解码得到的字符标记为无效。

? 如果链路使用多于一个的通道,对其字符流来消除通道间的偏移并将每个

通道上的字符流重新组装为一个单独的字符流。

? 将解码字符流得到的包和定界控制符号递送到更高层。

PMA(Physical Medium Attachment) 物理媒介适配层

PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。SERDES是一个串并转换器,负责FPGA中本地的32位并行数据(也可以是16位或8位)与RocketIO接口的串行数据之间的转换。采用串行数据收发,可以在高频条件下很好地避免数据间的串扰。时钟发生器及时钟恢复电路用于将时钟与数据绑定发送,以及将时钟从接收到的数据流中恢复出来,从而避免了在高速传输条件下时钟与数据分开传输所带来的时钟抖动等问题。

PMA 层的功能是逐通道将并行码组串行化为串行比特流,或将串行比特流转换为并行码组。在接收数据时,PMA 层的功能是将接收到的比特流逐通道分别对齐到10 位码组边界。接着该层向PCS 层的每一个通道提供一个连续的码组流。码组在PCS 层以上的各层是不可见的。更重要的是,PMA 层还负责物理层的时钟管理,在发送端由PLL 提供时钟进行数据的同步,在接收端由CDR将串行的数据比特流中的时钟信息提取出来,用于数据的判决。

PMA 层包括串行器和解串器,串行器和解串器负责从并行到串行和从串行到并行的转换。串行器需要时钟产生电路,时钟产生电路通常由PLL来实现。解串器需要CDR 从接收的串行数据中恢复出时钟信号,CDR 通常也可由PLL 来实现,但也有其它多种实现形式,如后文介绍的延迟环、过采样等。

Transmitter

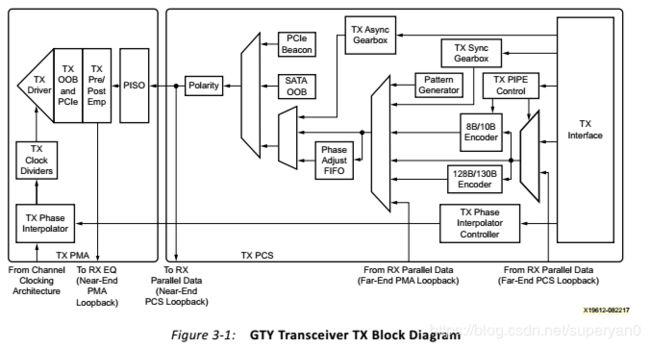

每个transceiver包括一个独立的transmitter,它由一个PCS和一个PMA组成。图3-1显示了发射器的功能块。并行数据从设备逻辑流入TX接口,通过PCS和PMA,然后作为高速串行数据输出TX驱动程序。

TX Interface

TX接口是GTY收发器TX数据路径的网关。应用程序通过GTY transceiver 发送的数据 ,数据通过TXDATA端口在TXUSRCLK2上升沿写入,端口的宽度可以配置为2、4、8或16字节宽。端口的实际宽度取决于TX_DATA_WIDTH和TX_INT_DATAWIDTH属性以及TX8B10BEN端口设置。端口宽度可以是16、20、32、40、64、80、128和160位。接口上并行时钟(txusrck2)的速率由tx line rate、txdata端口的宽度以及是否启用8b/10b编码决定。必须为发送器中的内部PCS逻辑提供第二个并行时钟(TXUSRCLK)。下面将介绍了如何驱动并行时钟,并解释了这些时钟的限制条件,以便正确操作。最高的发送器数据速率需要一个8字节的接口,以在指定的操作范围内实现TXUSRCLK2速率。

Interface Width Configuration

GTY收发器包含2字节、4字节和8字节内部数据路径(internal datapaths),并且可通过设置TX_INT_DATAWIDTH属性进行配置。接口宽度可通过设置TX_DATA_WIDTH属性进行配置。当启用8b/10b编码器时,必须将TX_DATA_WIDTH属性配置为20位、40位或80位,在这种情况下,tx接口仅使用txdata端口。例如,当接口宽度为16时,使用txdata[15:0]。当绕过8b/10b编码器时,可以将TX_DATA_WIDTH属性配置为任何可用宽度:16、20、32、40、64、80、128或160位。

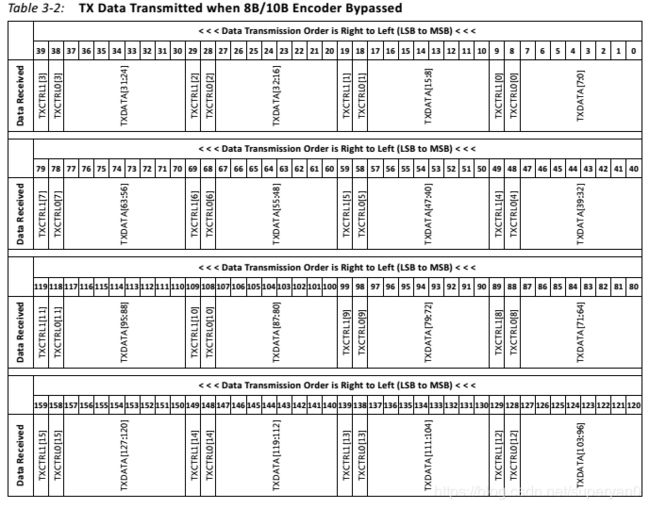

当绕过8b/10b编码器且tx_数据_宽度为20、40、80或160时,txctrl1和txctrl0端口用于将tx data端口从16位扩展到20位、32位扩展到40位、64位扩展到80位或128位扩展到160位。表3-2显示了禁用8b/10b编码器时传输的数据。当tx_数据_宽度为16、32或64时,忽略txctrl1/0端口,数据传输顺序与表3-2相同,但没有txctrl1/0位。使用TX变速箱时,请参阅第116页的TX同步变速箱以获取数据传输顺序。

TXUSRCLK and TXUSRCLK2 Generation

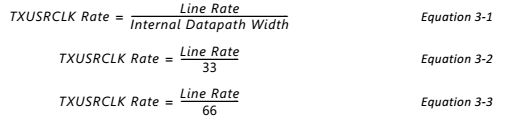

TX接口包括两个并行时钟:TXUSRCLK和TXUSRCLK2。txusrclk是GTY发送器中PCS逻辑的内部时钟。TXUSRCLK所需的速率取决于gtye3/4_通道原语的内部数据路径宽度和gty发送器的Tx线路速率。公式3-1显示了如何计算TxUSRCLK在所有情况下所需的速率,Tx异步齿轮箱启用时除外。

TXUSRCLK2是进入GTY收发器TX侧的所有信号的主同步时钟。大多数进入GTY收发器TX侧的信号都在TXUSRCLK2的正边缘上采样。txusrck2和txusrclk具有基于tx_data_width和tx_int_datawidth设置的固定速率关系。表3-3显示了这种关系

在txusrck2和txusrclk之间,每个tx_data_width和tx_int_datawidth值。在给定的行速率之上,需要使用4字节或8字节的内部数据路径。有关每个速度等级的详细信息,请参阅UltraScale和UltraScale+设备数据表。

对于txusrclk和txusrck2,必须遵守以下有关时钟之间关系的规则:

•txusrclk和txusrck2必须是正边对齐,它们之间的倾斜度尽可能小。因此,必须使用低歪斜时钟资源(bufg-gts)来驱动txusrclk和txusrck2。

•即使它们可能以不同的频率运行,txusrclk、txusrck2和发射机基准时钟必须具有与其源相同的振荡器。因此,txusrclk和txusrclk2必须乘以或除以发射机基准时钟的版本。

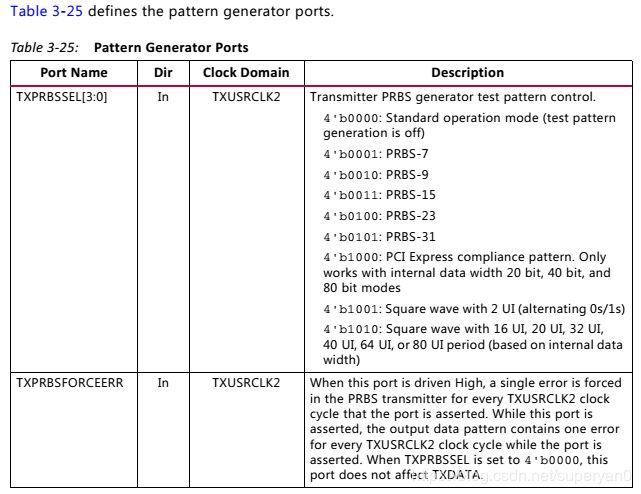

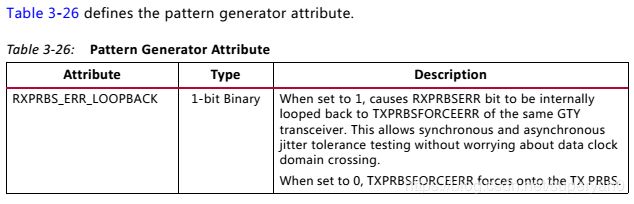

TX Pattern Generator

伪随机位序列(prbs)是测试高速链路信号完整性的常用方法。这些序列看起来是随机的,但具有可用于测量链接质量的特定属性。GTY收发器模式发生器模块可生成表3-23中列出的几个行业标准PRBS模式。

支持错误插入功能验证链路连接,也支持抖动容限测试。当需要反向PRBS模式时,TXPOLARITY

信号用于控制极性。

当TXPRBSFORCEERR被驱动到高电平时,PRBS发送器都会强制发送一个错误。对于每个TXUSRCLK2时钟周期都包含一个错误。当txprbssel设置为4'b0000时,此端口不影响txdata