ZYNQ平台学习--(1)新建工程

1.建立工程

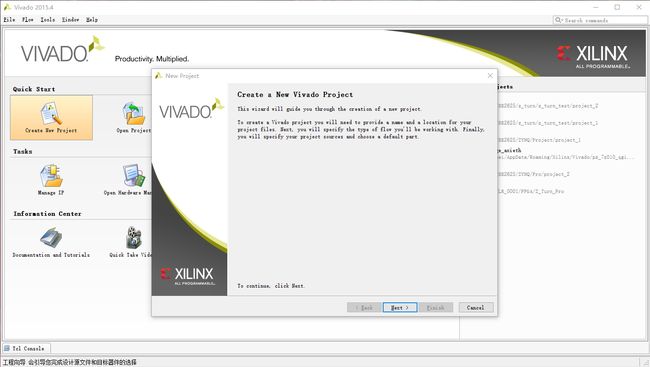

打开Vivado软件,在欢迎界面点击 Create New Project,即可新建工程。如图1所示,点击Next。

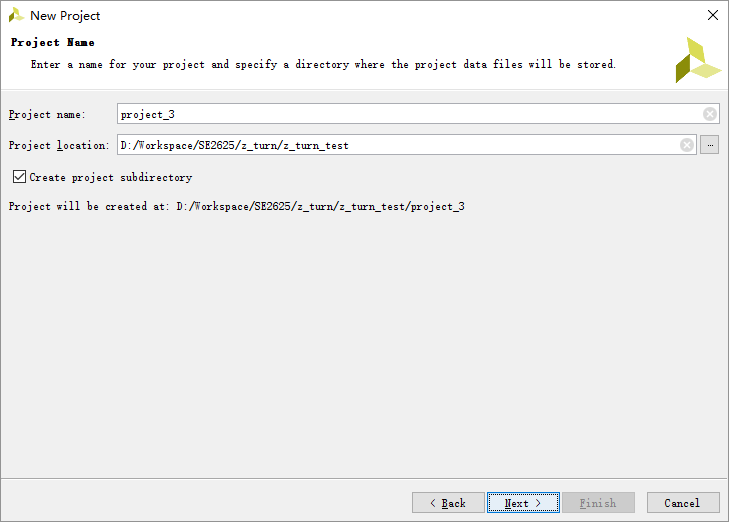

输入工程名和工程位置,并勾选Create project subdirectory,然后点击Next,如图2所示。

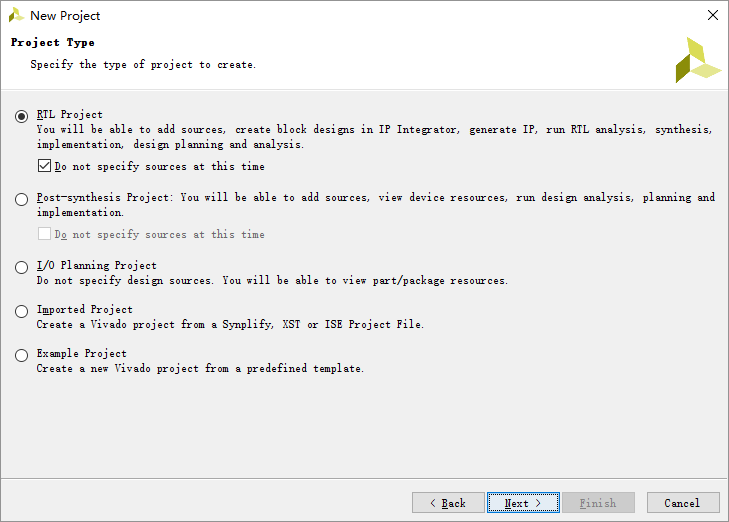

选择RTL Project,勾选Do not specify......(这样可以跳过添加源文件的步骤,源文件可以后面再添加),点击Next,如图3所示。

根据自己的开发板选择器件型号,可以直接通过型号进行搜索,例如本项目中使用的芯片型号为xc7z010clg400-1,点击Next,如图4所示。

点击Finish,如图5所示,项目新建完成。

2.添加模块

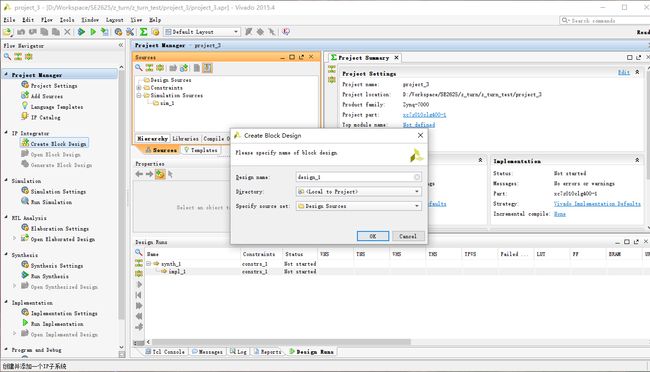

在Flow Navigater窗口中,点击Create Block Design,新建Block并命名,如图6所示。点击OK添加。

2.1添加ARM核

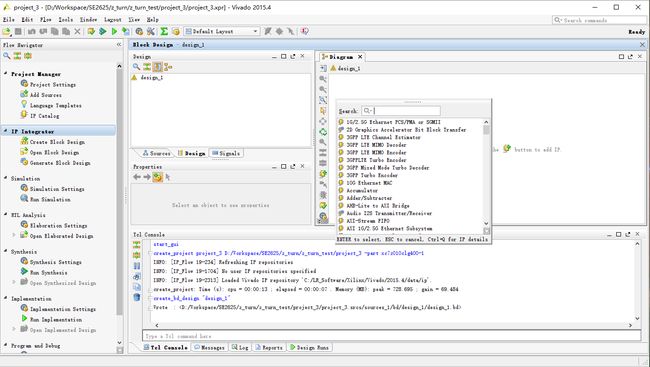

在Diagram窗口中,点击中间的图标添加ARM核,如图7所示。添加ZYNQ7 Processing System。

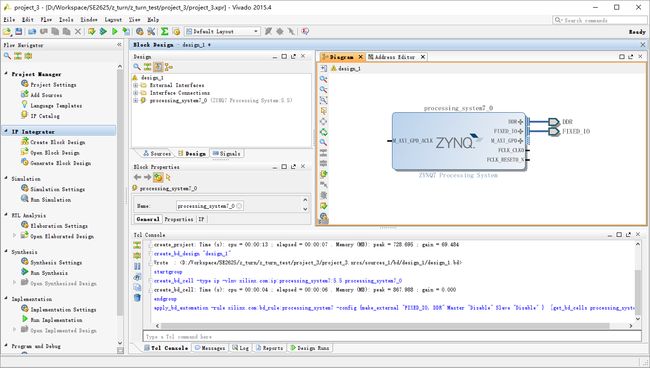

然后点击Run Block Automation,进行I/O连接,在弹出的窗口中,点击OK,如图8所示。

ARM添加完成,如图9所示。

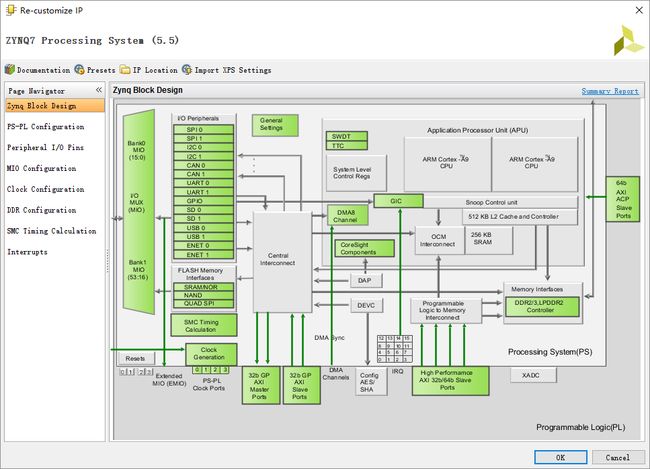

在Diagram窗口中,双击ARM核,弹出配置窗口,如图10所示。

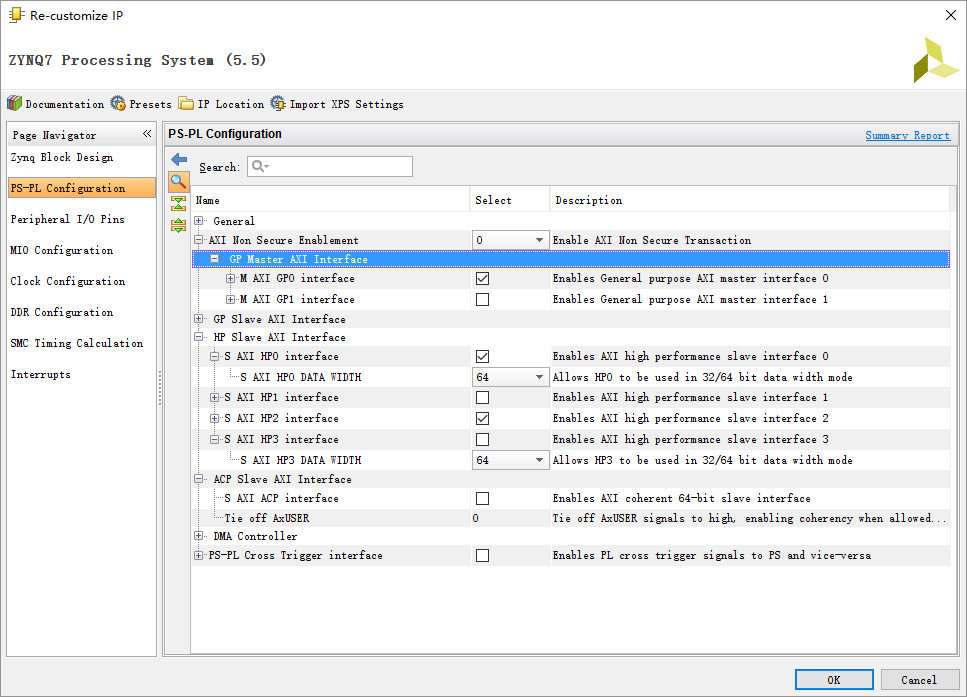

点击PS-PL Configuration,配置PL与PS之间的AMBA总线。PL与PS之间的总线主要有三种:

- AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

- AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)。

- AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口

展开AXI Non Secure Enablement和GP Master AXI Interface,勾选M AXI GP0 interface;展开HP Slave AXI Interface,勾选S AXI HP0 interface和S AXI HP2 interface。如图11所示。

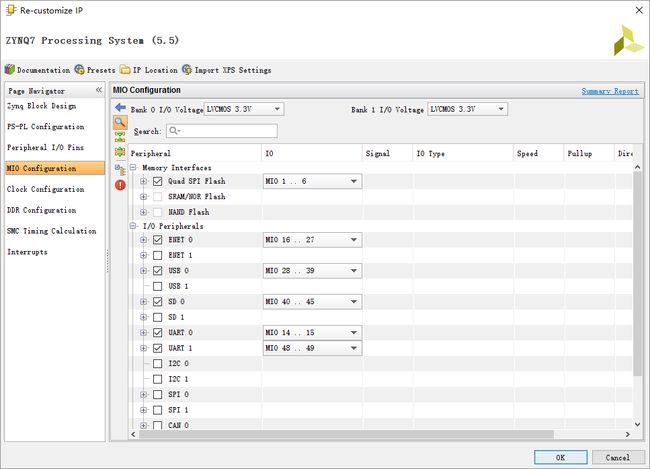

点击MIO Configuration,配置PS的引脚功能。在本项目中,Bank0的电压为3.3V,Bank1的电压为1.8V,如图12所示。

注:当使用eMMC的时候,SD的CP引脚和WP引脚需要配置EMIO,并连接到低电平上。

点击Clock Configuration,配置Zynq的时钟,如图13所示。

注:如出现SD卡识别异常的时候,可以降低SDIO的时钟频率。

点击DDR Configuration,根据DDR芯片的要求,配置DDR的时序。如图14所示。

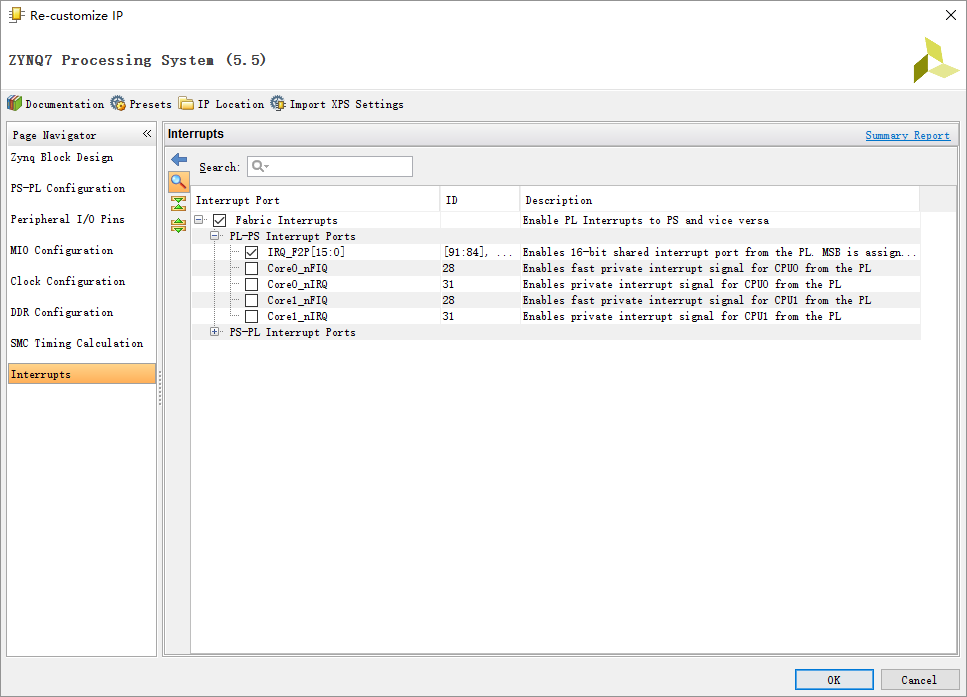

点击Interrupts,设置PL到PS的中断,勾选Fabric Interrupts,然后展开PL-PS Interrupt ports,勾选IRQ_F2P[15:0]。如图15所示。

2.2添加其他IP

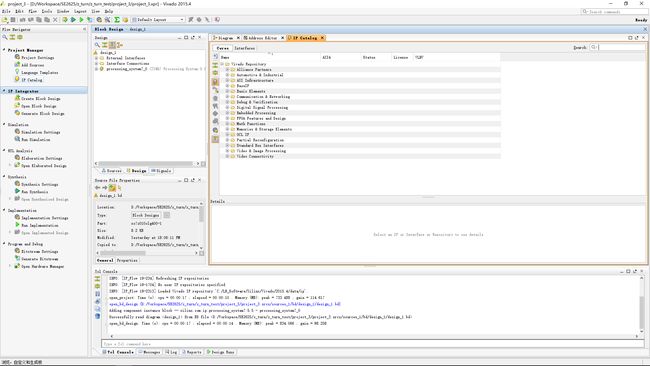

选择Flow Navigator窗口中的IP Catalog,如图16所示。在IP列表中选择需要使用的IP,添加到Diagram中,并进行配置。

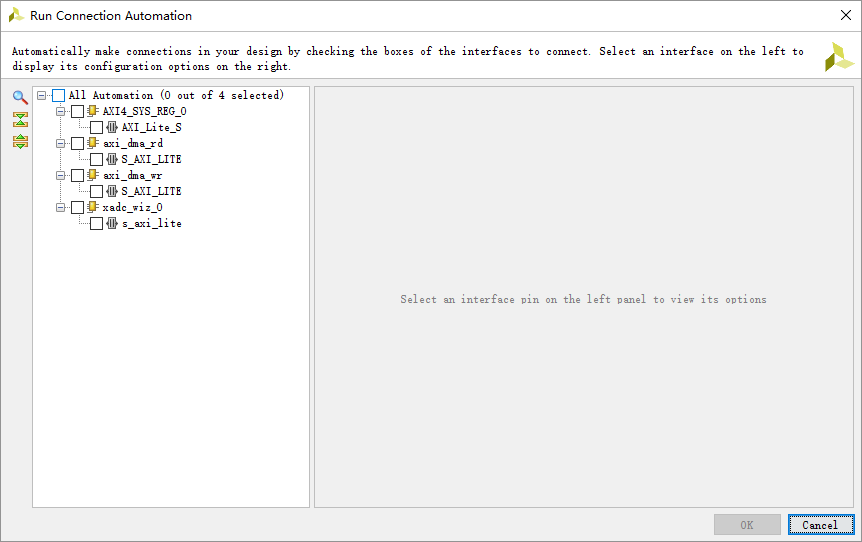

在Vivado中,IP一般都使用的AXI-Lite总线或AXI-Stream总线,而PS提供的AXI_GP和AXI_HP都是标准AXI4总线,需要使用AXI互联模块进行适配后与其他的IP连接。不过Vivado提供自动连接功能的,当IP添加完成后,点击Run Connection Automation就可以自动连接。如图17所示。

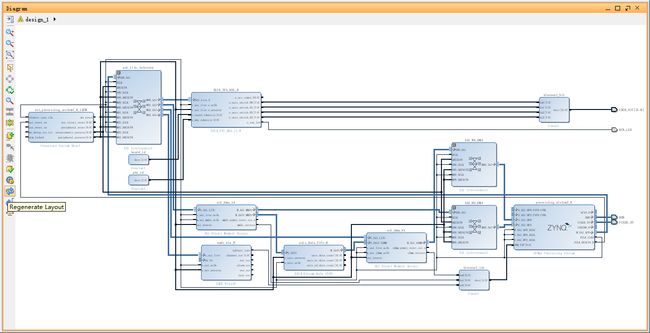

然后添加需要的IO口,最后连接好的效果如图18所示。

然后选择Address Editor对各个AXI外设的地址空间进行配置。对每个外设点右键,选择Assign Address,自动给外设分配地址控制。如图19所示。

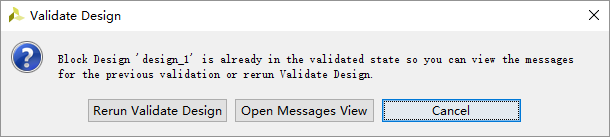

然后点击Validate Design对整个设计进行检查,如图20所示。如果出现异常,需要查找问题并进行修改,知道检查通过后才能进行下一步。

3.编译与综合

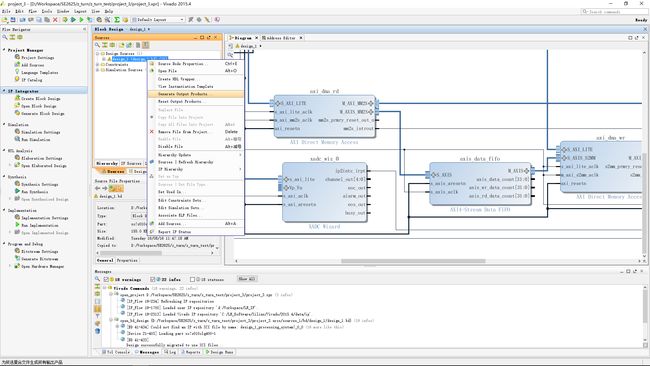

在Block Design下的Source窗口中,对上面新建的Block点右键,选择Generate Output Products...,生成各个IP的代码等文件,如图21所示。在弹出的窗口中,点击Generate。

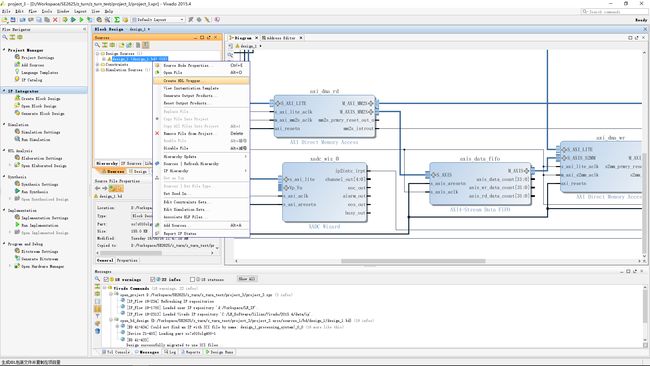

然后再对Block点右键,选择Create HDL Wrapper...,生成顶层模块,如图22所示。在弹出的窗口中,点击Let Vivado manage wrapper and auto-update。

在Block Design下的Source窗口中,选择Constraints,点右键选择Add Source...,如图23所示。选择Add or create constraints,新建一个约束文件。

然后在Flow Navigator中,选择Generate Bitstream,来进行编译和综合。如图24所示。