Vivado使用技巧(14):IO规划方法详解

本系列第13篇简单介绍了使用RTL工程IO布局工程两种方法定义IO Ports。在I/O Planning View Layout中(IO布局工程中是Default Layout),显示了FPGA器件资源、封装管脚、I/O Ports等详细信息。设计者借助这些信息来完成I/O规划。

创建单端/差分I/O Ports

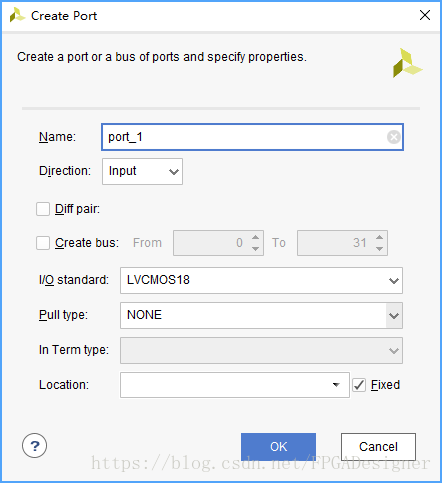

RTL工程会直接从RTL设计中获取I/O端口信息;IO布局工程可以从CSV/XDC文件中导入I/O端口信息,或者人工创建I/O端口(RTL工程不允许人工创建)。在I/O Ports窗口中右键->Create I/O Ports,弹出窗口:

设置端口名称、方向、是否是差分对、是否是总线、I/O标准、上下拉类型、端口位置等信息,当方向为Output时还可设置驱动强度和压摆率。

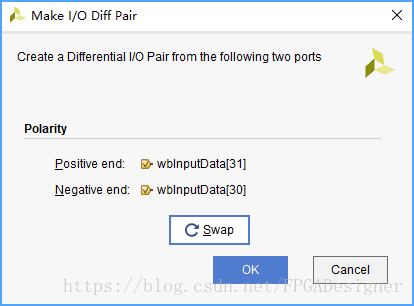

如果希望将I/O Ports窗口中已有的单端I/O组合为一对差分信号,选中两者,右键->Make Diff Pair:

点击Swap可以交换差分对的P端和N端。差分信号在I/O Ports窗口中只显示在一行里中(只会显示P端信号,N端信号显示在Neg Diff Pair属性栏中)。如过希望将一组差分信号拆成两个单端信号,右键->Split Diff Pair即可。上述功能只能在I/O规划工程中使用,不能在RTL工程中使用。

上述功能操作所对应的Tcl命令如下:

create_port port_1 -direction in #创建一个单端I/O

create_port port_2 -direction in -diff_pair #创建一个差分I/O

make_diff_pair_ports port_1 port_2 #组合一个差分对

split_diff_pair_ports port_1 port_2 #拆开一个差分对配置I/O Ports

Xilinx的FPGA器件支持可配置的SelectIO接口驱动器和接收器,支持多种标准接口。这些标准接口包含如下功能:可编程的输出强度和压摆率控制、使用DCI的片内端接、生成内部参考电压。

配置可以直接在I/O Ports窗口的属性列中进行,也可以点击右键->Configure Ports,在下面窗口中配置:

其中Pull type包括弱上拉PULLUP、弱下拉PULLDOWN和保持KEEPER和NONE四种,前两种让三态输出或双向端口在不被驱动时可以避免浮动,KEEPER可以让其保持当前的值。

每一个端口都有Fixed属性,表明该逻辑端口是由用户赋值的。端口必须保持锁定状态,才能避免生成比特流时不会发生错误。选中I/O端口,右键菜单中通过Fix Ports和Unfix Ports来切换端口状态。

RTL工程中,端口的方向只能从RTL源文件中获取,不能人工定义;在I/O规划工程中,需要人工定义I/O的方向。对于7系列、Zynq系列、UltraScale系列FPGA而言,所有I/O端口PACKAGE_PIN和IOSTANDARD属性必须有明确的值,否则不能生成bit流文件。

I/O Port接口的使用

Vivado提供了接口(Interface)用于管理有功能关系的一组I/O和总线。一组接口的属性可以同时赋值,减轻工作量,也有助于将接口隔离在某一时钟区域或PCB布线范围内。

在I/O Ports中选中所有需要组合在一起的信号,右键->Create I/O Port Interface,在新窗口中选中接口名称:

创建好的接口会按一定层次关系显示在I/O Ports窗口中:

添加其它I/O端口到接口中,选中I/O,右键->Assign to Interface,选中需要添加的接口即可;如果要从接口中移除某些I/O,右键->Unassign from Interface。

如果要删除某一接口,选中该接口右键->Delete或之间按键盘上的Delete按键,弹出如下窗口中,只选择接口点击OK即可。

Prohibit属性的使用

Vivado提供了Prohibit属性,设置了该属性的I/O管脚或I/O Bank会屏蔽掉端口布局。在Package Pin窗口中选中需要屏蔽的I/O,勾选中Prohibit:

在Device和Package窗口中相应的管脚会显示为带斜杠的圈:

上述功能操作所对应的示例Tcl命令如下:

set_property PROHIBIT 1 [get_sites U17] #屏蔽一个I/O的布局

set_property PROHIBIT 0 [get_sites U17] #解除屏蔽I/O Ports布局

如果已经提前知道了I/O端口和封装管脚之间的联系,直接在I/O Ports中填写即可。如果需要进行I/O Ports布局,Vivado提供了如下三种方法:

- 顺序布局:选中需要布局的I/O,右键->Place I/O Ports Sequentially,在Device窗口中依次点击,选择布局的位置,直到所有I/O全部布局完成。

- I/O Bank布局:选中需要布局的I/O,右键-> Place I/O Ports in an I/O Bank,在Device窗口中点击一个管脚位置,Vivado会尽可能的将I/O布局在该管脚所在的Bank中。如果还有I/O没有赋值,需要继续点击选择位置,直到所有I/O全部布局完成。

- 区域布局:选中需要布局的I/O,右键->Place I/O Ports in a Defined Area,箭头变为十字,在Device窗口中拖动一个矩形区域,Vivado会尽可能的将I/O布局在该区域中。如果还有I/O没有赋值,需要继续选择区域,直到所有I/O全部布局完成。

注意,所有布局方式所用的布局顺序都与端口在I/O Ports窗口中排列的顺序有关,如有需要应该在布局前先调整I/O在I/O Ports中的顺序。

除了人工布局外,Vivado还提供了自动布局功能。Vivado可以根据I/O标准和差分对规则,自动将I/O端口赋值到封装管脚上。在I/O Ports窗口中选择需要布局的I/O,在Tools菜单栏中点击I/O Planning->Auto-place I/O Ports:

选择布局全部I/O或仅布局选中I/O,点击下一步:

如果选中的I/O中有部分已经赋值,会出现如上窗口,选择保持原有赋值或寻找新的赋值位置,点击下一步,再点击Finish即可运行自动布局。接下来再介绍I/O布局过程中可能会用到的两个小操作:

- 交换布局位置:选中需要交换位置的两个I/O,右键->Swap Location;

- 移除已经完成的布局:选中需要删除布局的I/O,右键->Unplace;

I/O规划工程迁移为RTL工程

已经完成的I/O规划工程可以直接迁移为RTL工程,端口定义会用于创建RTL设计中的顶层模块(该过程不可逆,RTL工程不可迁回I/O规划工程)。在File菜单或Flow Navigator中点击Migrate to RTL:

Top RTL file设置顶层模块文件;Netlist format选中Verilog或VHDL;选中write diff buffers会将差分对缓存器保留在顶层模块定义中。点击OK迁移完成后,即可以RTL工程为基础完成FPGA设计,工程中有一个包含I/O约束的XDC文件。