- VIVADO导出仿真数据到MATLAB中进行分析

FPGA与信号处理

FPGA学习记录VIVADOSIMULATION导出仿真数据TXTMATLAB

VIVADO导出仿真数据到MATLAB中进行分析目录前言一、导出仿真数据需要编写的RTL代码二、MATLAB读入txt文件中的数据三、需要注意的点总结前言在使用XilinxVivado进行FPGA开发时,如何将RTL仿真生成的数据导出,进行进一步分析与可视化,是很多开发者常遇到的问题。Vivado自带仿真工具不支持直接导出仿真数据,但是我们可以通过编写一段简单的RTL代码即可将需要的仿真数据保存到

- [Labtoolstcl 44-513] HW Target shutdown. Closing target: localhost:3121/xilinx_tcf/Digilent/21025113

hahaha6016

硬件设计fpga开发

然后之后每次进行代码编译,综合,执行之后,就会提示error。工具有问题,将vivado工具关闭,重新打开,然后再打开工程,重新编译。

- FPGA基础 -- Verilog 禁止语句

关于Verilog中“禁止语句”的详细培训讲解**,结合可综合设计与仿真行为的角度,深入讲解Verilog中的“禁止类语句”(即综合时应避免或仅用于仿真的语句):一、Verilog中的“禁止语句”概念所谓“禁止语句”(或说非综合语句),是指不能被综合工具(如Vivado、Quartus、Synplify)综合到门级电路中,仅用于仿真或调试目的的语法结构。使用这些语句不会被转换为实际的逻辑门或触发器

- ZYNQ笔记(二十):Clocking Wizard 动态配置

W以至千里

ZYNQ笔记fpga开发

版本:Vivado2020.2(Vitis)任务:ZYNQPS端通过AXI4Lite接口配置ClockingWizardIP核输出时钟频率目录一、介绍二、寄存器定义三、配置四、PS端代码一、介绍Xilinx的ClockWizardIP核用于在FPGA中生成和管理时钟信号。它支持动态重配置(DynamicReconfiguration),允许在运行时通过AXI4-Lite接口或DRP接口(这两个接口

- 实验一:数据选择器实验

俺不是西瓜太郎´•ﻌ•`

实验报告fpga开发

实验一数据选择器实验报告目录实验目的实验内容原理描述VerilogHDL设计源代码Testbench仿真代码及仿真结果XDC文件配置下板测试实验体会实验照片实验目的熟悉使用VerilogHDL的三种不同描述方式进行基本逻辑电路建模,实现数据扩展。学习使用Vivado进行逻辑设计的基本流程。学习使用Nexys4FPGA硬件开发板,了解开发板主要的外围接口。了解设计源代码与仿真代码的区别。实验内容原理

- USB转JTAG、USB转I2C、USB转SPI、USB转RS121/RS422/RS485芯片调试笔记

vx:module1066

信号处理模块笔记

1.1测试环境1.1.1整体环境介绍测试环境说明板卡:pcie403板卡主控芯片:Xilinxxcvu13p-fhgb2104-2调试软件:Vivado2018.3代码环境:Vscodeutf-8测试工程:pcie403_user_top1.1.2硬件介绍UDPCIe-403使用VU13P+ZYNQ+FMC插槽架构,对外数据接口使用PCIe3.0x16和PCIe4.0x8进行数据通信或传输,支持千

- 通过vivado HLS设计一个FIR低通滤波器

fpga和matlab

VivadoHLS开发vivadoHLSFIR低通滤波器

目录1.FIR参数确定2.FIR系数计算3.C/C++代码实现4.VivadoHLS项目创建与配置4.1在VivadoHLS中创建新项目并配置4.2在VivadoHLS中执行C仿真4.3执行C综合以将C代码转换为RTL4.4进行RTL级仿真验证4.5导出IP4.6在Vivado中集成IPVivadoHLS是一款强大的高层次综合工具,可将C/C++代码转换为硬件描述语言(HDL),显著提升FPGA开

- vivadoHLS优化

ailao4622

//HLS数据类型:ap_fixed--------------------------------------------------------------------------(优化)Directive(函数/类->变量/对象)InsertDirective(优化措施ug902->designoptimization)Directive:DATA_PACK对结构体打包:INTERFACE对

- 【FPGA教程案例2】基于vivado核的NCO正弦余弦发生器设计与实现

fpga和matlab

★教程2:fpga入门100例NCODDSFPGA教程

FPGA教程目录MATLAB教程目录---------------------------------------------------------------------------------------本课程成果预览目录1.软件版本2.本算法理论知识3.核心代码4.操作步骤与仿真结论5.参考文献1.软件版本vivado2019.22.本算法理论知识在通信系统中,

- Vivado程序固化到Flash

白码王子小张

Vivado工具使用XilinxvivadoFPGA

在上板调试FPGA时,通常使用JTAG接口下载程序到FPGA芯片中,FPGA本身是基于RAM工艺的器件,因此掉电后会丢失芯片内的程序,需要重新烧写程序。但是当程序需要投入使用时不能每一次都使用JTAG接口下载程序,一般FPGA的外围会有非易失性存储器:Flash或SD卡等,可以将程序加载进去,这样下次上电后可以直接从该存储器中读取程序并启动配置。在使用Vivado固化程序时,通常有两种文件格式可以

- vivado ROM ip核的使用

明天冰雪封山

fpgaip核fpga开发

ROM介绍ROM代表只读存储器(Read-OnlyMemory),是一种电子存储设备,用于存储计算机系统启动程序、固件、操作系统和其他重要数据,比如说电脑中使用的磁盘。与随机存储器(RAM)不同,ROM存储的数据一旦写入后断电后不会丢失,RAM断电后数据直接丢失,因此ROM也被称为非易失性存储器(Non-VolatileMemory)。FPGA中是有一定的存储资源,常见就是BRAM,本实验通过调用

- 小白入门FPGA设计,如何快速学习?

IC与FPGA设计

FPGAfpga开发学习

很多刚入门的小伙伴,初次听说FPGA(现场可编程门阵列),脑子里只有一个字:玄!什么“时序逻辑”“Verilog”“Vivado”,仿佛一夜之间掉进了电子黑魔法的深坑。但真相是——FPGA,其实没有你想得那么难。只是你需要一套适合小白体质的学习方法,走对第一步,就能少走很多弯路。今天这篇文章,就带你从零出发,搞懂:小白怎么系统学习FPGA?有哪些推荐路径?最容易卡住的坑怎么避?一、FPGA是啥?能

- Vivado仿真波形不显示怎么解决?

Dreamboat_Soc

fpga

求助各位大佬,在使用vivado仿真测试时,部分信号有数据,但是无法显示具体波形,只有几个点(如下图所示),请问一下是什么原因、该如何解决?

- UDP--DDR--SFP,FPGA实现之ddr axi读写驱动模块

爱学习的张哥

udpfpga开发ddrAXI网络协议

ddraxi读写驱动模块实现介绍该模块主要功能为:接收数据读写op指令,将其转换为AXI4总线形式其逻辑较为简单,而关于AXI4的时序,建议读者使用vivado封装两个AXI4的ip核,一个主机,一个从机,进行学习,笔者在这里便不进行赘述,如果有读者想要了解,欢迎在评论区进行讨论,笔者后期可能会进行文章专栏讲解。其工作原理即是,检测到op指令有效,进行相应的读写操作,AXI4读写数据的流程是AXI

- AMD Vivado™ 设计套件生成加密比特流和加密密钥

芯眼

FPGAfpga开发集成测试算法软件工程

概括重要提示:有关使用AMDVivado™DesignSuite2016.4及更早版本进行eFUSE编程的重要更新,请参阅AMD设计咨询68832。本应用说明介绍了使用AMDVivado™设计套件生成加密比特流和加密密钥(高级加密标准伽罗瓦/计数器模式(AES-GCM)和RSA身份验证)的简单分步过程。其中还介绍了使用Vivado设计套件将高级加密标准全球移动通信系统(AES-GSM)加密密钥和R

- 2023 ASIC FPGA IP RTL & License (Diamond / Libero SOC)

Jerry_Wei_2020

fpga开发

FPGA系列:IntelAlteraFPGA(Quartus)ADMXILINXFPGA(Vivado&ISE)LatticeFPGA(Diamond)Microchip(LiberoSOC)ASIC系列:SynopsysIPARMIPCadenceIP等等QQ:3339377509

- Vivado中可新建的工程类型解析

漂洋过海的鱼儿

Vivadofpga开发

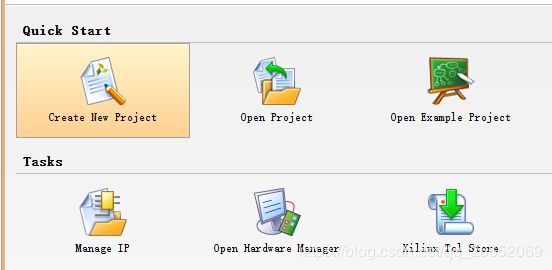

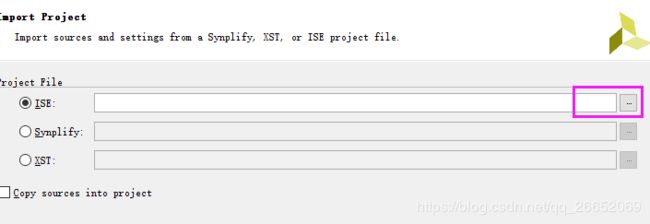

以下是Vivado中可新建的工程类型解析,按用途和场景分类说明:1.RTLProject(RTL工程)用途:从零开始基于RTL代码(Verilog/VHDL)设计FPGA逻辑,覆盖完整开发流程。适用阶段:设计初期(代码编写、IP集成、仿真、综合、实现)。核心功能:添加RTL代码、约束文件、IP核。运行RTL分析(检查语法和层次结构)。综合生成网表(Netlist)。实现布局布线(Place&Rou

- FPGA:Xilinx Kintex 7实现DDR3 SDRAM读写

InnoLink_1024

FPGA高速接口RTL设计fpga开发硬件架构硬件工程

在XilinxKintex7系列FPGA上实现对DDR3SDRAM的读写,主要依赖Xilinx提供的MemoryInterfaceGenerator(MIG)IP核,结合Vivado设计流程。以下是详细步骤和关键点:1.准备工作硬件需求:Kintex-7FPGA(如XC7K325T)。DDR3SDRAM芯片,符合JESD79-3标准(如MicronMT41J256M16)。开发板(如KC705)或

- FPGA: Xilinx Kintex 7实现PCIe接口

InnoLink_1024

高速接口FPGARTL设计fpga开发硬件架构硬件工程

在XilinxKintex-7系列FPGA上实现PCIe(PeripheralComponentInterconnectExpress)接口,通常使用Xilinx提供的7SeriesIntegratedBlockforPCIeIP核,结合Vivado设计流程。以下是实现PCIe接口的详细步骤和关键点,适用于Kintex-7FPGA(如XC7K325T)。1.准备工作硬件需求:Kintex-7FPG

- vivado的license

Dr-加菲

vivado

INCREMENTVIVADO_HLSxilinxd2037.05permanentuncountedAF3E86892AA2VENDOR_STRING=License_Type:BoughtHOSTID=ANYISSUER=“XilinxInc”START=19-May-2016TS_OKINCREMENTVivado_System_Editionxilinxd2037.05permanentu

- artix 7 FPGA上电启动速度慢的解决办法

我是苹果,不是香蕉

fpga

解决方法:上电启动速度慢是因为FPGA生成的bit文件采用1-wire形式读取FLAS固件。打开VIVADO,点击opensynthesizedDesign:第二步,右击Generatebitstream,点击bitstreamsettings点击configureadditionalbitstreamsettings,在里面选择spix4

- 学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (十二)Verilog程序设计举例 | 2023.11.6/星期一/天气晴

杨肉师傅

学习XilinxZYNQFPGA开发学习fpga开发

系列文章目录专栏系列文章:学习XilinxZYNQFPGA开发文章目录系列文章目录摘要一、设计思路二、创建Verilog源文件三、编写Verilog源程序或门模块my_or2.v半加器模块h_adder.v全加器模块f_adder.v四、仿真五、查看RTL分析摘要在上一次的学习内容《Vivado建立工程》的基础上,我已经有一个工程了,现在以1位全加器的设计过程来举例说明VerilogHDL程序的设

- 62_ZYNQ7020开发板_SD/QSPI实现Vivado的PL端程序和SDK程序同时运行

一米八零的昊哥

ZYNQ嵌入式系统1

1)双击用vivado打开黑金7020自带的linux_base工程2)查看vivado顶层文件design_1_wrapper.v文件//Copyright1986-2017Xilinx,Inc.AllRightsReserved.//--------------------------------------------------------------------------------/

- ZYNQ使用petalinux方式移植linux

工匠Sola

linux嵌入式硬件fpga开发

一、安装petalinux.安装虚拟机,在虚拟机里安装linux系统(ubuntu16.04.7LTS)虚拟机里磁盘尽量留大点,建议60G。建议安装VMwareTools,Win11用户建议安装VMware17.5,不然启动虚拟机可能遇到蓝屏问题。开发工具:vivado2017.1(Windows11下)+petalinux2017.1(Linux下)更新apt-getsudoapt-getupd

- ZYNQ 基于OCM实现AMP双核petalinux开发流程

寒听雪落

fpga开发linux

一,基本开发流程1,软件平台:Windows64位环境下,Vivado2017.04版本+SDK2017.04版本,Linux环境下(Ubuntu16.04),Petalinux2017.04版本,ZYNQ7z10clg400-12,AMP模式:从软件的角度来看,多核处理器的运行模式有三种:(1)AMP(非对称多进程):多个核心相对独立的运行不同的任务,每个核心可能运行不同的操作系统或裸机程序,但

- Vivado 的XDC设置输出延时

BinaryStarXin

FPGA技术汇总分享网络fpga开发数据库

Vivado的XDC设置输出延时Q1Vivado的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。设置输出时钟时,参考时钟选择相移的那个,发现不起作用,没有路径。如果选择系统时钟,分析后是系统时钟的最大最小延时,没有相位移动后的信息,这是什么问题?伴随时钟创建的Create_generated_clock中的Set_out

- xilinx 芯片使用vivado导出pindelay文件——FPGA学习笔记24

无尽的苍穹

FPGA学习笔记fpga开发

1、创建一个空的工程2、在TCL命令窗输入link_design-partxc7a35tfgg484-2(芯片型号)回车3、输入write_csvxc7a35tfgg484-2(文件类型和文件名字)回车,导出文件在该目录下4、导出文件

- FPGA车牌识别

超能力MAX

fpga开发

基于FPGA的车牌识别主要包含以下几个步骤:图像采集、颜色空间转换、边缘检测、形态学处理(腐蚀和膨胀)、特征值提取、模板匹配、结果显示。先用matlab对原理进行仿真,后用vivado和modelsim进行设计和仿真。一、1.图像采集采用ov5640摄像头使用I2C协议对其进行驱动从而实时捕获数据2.数据通过DDR3进行缓存,并使用fifo进行乒乓缓存3.采用XC7A100T开发板进行数字图像处理

- 24小时FPGA数字时钟设计与实现

西域情歌

本文还有配套的精品资源,点击获取简介:本项目利用FPGA技术创建了一个24小时制的数字时钟硬件电路。通过使用XilinxVivado2019.1工具和NEXYS4开发板,展示了从Verilog或VHDL代码编写到时钟逻辑在FPGA上的实现过程。时钟系统包含计数器和解码逻辑,以控制LED或LCD显示时间。这个项目对于学习数字逻辑设计和FPGA编程是极佳的实践材料。1.FPGA技术在数字时钟设计中的应

- [FPGA基础] AXIS篇

S&Z3463

FPGA基础fpga开发

XilinxFPGAAXI4-Stream使用文档1.概述AXI4-Stream(AdvancedeXtensibleInterface4Stream)是ARM公司AMBA协议中的一种面向流式数据传输的协议,广泛应用于XilinxFPGA中,用于视频、音频、DMA数据流等连续数据处理场景。本文档详细介绍AXI4-Stream协议的使用,涵盖协议概述、信号描述、设计流程、Vivado相关IP核及示例

- java类加载顺序

3213213333332132

java

package com.demo;

/**

* @Description 类加载顺序

* @author FuJianyong

* 2015-2-6上午11:21:37

*/

public class ClassLoaderSequence {

String s1 = "成员属性";

static String s2 = "

- Hibernate与mybitas的比较

BlueSkator

sqlHibernate框架ibatisorm

第一章 Hibernate与MyBatis

Hibernate 是当前最流行的O/R mapping框架,它出身于sf.net,现在已经成为Jboss的一部分。 Mybatis 是另外一种优秀的O/R mapping框架。目前属于apache的一个子项目。

MyBatis 参考资料官网:http:

- php多维数组排序以及实际工作中的应用

dcj3sjt126com

PHPusortuasort

自定义排序函数返回false或负数意味着第一个参数应该排在第二个参数的前面, 正数或true反之, 0相等usort不保存键名uasort 键名会保存下来uksort 排序是对键名进行的

<!doctype html>

<html lang="en">

<head>

<meta charset="utf-8&q

- DOM改变字体大小

周华华

前端

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/xhtml&q

- c3p0的配置

g21121

c3p0

c3p0是一个开源的JDBC连接池,它实现了数据源和JNDI绑定,支持JDBC3规范和JDBC2的标准扩展。c3p0的下载地址是:http://sourceforge.net/projects/c3p0/这里可以下载到c3p0最新版本。

以在spring中配置dataSource为例:

<!-- spring加载资源文件 -->

<bean name="prope

- Java获取工程路径的几种方法

510888780

java

第一种:

File f = new File(this.getClass().getResource("/").getPath());

System.out.println(f);

结果:

C:\Documents%20and%20Settings\Administrator\workspace\projectName\bin

获取当前类的所在工程路径;

如果不加“

- 在类Unix系统下实现SSH免密码登录服务器

Harry642

免密ssh

1.客户机

(1)执行ssh-keygen -t rsa -C "

[email protected]"生成公钥,xxx为自定义大email地址

(2)执行scp ~/.ssh/id_rsa.pub root@xxxxxxxxx:/tmp将公钥拷贝到服务器上,xxx为服务器地址

(3)执行cat

- Java新手入门的30个基本概念一

aijuans

javajava 入门新手

在我们学习Java的过程中,掌握其中的基本概念对我们的学习无论是J2SE,J2EE,J2ME都是很重要的,J2SE是Java的基础,所以有必要对其中的基本概念做以归纳,以便大家在以后的学习过程中更好的理解java的精髓,在此我总结了30条基本的概念。 Java概述: 目前Java主要应用于中间件的开发(middleware)---处理客户机于服务器之间的通信技术,早期的实践证明,Java不适合

- Memcached for windows 简单介绍

antlove

javaWebwindowscachememcached

1. 安装memcached server

a. 下载memcached-1.2.6-win32-bin.zip

b. 解压缩,dos 窗口切换到 memcached.exe所在目录,运行memcached.exe -d install

c.启动memcached Server,直接在dos窗口键入 net start "memcached Server&quo

- 数据库对象的视图和索引

百合不是茶

索引oeacle数据库视图

视图

视图是从一个表或视图导出的表,也可以是从多个表或视图导出的表。视图是一个虚表,数据库不对视图所对应的数据进行实际存储,只存储视图的定义,对视图的数据进行操作时,只能将字段定义为视图,不能将具体的数据定义为视图

为什么oracle需要视图;

&

- Mockito(一) --入门篇

bijian1013

持续集成mockito单元测试

Mockito是一个针对Java的mocking框架,它与EasyMock和jMock很相似,但是通过在执行后校验什么已经被调用,它消除了对期望 行为(expectations)的需要。其它的mocking库需要你在执行前记录期望行为(expectations),而这导致了丑陋的初始化代码。

&nb

- 精通Oracle10编程SQL(5)SQL函数

bijian1013

oracle数据库plsql

/*

* SQL函数

*/

--数字函数

--ABS(n):返回数字n的绝对值

declare

v_abs number(6,2);

begin

v_abs:=abs(&no);

dbms_output.put_line('绝对值:'||v_abs);

end;

--ACOS(n):返回数字n的反余弦值,输入值的范围是-1~1,输出值的单位为弧度

- 【Log4j一】Log4j总体介绍

bit1129

log4j

Log4j组件:Logger、Appender、Layout

Log4j核心包含三个组件:logger、appender和layout。这三个组件协作提供日志功能:

日志的输出目标

日志的输出格式

日志的输出级别(是否抑制日志的输出)

logger继承特性

A logger is said to be an ancestor of anothe

- Java IO笔记

白糖_

java

public static void main(String[] args) throws IOException {

//输入流

InputStream in = Test.class.getResourceAsStream("/test");

InputStreamReader isr = new InputStreamReader(in);

Bu

- Docker 监控

ronin47

docker监控

目前项目内部署了docker,于是涉及到关于监控的事情,参考一些经典实例以及一些自己的想法,总结一下思路。 1、关于监控的内容 监控宿主机本身

监控宿主机本身还是比较简单的,同其他服务器监控类似,对cpu、network、io、disk等做通用的检查,这里不再细说。

额外的,因为是docker的

- java-顺时针打印图形

bylijinnan

java

一个画图程序 要求打印出:

1.int i=5;

2.1 2 3 4 5

3.16 17 18 19 6

4.15 24 25 20 7

5.14 23 22 21 8

6.13 12 11 10 9

7.

8.int i=6

9.1 2 3 4 5 6

10.20 21 22 23 24 7

11.19

- 关于iReport汉化版强制使用英文的配置方法

Kai_Ge

iReport汉化英文版

对于那些具有强迫症的工程师来说,软件汉化固然好用,但是汉化不完整却极为头疼,本方法针对iReport汉化不完整的情况,强制使用英文版,方法如下:

在 iReport 安装路径下的 etc/ireport.conf 里增加红色部分启动参数,即可变为英文版。

# ${HOME} will be replaced by user home directory accordin

- [并行计算]论宇宙的可计算性

comsci

并行计算

现在我们知道,一个涡旋系统具有并行计算能力.按照自然运动理论,这个系统也同时具有存储能力,同时具备计算和存储能力的系统,在某种条件下一般都会产生意识......

那么,这种概念让我们推论出一个结论

&nb

- 用OpenGL实现无限循环的coverflow

dai_lm

androidcoverflow

网上找了很久,都是用Gallery实现的,效果不是很满意,结果发现这个用OpenGL实现的,稍微修改了一下源码,实现了无限循环功能

源码地址:

https://github.com/jackfengji/glcoverflow

public class CoverFlowOpenGL extends GLSurfaceView implements

GLSurfaceV

- JAVA数据计算的几个解决方案1

datamachine

javaHibernate计算

老大丢过来的软件跑了10天,摸到点门道,正好跟以前攒的私房有关联,整理存档。

-----------------------------华丽的分割线-------------------------------------

数据计算层是指介于数据存储和应用程序之间,负责计算数据存储层的数据,并将计算结果返回应用程序的层次。J

&nbs

- 简单的用户授权系统,利用给user表添加一个字段标识管理员的方式

dcj3sjt126com

yii

怎么创建一个简单的(非 RBAC)用户授权系统

通过查看论坛,我发现这是一个常见的问题,所以我决定写这篇文章。

本文只包括授权系统.假设你已经知道怎么创建身份验证系统(登录)。 数据库

首先在 user 表创建一个新的字段(integer 类型),字段名 'accessLevel',它定义了用户的访问权限 扩展 CWebUser 类

在配置文件(一般为 protecte

- 未选之路

dcj3sjt126com

诗

作者:罗伯特*费罗斯特

黄色的树林里分出两条路,

可惜我不能同时去涉足,

我在那路口久久伫立,

我向着一条路极目望去,

直到它消失在丛林深处.

但我却选了另外一条路,

它荒草萋萋,十分幽寂;

显得更诱人,更美丽,

虽然在这两条小路上,

都很少留下旅人的足迹.

那天清晨落叶满地,

两条路都未见脚印痕迹.

呵,留下一条路等改日再

- Java处理15位身份证变18位

蕃薯耀

18位身份证变15位15位身份证变18位身份证转换

15位身份证变18位,18位身份证变15位

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

蕃薯耀 201

- SpringMVC4零配置--应用上下文配置【AppConfig】

hanqunfeng

springmvc4

从spring3.0开始,Spring将JavaConfig整合到核心模块,普通的POJO只需要标注@Configuration注解,就可以成为spring配置类,并通过在方法上标注@Bean注解的方式注入bean。

Xml配置和Java类配置对比如下:

applicationContext-AppConfig.xml

<!-- 激活自动代理功能 参看:

- Android中webview跟JAVASCRIPT中的交互

jackyrong

JavaScripthtmlandroid脚本

在android的应用程序中,可以直接调用webview中的javascript代码,而webview中的javascript代码,也可以去调用ANDROID应用程序(也就是JAVA部分的代码).下面举例说明之:

1 JAVASCRIPT脚本调用android程序

要在webview中,调用addJavascriptInterface(OBJ,int

- 8个最佳Web开发资源推荐

lampcy

编程Web程序员

Web开发对程序员来说是一项较为复杂的工作,程序员需要快速地满足用户需求。如今很多的在线资源可以给程序员提供帮助,比如指导手册、在线课程和一些参考资料,而且这些资源基本都是免费和适合初学者的。无论你是需要选择一门新的编程语言,或是了解最新的标准,还是需要从其他地方找到一些灵感,我们这里为你整理了一些很好的Web开发资源,帮助你更成功地进行Web开发。

这里列出10个最佳Web开发资源,它们都是受

- 架构师之面试------jdk的hashMap实现

nannan408

HashMap

1.前言。

如题。

2.详述。

(1)hashMap算法就是数组链表。数组存放的元素是键值对。jdk通过移位算法(其实也就是简单的加乘算法),如下代码来生成数组下标(生成后indexFor一下就成下标了)。

static int hash(int h)

{

h ^= (h >>> 20) ^ (h >>>

- html禁止清除input文本输入缓存

Rainbow702

html缓存input输入框change

多数浏览器默认会缓存input的值,只有使用ctl+F5强制刷新的才可以清除缓存记录。

如果不想让浏览器缓存input的值,有2种方法:

方法一: 在不想使用缓存的input中添加 autocomplete="off";

<input type="text" autocomplete="off" n

- POJO和JavaBean的区别和联系

tjmljw

POJOjava beans

POJO 和JavaBean是我们常见的两个关键字,一般容易混淆,POJO全称是Plain Ordinary Java Object / Pure Old Java Object,中文可以翻译成:普通Java类,具有一部分getter/setter方法的那种类就可以称作POJO,但是JavaBean则比 POJO复杂很多, Java Bean 是可复用的组件,对 Java Bean 并没有严格的规

- java中单例的五种写法

liuxiaoling

java单例

/**

* 单例模式的五种写法:

* 1、懒汉

* 2、恶汉

* 3、静态内部类

* 4、枚举

* 5、双重校验锁

*/

/**

* 五、 双重校验锁,在当前的内存模型中无效

*/

class LockSingleton

{

private volatile static LockSingleton singleton;

pri