FPGA学习嵌入式硬件最小系统搭建(二)(RAM,system_id及PIO等)

FPGA学习嵌入式硬件最小系统搭建(二)(RAM,system_id及PIO等)

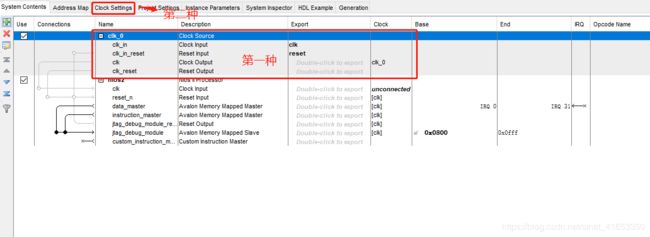

上篇NIOS处理器设置中未提到时钟设置,一般在定制个人的NIOS系统之前,需要配置系统时钟,因为开发板上的晶振是50MHz,输入给系统的时钟就是外部晶振的时钟频率,因此这里设置为50MHz。有两种设置方法。

由上图可知,第一种直接双击clk_0,修改系统时钟,第二种是点击clock settings,在这里修改系统时钟。

在上篇文章中已经详细描述了如何去定制nios ii处理器,本篇就直接从设置ROM和RAM说起,后期在点亮LCD1602液晶时,将会用SDRAM替代ROM。

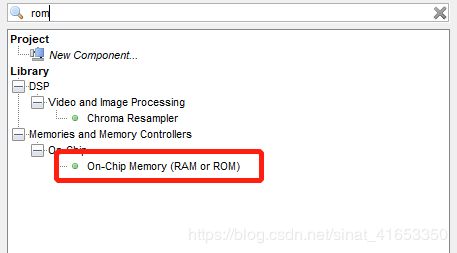

添加ROM及RAM存储器

直接搜索ROM,出现On-Chip Memory(RAM or ROM),如下图所示,因此得知RAM依然在这里添加。

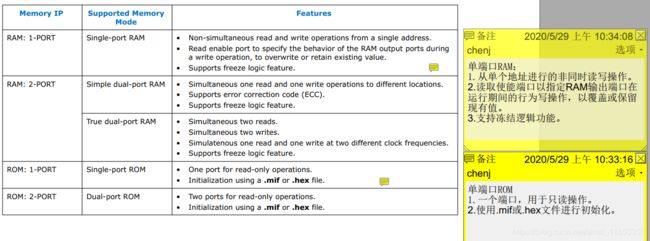

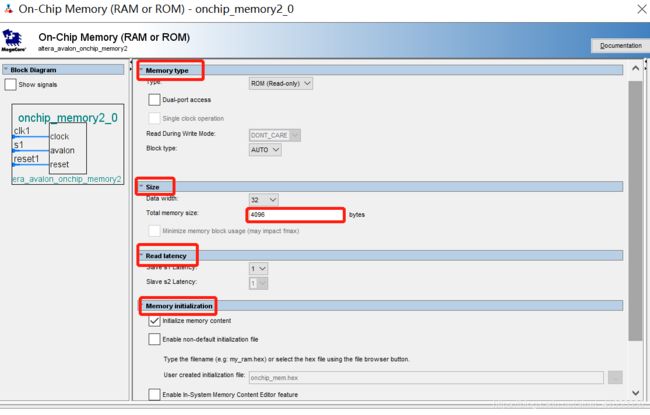

查找手册这个IP核支持多种ROM和ROM,这里选择单端口ROM,可知可以使用文件进行初始化

这里比之前的FPGA系统中IP核设置多了一个读取延迟设置,一般默认即可,由于器件资源丰富,因此这里选择单端口ROM和RAM时,默认即可,也可以选择初始化文件使能。

RAM设置同理,当我们设置好RAM和ROM时,下一步也可以添加JTAG_UART调试器IP,一般在建最小系统时,没有选择这一IP核。

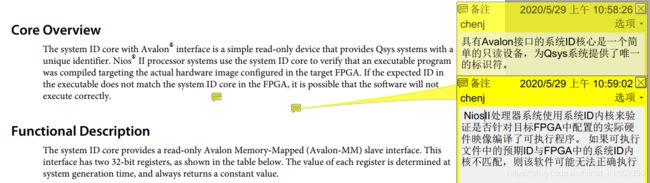

在定制NIOS II系统时,系统ID必不可少

查阅手册如下图所示,系统ID必不可少,因为需要为NIOS II系统提供了唯一的标识符,在连接CPU的时候会进行ID检测,如果系统ID不正确,则该NIOS II系统软件无法正常执行工作。

设置项如下,32位系统ID,可以自己设置定制NIOS II系统ID,也可以默认即可。

当把上述IP核添加到定制NIOS II系统中去后,下一步就可以定义我们的外设接口。

PIO核的重要性

这里我们需要先认识最重要的一个PIO核,PIO核功能如下:

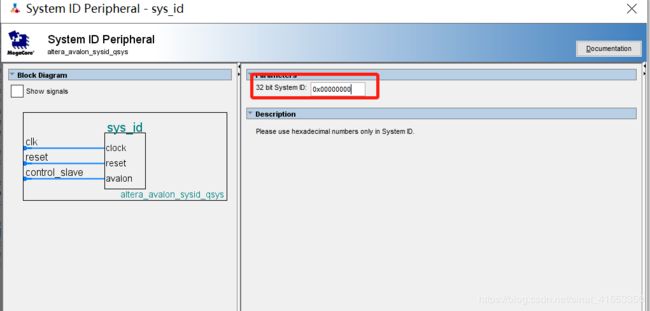

每个PIO内核最多可提供32个I / O端口。 诸如微处理器之类的主机通过读写寄存器映射的Avalon-MM接口来控制PIO端口。 在主机的控制下,PIO内核在其输入上捕获数据并将数据驱动到其输出。 当PIO端口直接连接到I / O引脚时,主机可以通过在PIO内核中写入控制寄存器来使引脚处于三态。 手册上展示了一个基于处理器的系统,该系统使用多个PIO内核来驱动LED,捕获片上复位请求控制逻辑的边沿并控制片外LCD显示器。

上图手册展示的系统,可以看出PIO可以控制片外LCD液晶显示,因为本期学习目标是点亮LCD液晶。

比如我个人定制一个最小系统,专门来驱动8080接口LCD液晶,那么PIO核起到怎样的角色呢?

这里涉及到Avalon-MM总线接口,因此这里下篇重点介绍LCD1602液晶IP核编写规范和最小系统中如何自定义8080接口LCD液晶IP核。

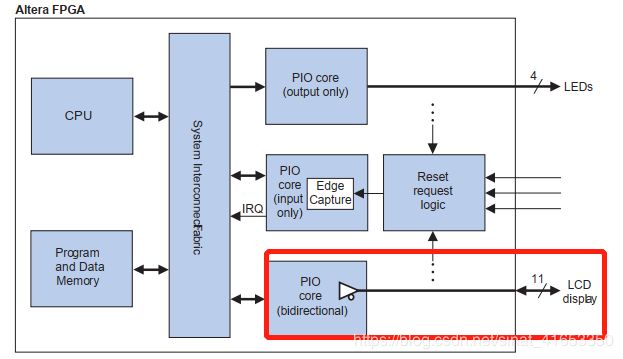

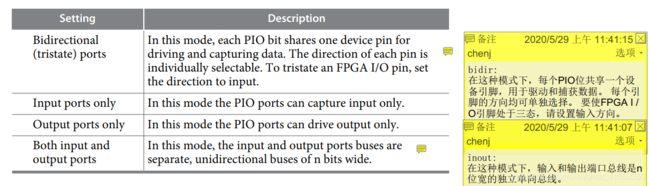

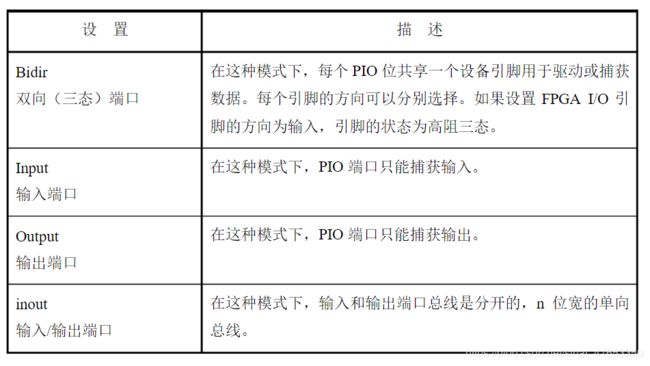

由上图看出PIO的基本设置中有几大IO类型,具体含义如下图所示,不同IO对应下面不同的设置项。

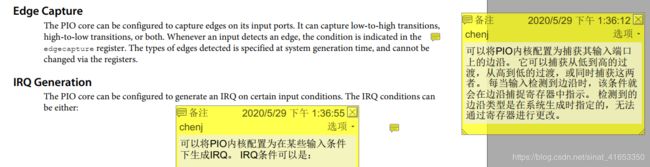

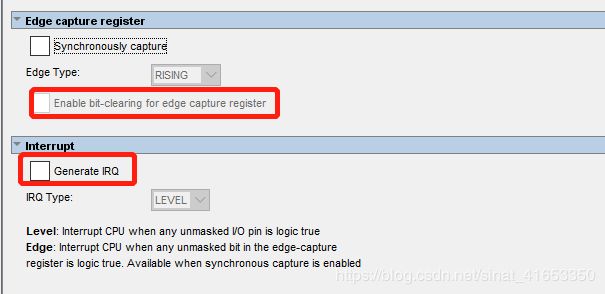

可知当PIO充当数据input时,可开启Edge capture register(边沿捕获)和interrupt(中断)设置。

【Edge capture register(边沿捕获)】

当 Synchronously capture(同步捕获)打开时, PIO 核包含边沿捕获寄存器Edge Capture。用户必须进一步指定边沿探测的类型:

Rising Edge(上升沿)

Falling Edge(下降沿)

ANY Edge(上升下降沿)

在输入端口,当一个指定类型的边沿出现时,边沿捕获寄存器允许核探测并且(可选)产生一个中断。

当 Synchronously capture(同步捕获)关闭时, Edge Capture寄存器不存在。

Enable Bit Clearing for Edge Capture Register(边沿捕获寄存器的使能位清除)

打开 Enable bit-clearing for edge capture register (边沿捕获寄存器的使能位清除),允许你单独清除一个或多个边沿捕获寄存器中的位。例如,为了清除边沿捕获寄存器的第六位,可以写01000000到寄存器。

【interrupt(中断)】

当输入端口上发生指定事件时,打开“生成IRQ(Generate IRQ)”以断言IRQ输出。 且必须进一步指定IRQ事件的原因:

•Level(级别)—每当特定输入为高电平且中断屏蔽寄存器中的该输入使能了中断时,内核都会产生IRQ。

•Edge(边沿)—每当边沿捕获寄存器中的特定位为高电平并为中断屏蔽寄存器中的该位使能中断时,内核就会生成IRQ。

当Generate IRQ关闭时,中断屏蔽寄存器不存在。

可知当PIO充当数据output时,可开启output register。

选项启用单个位设置/清除输出寄存器(Enable individual bit set/clear output register)选项允许您设置或清除输出端口的单个位。 启用此选项后,将实现两个额外的寄存器(起始寄存器和清除寄存器)。 您可以使用这些寄存器来指定要设置和清除的输出位。

上述将PIO核设置分成数据是输入还是输出来讲解配置项。(bidir和inout同理)。

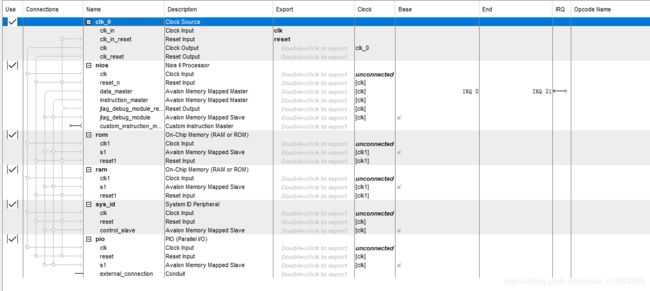

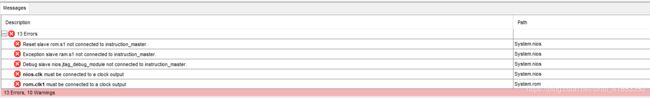

当将这些IP核添加如上图后,基本上简易的NIOS II系统就建立完成了,后期学习将会介绍这些接口模块线路如何连接及如何消除下图中的错误标识。

但下篇文件将会介绍组件库自带的LCD1602核及PIO核文件是怎样编写的和如何自定义封装自己的8080接口液晶IP核。