- 大厂高频面试题复习JAVA学习笔记-学习路线

addaduvyhup

java开发语言

对于应届生,要找到一份java工作,你得大概学会:java基础:javase、jvm、juc、gc、mysql、jdbc,计网计组Java微服务基础Maven→Gradle→Spring6→SpringMVC→MyBatis→MyBatisPlus→SSM->Redis7->SpringBoot2->SpringCloudjava微服务生态:Git-Docker-Elasticsearch→Zoo

- 企业级业务架构(EBA)设计方法论

数字化建设方案

数字化转型数据治理主数据数据仓库架构数据库运维

企业级业务架构(EBA)设计方法论企业级业务架构(EBA)设计方法论引言目的和背景业务架构定义与重要性设计方法论概述企业战略与业务架构关系企业战略制定过程业务架构对企业战略支撑作用战略导向下业务架构调整策略EBA设计原则与方法设计原则设计方法关键成功因素EBA核心组件设计组织架构设计流程体系设计信息系统架构设计数据治理与管理体系设计EBA实施落地策略实施步骤与计划制定变革管理与风险应对策略培训、宣

- 2019—06—18

xxxxxxxxxv

618别人疯狂购物的一天,我什么也没买…要攒钱去儿子的演唱会呀~祝大噶包括我都能财源广进呀!演唱会VIP说买就买!上床了,summarize~图片发自App❤️今天完成了什么呢?1、三大节专业课认真听讲2/3(下午的计组可能因为是最后一节新内容了,有一点点跑神,嘿嘿嘿…xinxuing2、课后整理笔记√着手复习X(还是英语听力占了一些时间,另外今天开始的也很晚…具体原因我就不明说了,还是那个金属疙

- ORP传感器

月明张速欧冀

传感器

ORP传感器1概述氧化还原电位,简称ORP(Oxidation-ReductionPotential)或Eh。ORP常用于指示环境介质(天然水、培养基、土壤等)的氧化性和还原性的相对程度。ORP的单位是mV。它由ORP复合电极和mV(毫伏)计组成。ORP复合电极由一种可以在其敏感层表面进行电子吸收或释放的电极,该敏感层是一种惰性金属,通常是用铂和金来制作,和参比电极(和pH电极一样的银/氯化银电极

- 【0101践行笔记】宝林+698字

盛夏光年_宝林

在一次主题营期间,尝试参加了设计组。在此之前,是没有接触过如何做好海报的。最多也只是学生时期,用PPT做的组员阳春海报。所以感谢@一点小贤组长,对我设计小白的点评与帮助。虽然只会基本的晚安图,但构图方面在10天内有了些进步。今天骚杰导师的分享-如何设计出让人尖叫的海报?让我对海报设计,有更全面的认识。希望,未来自己能够提升设计力,做好一张有质感的海报。审美力美,是一种生活方式。要多用眼睛看,多用心

- c++编程--对于程序的理解

天地过客1124

游戏开发c++

软件、程序的执行过程1.1编译器将写成的代码转成cpu指令,机器码---存储--》硬盘比如exe文件,存储的全是0和11.2对于exe一双击,就会读取到内存当中,然后所有cpu指令都在内存里了1.3CPU的作用:从内存中读取指令数据,解码,执行指令;CPU读写内存,控制其他设备干点事情1.4CPU之所以能控制,里面有三个比较重要的部分(计组)cpu通过寄存器进行信息存储,cpu通过运算器进行信息处

- 2021蓝桥杯省赛b题解

果汁大杯

蓝桥杯c++职场和发展

近几年蓝桥杯再也不是暴力杯了,但是可以很好的锻炼自己的代码水平,可以以赛促学,不要老看代码,比赛后时写代码速度也很重要!空间计组基础题:256MB=256*2^20*8位所以存放32位元素可以存放256*1024*1024*8/322.卡片#includeusing namespace std;const int maxn=2021;int car[10];int get(int x){retu

- 顺序表:数据结构的建筑积木

QuiteCoder

数据结构

朋友们大家好啊,本节内容我们进入数据结构的第二节,顺序表有关内容,同步我们会学习计组原理与cpp相关知识,求三连啊!本节我们重点探讨动态顺序表关于插入数据和删除数据的多种情况的分析顺序表线性表顺序表静态顺序表动态顺序表顺序表的初始化与销毁顺序表头部尾部的插入与删除指定位置插入和删除线性表线性表是数据结构的一种,它是一组具有相同数据类型的数据元素的有限序列。在线性表中,除了第一个和最后一个数据元素之

- 连载42《管理:使命、责任、实务(实务篇)》笔记

医管求索者

第42章组织的基本构成单位【对第42章总的理解】从关键活动去思考组织的基本构成单元是首要的任务。其次根据与产生成果的关系再把基本构成单位分类,不要按照技术类别划分,而是根据产出划分和合并。【对文章内容的理解】组织的基本构成单位首先来着关键活动在设计组织的基本构成单位是必须从想要得到的成果出发分析各种关键活动。注意是承担重任的部分。比如为了达到公司的目标,必须在哪个领域有出色的表现?哪些领域会影响企

- Vitis AI 集成

人工智能

更多TVM中文文档可访问→ApacheTVM是一个端到端的深度学习编译框架,适用于CPU、GPU和各种机器学习加速芯片。IApacheTVM中文站VitisAI是用在Xilinx平台(包括边缘设备和Alveo卡)上进行硬件加速AI推理的Xilinx开发堆栈。它由优化的IP、工具、库、模型和示例设计组成。在设计时兼顾高效率和易用性,充分发挥了XilinxFPGA和ACAP上AI加速的潜力。TVM中当

- 受益匪浅的一天

七月up

跟着审计组一个星期有两天。感觉还是静静的在学到一些东西,不同于书本之上的。在这里每天的环境就是跟账本打交道。你能看到各种各样的召集各种各样的凭证。自己本来不学这个。这次给了我一个,就有机会去大量的,密集的接触账本。你不懂了,带着一个问题大再去梳理查找知识点,这样既得既快又准确,而且还深刻。

- 算法(二)|深入浅出的讲解海明码的原理

DADONGOOO

计组算法

目录0.前言1.海明码的使用2.理解海明码需要明白的知识a.奇偶校检法b.异或运算3.海明码的原理a.海明码原理的概述b.多个校检位的设计c.校检位个数的计算d.海明码的总结4.举例a.计算校检码的个数b.计算每一位校检码并且与数据码组合c.数据传出,检错验错0.前言最近在学计组,碰到了海明码,但是书上数学语言有点晦涩难懂,而且并没有给出一部分细节的说明(比如为什么2^k-1>=n+k),去网上搜

- UI素材|最全面的移动端 UI KIT 模板

awayaya1

UI

什么是UI组件UI设计组件(UIKIT),直译过来就是用户界面成套元件,是界面设计常用控件或元件,「组」是设计元素的组合方式,「件」由不同的元件组成。组件的优势1、保证一致性Consistency与现实生活一致:与现实生活的流程、逻辑保持一致,遵循用户习惯的语言和概念;在界面中一致:所有的元素和结构需保持一致,比如:设计样式、图标和文本、元素的位置等。2、反馈用户Feedback控制反馈:通过界面

- Vitis AI 集成

HyperAI超神经

TVM人工智能TVM

更多TVM中文文档可访问→ApacheTVM是一个端到端的深度学习编译框架,适用于CPU、GPU和各种机器学习加速芯片。IApacheTVM中文站**VitisAI**是用在Xilinx平台(包括边缘设备和Alveo卡)上进行硬件加速AI推理的Xilinx开发堆栈。它由优化的IP、工具、库、模型和示例设计组成。在设计时兼顾高效率和易用性,充分发挥了XilinxFPGA和ACAP上AI加速的潜力。T

- 【软件设计师】——计组原理

栉风沐雪

软件设计师软件工程

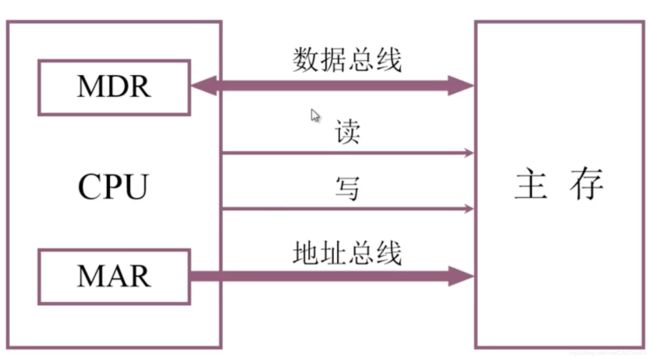

计算机系统硬件的基本组成计算机系统是由软件和硬件构成的。硬件系统由运算器、控制器、存储器、输入设备、输出设备五大部件组成。运算器、控制器等部件被集成在一起统称为中央处理单元CentralProcessingUnit。输入和输出设备合称为外部设备。存储器分为内部存储器和外部存储器,内部存储器速度高、容量小,一般用于临时存放程序、数据及中间结果,外部存储器速度慢、容量大,长期保存程序和数据。中央处理单

- 自己动手实现一个简单的 IOC,牛皮!!

java猫猫碎碎

我们将分为几步来编写简易IOC,首先设计组件,再设计接口,然后关注实现。1.设计组件。我们还记得Spring中最重要的有哪些组件吗?BeanFactory容器,BeanDefinitionBean的基本数据结构,当然还需要加载Bean的资源加载器。大概最后最重要的就是这几个组件。容器用来存放初始化好的Bean,BeanDefinition就是Bean的基本数据结构,比如Bean的名称,Bean的属

- 接口测试:自动化脚本

geobuins

自动化运维

接口测试:自动化脚本接口自动化脚本为什么要设计自动化脚本?后台程序更新/发布新版之前需要验证下之前的功能是否能用自动化脚本设计原则每个测试用例都是独立的测试用例都是可重复运行的测试数据与业务相分离(测试数据包括参数接口数据/测试执行所需要的系统数据)测试完成后,要删除不必要的测试数据。自动化脚本设计组件分析使用数据库连接池使用setUpThreadGroup线程组使用tearDownThreadG

- 汇编与接口技术期末复习笔记(1)—— 汇编部分

zyw2002

#汇编与接口技术汇编语言

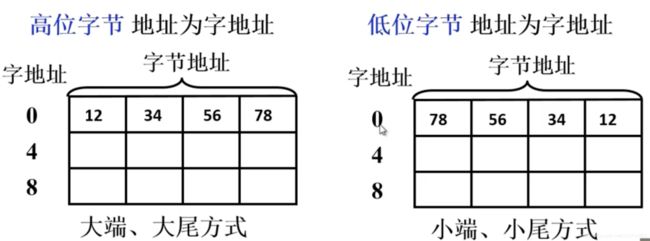

文章目录0.计组先导知识0.1进位计数制0.2计算机中数和字符的表示1.基础知识1.1汇编语言1.2硬件接口2.80x86计算机组织2.1计算机系统2.28086微处理器2.3存储器地址第1次作业3.地址与指令3.1寻址方式3.1.1数据寻址方式3.1.1.1立即数寻址3.1.1.2寄存器寻址3.1.1.3存贮器寻址直接寻址寄存器间接寻址寄存器相对寻址基址变址寻址相对基址变址寻址3.1.2指令寻址

- 计组学习笔记2024/2/5

Angus1648

学习笔记

记录每天学到了什么,同时在挪移图片过程中再次理解加深印象学计算机最重要的是理解,而不是整齐的笔记,不要主次搞混,所以以后记笔记的模式也要改一下(主要还是自己太菜,还达不到一边做到整齐笔记的同时还能够有时间做到理解,所以只能舍弃整齐时间保留理解时间)(不过如果有现成笔记的话能整齐就整齐,就比如数据库嘿嘿,因科制宜)1.2.3.1.这么多步,才完成第一条指令,通过0索引来找到22.PC的值是对应着MA

- 一起成长系列(50)

深圳的早晨

又一周过去了,因前一周只上了三天班,小伙伴们连带一起总结。有时我也想,每天都是这些工作,每周的周报如何汇报好?其实,虽然每天的工作大抵差不多,但是你是否能够在这差不多的工作中找到不一样呢?你是否有心得感想呢?审阅L洋学习工作周报,提出如下建议。1、标签版面牵涉项目部、设计组、供应商打版等,每一个环节出错都有可能影响最终出品的质量,因此在我们这个环节要认真做好核对及时反馈改进,并做好记录,督促相关人

- 检错编码——奇偶校验与循环冗余码CRC校验

bubb1e ly

计算机网络学习网络

奇偶校验奇偶校验是最简单的数据校验码,在计组时已经学过,它可以检测出一位数据出错或者奇数位数据出错,缺点就是不能确定出错的位置和不能检测出偶数位数据出错。但是在实际数据传输中,一位数据出错的概率比同时多位出错的概率要高,故而奇偶校验码的检错能力低,但还是在实际中广泛应用。一些概念:奇偶校验码:在若干有效信息数据位后面加上一位二进制位作为校验位,这样组成了奇偶校验码。码距:简单来说就是两个二进制数比

- 计组学习笔记2024/2/4

Angus1648

学习笔记

1.计算机的发展历程2.计算机硬件的基本组成存储器->就是内存.3.各个硬件的部件寄存器->用来存放二进制数据.各个硬件的工作原理视频留白,听完后边课程之后再来理解理解.冯诺依曼计算机的特点:1.计算机由五大部件组成2.指令和数据以同等地位存于存储器,可按地址寻访3.指令和数据用二进制表示4.指令由操作码和地址码和地址码组成5.存储程序6.以运算器为中心(现在一般以存储器为中心).4.计算机的层次

- Angular BaseView抽离页面公用属性

千寻物语

Angularangular.js前端

前言如果有一系列的页面布局很类似,为了节省时间,我们可以把这些类似的页面所通用的属性和方法抽离成一个BaseView,让其它页面继承该基础页面,同时将一些经常改变的属性和差异的属性写到配置文件里。例如树容器初始时是否展开、某些图表是否显示等都可以写到配置文件里面。本文将带你实现该功能,抽离出BaseView页面组件,鉴于json文件无法写注释的情况,配置文件采取yml的格式页面设计组件抽离Base

- Jellyfish进行Kmer评估基因组大小

吕强强学生信

我们对一个新物种进行基因组denovo测序时,一般需要先对该物种进行基因组survey,估计基因组大小、杂合率、重复序列比例、GC含量和倍性等信息,这些结果会直接影响我们后续测序的数据量及估计组装难度。公司一般会先用二代测个100x的数据量来做这一步,现在二代已经很便宜了,测50X和100X也差不了多少钱(当然也不是越多越好),但在测序之前,建议通过核型分析和流式等方法预估一下基因组大小是多少再安

- 【计算机网络-网络层】变长子网划分问题的二叉树解法

Mount256

#计算机网络考研计算机网络子网划分

计网的变长子网划分、计组的变长操作码划分、数据结构的哈夫曼编码,都是前缀编码的本质。【二叉树解法】每条从叶结点到根节点的路径上有且只有一个被分配的结点:【例】现将一个IP网络划分成4个子网,若其中一个子网是172.16.1.128/26,则下列网络中,不可能是另外三个子网之一的是()。A.172.16.1.0/25B.172.16.1.64/26C.172.16.1.96/27D.172.16.1

- 【2023地理设计组一等奖】基于机器学习的地下水仿真与时空分析

sky J

案例分享机器学习机器人人工智能

作品介绍1设计思想1.1作品背景华北平原是我国最重要的粮棉产地之一,然而近年来农业的低效用水以及过度压采正逐步加剧其地下水资源的紧张性,为经济可持续发展带来重大风险。而地下水动态变化与人为干预、全球气候波动呈现出高度相关性,因此,地下水的仿真模拟对保障粮食供应和推动水资源的可持续管理至关重要。目前学界尽管有大量的文献探讨地下水的时空分布及可持续性发展,但与现实需求相比,其在空间分辨率和多因子影响的

- 【2023地理设计组一等奖】基于GIS的桥梁隧道三维建模与可视化

sky J

案例分享人工智能

作品介绍1设计背景和意义随着我国基础建设规模不断扩大和深入,构建桥梁可视化管理模型,全面推动智慧桥梁,已成为现代隧道桥梁建设行业的发展趋势。传统的桥梁建模工作需要复杂的算法设计并需要熟练编程实践技能,实现周期长。开发自主知识版权的桥梁建模软件系统或专用插件是桥梁、隧道可视化的重要技术趋势。图1研究区域概况图本项目以湖北省恩施土家族苗族自治州的四渡河大桥为例,通过大桥测量数据、和数字高程模型等多源数

- 【2023地理设计组一等奖】多模态地理空间数据支持下的城市洪涝灾害韧性评价

sky J

案例分享人工智能

作品介绍1作品背景近几年,城市化进程的加快和全球气候变暖导致气候系统不稳定,极端天气事件的发生频率逐渐上升[1]。据统计,洪涝灾害是最常见、最广泛和最具破坏性的自然灾害之一[2]。2021年7月,河南地区发生历史罕见特大暴雨,造成严重的洪涝灾害,而在2023年7月,强降雨导致河北地区遭受洪涝灾害。在洪涝灾害日益严峻的情况下,对洪涝灾害的研究是提升城市韧性的基础[3,4]。城市洪涝灾害韧性是指城市系

- 高宇辰:打造“π”型人才 | 提升之路系列(七)

数据派THU

导读为了发挥清华大学多学科优势,搭建跨学科交叉融合平台,创新跨学科交叉培养模式,培养具有大数据思维和应用创新的“π”型人才,由清华大学研究生院、清华大学大数据研究中心及相关院系共同设计组织的“清华大学大数据能力提升项目”开始实施并深受校内师生的认可。项目通过整合建设课程模块,形成了大数据思维与技能、跨界学习、实操应用相结合的大数据课程体系和线上线下混合式教学模式,显著提升了学生大数据分析能力和创新

- 【剽悍读书营成长记录】做到,才能看到

开心大果子

每一次的结束都是更好的开始。在读书营,五次结束,五次开始,我遇见了做到的自己。2018初入读书营,很长一段时间都是焦虑,非常焦虑的状态,现在想来为什么会焦虑,其实都是自己想的太多做的太少。成为了一个思想的畅行者,行动上的残疾人。我开始想,不行啊,我交钱不是来混日子的啊,得干点啥。图片发自App在焦虑过后,慢慢的找到了事儿做,是在加入设计组、活动组开始,也就是在第三次主题营那时候开始的。从那时候我泡

- 用MiddleGenIDE工具生成hibernate的POJO(根据数据表生成POJO类)

AdyZhang

POJOeclipseHibernateMiddleGenIDE

推荐:MiddlegenIDE插件, 是一个Eclipse 插件. 用它可以直接连接到数据库, 根据表按照一定的HIBERNATE规则作出BEAN和对应的XML ,用完后你可以手动删除它加载的JAR包和XML文件! 今天开始试着使用

- .9.png

Cb123456

android

“点九”是andriod平台的应用软件开发里的一种特殊的图片形式,文件扩展名为:.9.png

智能手机中有自动横屏的功能,同一幅界面会在随着手机(或平板电脑)中的方向传感器的参数不同而改变显示的方向,在界面改变方向后,界面上的图形会因为长宽的变化而产生拉伸,造成图形的失真变形。

我们都知道android平台有多种不同的分辨率,很多控件的切图文件在被放大拉伸后,边

- 算法的效率

天子之骄

算法效率复杂度最坏情况运行时间大O阶平均情况运行时间

算法的效率

效率是速度和空间消耗的度量。集中考虑程序的速度,也称运行时间或执行时间,用复杂度的阶(O)这一标准来衡量。空间的消耗或需求也可以用大O表示,而且它总是小于或等于时间需求。

以下是我的学习笔记:

1.求值与霍纳法则,即为秦九韶公式。

2.测定运行时间的最可靠方法是计数对运行时间有贡献的基本操作的执行次数。运行时间与这个计数成正比。

- java数据结构

何必如此

java数据结构

Java 数据结构

Java工具包提供了强大的数据结构。在Java中的数据结构主要包括以下几种接口和类:

枚举(Enumeration)

位集合(BitSet)

向量(Vector)

栈(Stack)

字典(Dictionary)

哈希表(Hashtable)

属性(Properties)

以上这些类是传统遗留的,在Java2中引入了一种新的框架-集合框架(Collect

- MybatisHelloWorld

3213213333332132

//测试入口TestMyBatis

package com.base.helloworld.test;

import java.io.IOException;

import org.apache.ibatis.io.Resources;

import org.apache.ibatis.session.SqlSession;

import org.apache.ibat

- Java|urlrewrite|URL重写|多个参数

7454103

javaxmlWeb工作

个人工作经验! 如有不当之处,敬请指点

1.0 web -info 目录下建立 urlrewrite.xml 文件 类似如下:

<?xml version="1.0" encoding="UTF-8" ?>

<!DOCTYPE u

- 达梦数据库+ibatis

darkranger

sqlmysqlibatisSQL Server

--插入数据方面

如果您需要数据库自增...

那么在插入的时候不需要指定自增列.

如果想自己指定ID列的值, 那么要设置

set identity_insert 数据库名.模式名.表名;

----然后插入数据;

example:

create table zhabei.test(

id bigint identity(1,1) primary key,

nam

- XML 解析 四种方式

aijuans

android

XML现在已经成为一种通用的数据交换格式,平台的无关性使得很多场合都需要用到XML。本文将详细介绍用Java解析XML的四种方法。

XML现在已经成为一种通用的数据交换格式,它的平台无关性,语言无关性,系统无关性,给数据集成与交互带来了极大的方便。对于XML本身的语法知识与技术细节,需要阅读相关的技术文献,这里面包括的内容有DOM(Document Object

- spring中配置文件占位符的使用

avords

1.类

<?xml version="1.0" encoding="UTF-8"?><!DOCTYPE beans PUBLIC "-//SPRING//DTD BEAN//EN" "http://www.springframework.o

- 前端工程化-公共模块的依赖和常用的工作流

bee1314

webpack

题记: 一个人的项目,还有工程化的问题嘛? 我们在推进模块化和组件化的过程中,肯定会不断的沉淀出我们项目的模块和组件。对于这些沉淀出的模块和组件怎么管理?另外怎么依赖也是个问题? 你真的想这样嘛? var BreadCrumb = require(‘../../../../uikit/breadcrumb’); //真心ugly。

- 上司说「看你每天准时下班就知道你工作量不饱和」,该如何回应?

bijian1013

项目管理沟通IT职业规划

问题:上司说「看你每天准时下班就知道你工作量不饱和」,如何回应

正常下班时间6点,只要是6点半前下班的,上司都认为没有加班。

Eno-Bea回答,注重感受,不一定是别人的

虽然我不知道你具体从事什么工作与职业,但是我大概猜测,你是从事一项不太容易出现阶段性成果的工作

- TortoiseSVN,过滤文件

征客丶

SVN

环境:

TortoiseSVN 1.8

配置:

在文件夹空白处右键

选择 TortoiseSVN -> Settings

在 Global ignote pattern 中添加要过滤的文件:

多类型用英文空格分开

*name : 过滤所有名称为 name 的文件或文件夹

*.name : 过滤所有后缀为 name 的文件或文件夹

--------

- 【Flume二】HDFS sink细说

bit1129

Flume

1. Flume配置

a1.sources=r1

a1.channels=c1

a1.sinks=k1

###Flume负责启动44444端口

a1.sources.r1.type=avro

a1.sources.r1.bind=0.0.0.0

a1.sources.r1.port=44444

a1.sources.r1.chan

- The Eight Myths of Erlang Performance

bookjovi

erlang

erlang有一篇guide很有意思: http://www.erlang.org/doc/efficiency_guide

里面有个The Eight Myths of Erlang Performance: http://www.erlang.org/doc/efficiency_guide/myths.html

Myth: Funs are sl

- java多线程网络传输文件(非同步)-2008-08-17

ljy325

java多线程socket

利用 Socket 套接字进行面向连接通信的编程。客户端读取本地文件并发送;服务器接收文件并保存到本地文件系统中。

使用说明:请将TransferClient, TransferServer, TempFile三个类编译,他们的类包是FileServer.

客户端:

修改TransferClient: serPort, serIP, filePath, blockNum,的值来符合您机器的系

- 读《研磨设计模式》-代码笔记-模板方法模式

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.sql.Connection;

import java.sql.DriverManager;

import java.sql.PreparedStatement;

import java.sql.ResultSet;

- 配置心得

chenyu19891124

配置

时间就这样不知不觉的走过了一个春夏秋冬,转眼间来公司已经一年了,感觉时间过的很快,时间老人总是这样不停走,从来没停歇过。

作为一名新手的配置管理员,刚开始真的是对配置管理是一点不懂,就只听说咱们公司配置主要是负责升级,而具体该怎么做却一点都不了解。经过老员工的一点点讲解,慢慢的对配置有了初步了解,对自己所在的岗位也慢慢的了解。

做了一年的配置管理给自总结下:

1.改变

从一个以前对配置毫无

- 对“带条件选择的并行汇聚路由问题”的再思考

comsci

算法工作软件测试嵌入式领域模型

2008年上半年,我在设计并开发基于”JWFD流程系统“的商业化改进型引擎的时候,由于采用了新的嵌入式公式模块而导致出现“带条件选择的并行汇聚路由问题”(请参考2009-02-27博文),当时对这个问题的解决办法是采用基于拓扑结构的处理思想,对汇聚点的实际前驱分支节点通过算法预测出来,然后进行处理,简单的说就是找到造成这个汇聚模型的分支起点,对这个起始分支节点实际走的路径数进行计算,然后把这个实际

- Oracle 10g 的clusterware 32位 下载地址

daizj

oracle

Oracle 10g 的clusterware 32位 下载地址

http://pan.baidu.com/share/link?shareid=531580&uk=421021908

http://pan.baidu.com/share/link?shareid=137223&uk=321552738

http://pan.baidu.com/share/l

- 非常好的介绍:Linux定时执行工具cron

dongwei_6688

linux

Linux经过十多年的发展,很多用户都很了解Linux了,这里介绍一下Linux下cron的理解,和大家讨论讨论。cron是一个Linux 定时执行工具,可以在无需人工干预的情况下运行作业,本文档不讲cron实现原理,主要讲一下Linux定时执行工具cron的具体使用及简单介绍。

新增调度任务推荐使用crontab -e命令添加自定义的任务(编辑的是/var/spool/cron下对应用户的cr

- Yii assets目录生成及修改

dcj3sjt126com

yii

assets的作用是方便模块化,插件化的,一般来说出于安全原因不允许通过url访问protected下面的文件,但是我们又希望将module单独出来,所以需要使用发布,即将一个目录下的文件复制一份到assets下面方便通过url访问。

assets设置对应的方法位置 \framework\web\CAssetManager.php

assets配置方法 在m

- mac工作软件推荐

dcj3sjt126com

mac

mac上的Terminal + bash + screen组合现在已经非常好用了,但是还是经不起iterm+zsh+tmux的冲击。在同事的强烈推荐下,趁着升级mac系统的机会,顺便也切换到iterm+zsh+tmux的环境下了。

我为什么要要iterm2

切换过来也是脑袋一热的冲动,我也调查过一些资料,看了下iterm的一些优点:

* 兼容性好,远程服务器 vi 什么的低版本能很好兼

- Memcached(三)、封装Memcached和Ehcache

frank1234

memcachedehcachespring ioc

本文对Ehcache和Memcached进行了简单的封装,这样对于客户端程序无需了解ehcache和memcached的差异,仅需要配置缓存的Provider类就可以在二者之间进行切换,Provider实现类通过Spring IoC注入。

cache.xml

<?xml version="1.0" encoding="UTF-8"?>

- Remove Duplicates from Sorted List II

hcx2013

remove

Given a sorted linked list, delete all nodes that have duplicate numbers, leaving only distinct numbers from the original list.

For example,Given 1->2->3->3->4->4->5,

- Spring4新特性——注解、脚本、任务、MVC等其他特性改进

jinnianshilongnian

spring4

Spring4新特性——泛型限定式依赖注入

Spring4新特性——核心容器的其他改进

Spring4新特性——Web开发的增强

Spring4新特性——集成Bean Validation 1.1(JSR-349)到SpringMVC

Spring4新特性——Groovy Bean定义DSL

Spring4新特性——更好的Java泛型操作API

Spring4新

- MySQL安装文档

liyong0802

mysql

工作中用到的MySQL可能安装在两种操作系统中,即Windows系统和Linux系统。以Linux系统中情况居多。

安装在Windows系统时与其它Windows应用程序相同按照安装向导一直下一步就即,这里就不具体介绍,本文档只介绍Linux系统下MySQL的安装步骤。

Linux系统下安装MySQL分为三种:RPM包安装、二进制包安装和源码包安装。二

- 使用VS2010构建HotSpot工程

p2p2500

HotSpotOpenJDKVS2010

1. 下载OpenJDK7的源码:

http://download.java.net/openjdk/jdk7

http://download.java.net/openjdk/

2. 环境配置

▶

- Oracle实用功能之分组后列合并

seandeng888

oracle分组实用功能合并

1 实例解析

由于业务需求需要对表中的数据进行分组后进行合并的处理,鉴于Oracle10g没有现成的函数实现该功能,且该功能如若用JAVA代码实现会比较复杂,因此,特将SQL语言的实现方式分享出来,希望对大家有所帮助。如下:

表test 数据如下:

ID,SUBJECTCODE,DIMCODE,VALUE

1&nbs

- Java定时任务注解方式实现

tuoni

javaspringjvmxmljni

Spring 注解的定时任务,有如下两种方式:

第一种:

<?xml version="1.0" encoding="UTF-8"?>

<beans xmlns="http://www.springframework.org/schema/beans"

xmlns:xsi="http

- 11大Java开源中文分词器的使用方法和分词效果对比

yangshangchuan

word分词器ansj分词器Stanford分词器FudanNLP分词器HanLP分词器

本文的目标有两个:

1、学会使用11大Java开源中文分词器

2、对比分析11大Java开源中文分词器的分词效果

本文给出了11大Java开源中文分词的使用方法以及分词结果对比代码,至于效果哪个好,那要用的人结合自己的应用场景自己来判断。

11大Java开源中文分词器,不同的分词器有不同的用法,定义的接口也不一样,我们先定义一个统一的接口:

/**

* 获取文本的所有分词结果, 对比

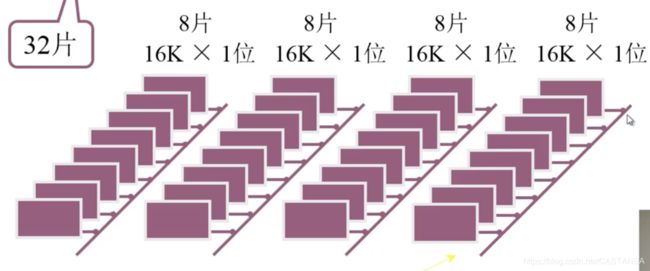

![]() =16MB

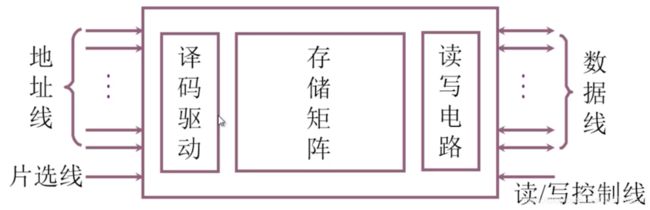

=16MB![]() 字节,有8M字)

字节,有8M字)![]()

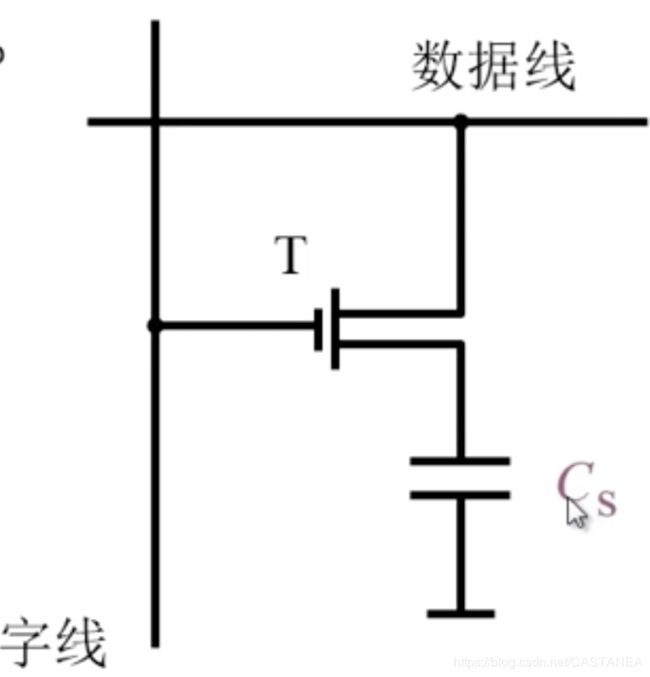

(CS是芯片选择的缩写)上边一横表示低电平有效,标示这个管脚如果是低电平,这次数据访问的地址就是在这个存储矩阵当中

(CS是芯片选择的缩写)上边一横表示低电平有效,标示这个管脚如果是低电平,这次数据访问的地址就是在这个存储矩阵当中 (CE是芯片使能的缩写)

(CE是芯片使能的缩写)![]() (标示低电平写,高电平读)或 两根线

(标示低电平写,高电平读)或 两根线![]() (读)

(读)![]() (写)

(写) =16根线 给定一个输入,在输出端只有一根线有效,只有一根线上的信号会控制相应的存储单元中的所有的存储元件进行数据输入输出操作

=16根线 给定一个输入,在输出端只有一根线有效,只有一根线上的信号会控制相应的存储单元中的所有的存储元件进行数据输入输出操作 是读写控制信号,低电平表示写 ,高电平表示读 对2214存储芯片的的某一个存储单元进行读或者是写要给出相应的WE信号是高电平还是低电平

是读写控制信号,低电平表示写 ,高电平表示读 对2214存储芯片的的某一个存储单元进行读或者是写要给出相应的WE信号是高电平还是低电平 是片选信号,只有CS是低电平时,2114芯片才会被选中

是片选信号,只有CS是低电平时,2114芯片才会被选中 通过T4对读数据线进行充电,使读数据线变成高电平,如果进行读出,读选择信号线有效,T2导通,若Cg保存的信息是0,则T1的栅极是低电平,T1不会导通,读数据线就会保持高电平,也就是说如果是0,在读数据线上,读出的就是1,若保存的信号是1,则T1的栅极有电,T1导通,数据线读数据线会通过T2、T1放电变成低电平,读出的和原存的信息是相反的,如果想读到正确的信号,则在读数据线的输出端要加一个非门。

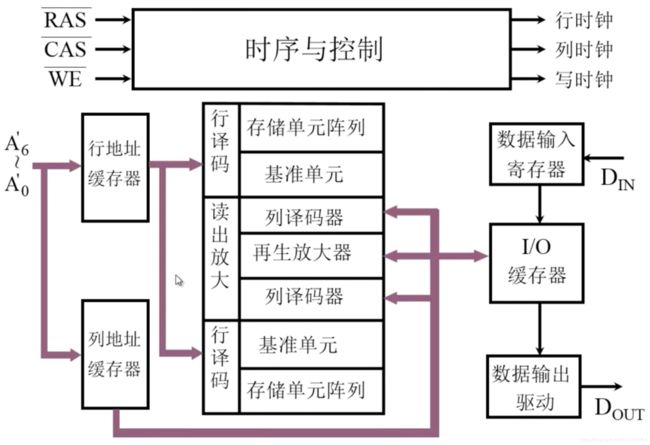

通过T4对读数据线进行充电,使读数据线变成高电平,如果进行读出,读选择信号线有效,T2导通,若Cg保存的信息是0,则T1的栅极是低电平,T1不会导通,读数据线就会保持高电平,也就是说如果是0,在读数据线上,读出的就是1,若保存的信号是1,则T1的栅极有电,T1导通,数据线读数据线会通过T2、T1放电变成低电平,读出的和原存的信息是相反的,如果想读到正确的信号,则在读数据线的输出端要加一个非门。 行选通信号,

行选通信号, 列选通信号,

列选通信号, 读写控制信号作为输入,产生行时钟,列时钟和写时钟,完成了芯片内部的读和写操作

读写控制信号作为输入,产生行时钟,列时钟和写时钟,完成了芯片内部的读和写操作 为读写及维持操作

为读写及维持操作 为某一行的刷新操作

为某一行的刷新操作