Q:RC-Corner跟PVT怎么组合?

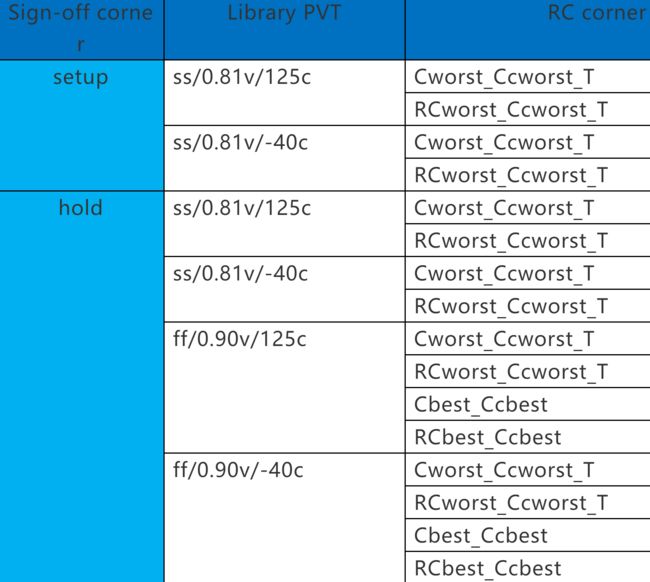

A:通常的组合:

Q:通常说的ttcorner指的是啥?

A:@孟时光 ttcorner是指管子在tt+RCtyp吧。

Typesof corners

When working in the schematic domain, weusually only work with frontend of line (FEOL) process corners as these corners willaffect the performance of devices. But there is an orthogonal set of processparameters that affect back endof line (BEOL) parasitics.

FEOL corners

One naming convention for process corners isto use two-letter designators, where the first letter refers to the N-channel MOSFET (NMOS) corner, and the second letter refers to the P channel (PMOS)corner. In this naming convention, three corners exist: typical, fast and slow. Fast and slow corners exhibit carrier mobilities that are higher and lower than normal,respectively. For example, a corner designated as FS denotes fast NFETs and slow PFETs.

There are therefore five possible corners:typical-typical (TT) (not really a corner of an n vs. p mobility graph, butcalled a corner, anyway), fast-fast (FF), slow-slow (SS), fast-slow (FS), andslow-fast (SF). The first three corners (TT, FF, SS) are called even corners,because both types of devices are affected evenly, and generally do notadversely affect the logical correctness of the circuit. The resulting devicescan function at slower or faster clock frequencies, and are often binned as such. The last two corners (FS, SF) are called "skewed"corners, and are cause for concern. This is because one type of FET will switchmuch faster than the other, and this form of imbalanced switching can cause oneedge of the output to have much less slew than the other edge. Latching devices may then record incorrect values in the logic chain.

BEOL corners

In addition to the FETs themselves, there are more on-chip variation (OCV) effects thatmanifest themselves at smaller technology nodes. These include process, voltageand temperature (PVT) variation effects on on-chip interconnect, as well as viastructures.

Extraction tools often have a nominal corner to reflect the nominal cross section of the process target.Then the corners cbest and cworst were created to model the smallest andlargest cross sections that are in the allowed process variation. A simplethought experiment shows that the smallest cross section with the largestvertical spacing will produce the smallest coupling capacitance. CMOS Digitalcircuits were more sensitive to capacitance than resistance so this variationwas initially acceptable. As processes evolved and resistance of wiring becamemore critical, the additional rcbest and rcworst werecreated to model the minimum and maximum cross sectional areas for resistance.But the one change is that cross sectional resistance is not dependent on oxidethickness (vertical spacing between wires) so for rcbest the largest is used and for rcworst the smallest is used.

Parameters

Mostimportantly, the corners of a process are designated by five parameters

-

Mobility variation due to implantation of N+ and P+

-

Vthvariation

-

Resistance of the actives

-

Bodycoefficient

-

Oxidethickness

Otherparameters like the effective Length, effective width, Cjsw caps, Cj caps alsochange.

注:所以TT corner并不是一个需要sign-off的corner。

Q:dishing可以理解成过度刻蚀嘛?

A:@孟时光 不是刻蚀,意思差不多,就多啃掉了一块

Q:为什么铜软?

A:@孟时光 Cu相对氧化硅比较软。大概是:刀子能划铜板,不能划玻璃。

Q:@LZH 有没懂的大牛 scan 下这个问题可以autofix吗?

A:@junbojia 最好不用Autofix, 如果D10 Vio比较多的话, autofix不知道会给你fix成什么样子, autofix会对后端产生一些影响,比如timing,routing.

-

建议1:分析一下电路, 看能否再RTL上休掉,如果rtl能修最好rtl修。

-

建议2:不修,这类vio 容易造成mismatch,但是现在ATPG算法能够处理这种情况,避免生成这类pattern。 可能会使patter count受影响。

-

建议3:一般scan insertin都不建议开autofix, 如果要开autofix,插完链以后,report一下都插入了哪些autofix,分析一下合理不。关于autofix DRC,一般不建议开。 但是C家有一个feature, 通过autofix来加入提高coverage,和隔离x-source,具说很好用,但是要advance license。

Q:RTL难修怎么办?

A:那就不修,交给atpg处理。

Q:不修,那对atpg影响是什么?

A:这类vio 容易造成mismatch, 但是现在ATPG算法能够处理这种情况,避免生成这类pattern。 可能会使patter count受影响。

Q:@松泉石 问问C家timingsignoff tools,大家有使用的么?

A:Innovus+TSO应该 很多用 innovus 做16以下的项目的人都用过吧

Q:@松泉石 我今天遇到一个问题: sdf annotation completed, 0 Errors, 比较多的Warning,结果vcs 出现 Segmentation fault

A:@占少君 limit stacksize unlimited

Q:@Lauque 问一个问题,怎么理解eFUSE?

A:@wbefuse就是一次性烧入不可更改的rom,每个row有一个bit用来指示是否该row已被烧入,烧入前需要输入一串固定的码这个码应该是efuse厂家提供的 匹配之后才能烧入。

@唐欣 EFUSE理解成保险丝,烧断之前逻辑是1,烧断之后逻辑是0