Xilinx Zynq mpsoc 的 pcie Tandem 配置

参照Xilinx 《UltraScale Devices Gen3Integrated Block for PCI Express v4.4》 LogiCORE IP Product Guide中的Ch.3章节中的Tandem Configuration.

PCI Express specification对设备的要求是PERST# must deassert 100 ms after the power good of the systems has occurred, and a PCI Express port must be ready to link train no more than 20 ms after PERST# has deasserted.但是FPGA加载包含有PCIE IP 的Bit文件时间就已经远远超过了120ms.于是Xilinx PCIE的IP里有叫做Tandem的功能用来首先将一部分有关与PCIE的配置加载到FPGA中,好让FPGA在100ms实现PCIE识别训练所必须的配置.

这里对Tandem配置的FPGA部分不做讨论,在PG156文档中包含了如何去配置PCIE的IP和如何去修改约束文件等等.在这里只讨论Zynq系列的ARM硬核+FPGA平台下如何去将Tandem功能配置好.

手册中解释的是由Vivado综合出来1个完整的Bit文件,然后再将此Bit文件通过工具生成出PROM文件比如MCS文件来烧录到SPI FLASH等存储器中.

Vivado也可以生成出两段Bit文件,分别为Stage1和Stage2,以此用JTAG分别下载来验证Tandem功能的完整性和正确性.

在Xilinx SDK开发环境下,一般采用默认生成的FSBL,此FSBL无法将一个Bit文件自主分段加载到FPGA中,也就导致了包含有1个Bit文件的PROM文件,无法实现Tandem的功能,因为Bit 通过FSBL加载只能整个加载,所耗费的时间一般也是超过100ms的.

这时候在保证尽量少改动FSBL的动机下,可以使用用于JTAG验证的两段Bit文件进行FPGA的配置.将FSBL修改为支持加载2段Bit文件.

FSBL配置FPGA是通过PCAP interface实现的,通过PCAP,PS可以将PROM中所包含的FPGA配置信息加载到FPGA中.

而PCAP的使用包含了初始化和加载阶段.

初始化阶段进行PCAP的寄存器配置,其中包含Clear FPGA的有关动作,这个动作在Stage2加载时应该去掉,以免Stage2的加载影响到已经加载进FPGA的Stage1部分,并且在开启Stage2的配置之前,确保Stage1已经配置完毕.

Zynq ultrascale+ mpsoc的pcap status寄存器描述如下:

Pcap status(CSU) Register

可以通过检测此寄存器的Bit3来判断Stage1是否加载完成,如果Bit3为1,则Stage1加载完成.

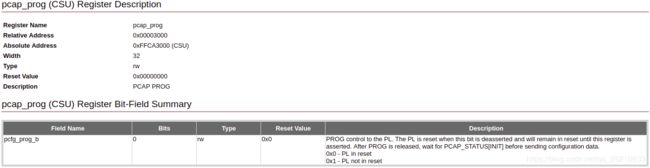

Pcap prog寄存器用来Reset PL,寄存器描述如下

对此寄存器的操作包含了Clear PL的动作,所以在Stage1配置前应当保留以下代码,对PL Reset操作,只在Stage2配置时应当删除此段代码,以免Clear PL

/* Reset PL */

XFsbl_Out32(CSU_PCAP_PROG, 0x0U);

(void)usleep(PL_RESET_PERIOD_IN_US);

XFsbl_Out32(CSU_PCAP_PROG, CSU_PCAP_PROG_PCFG_PROG_B_MASK);

/*

* Wait for PL_init completion

* Bypass this check in platforms not supporting PCAP interface

*/

PlatInfo = XGet_Zynq_UltraMp_Platform_info();

if ((PlatInfo != (u32)XPLAT_ZYNQ_ULTRA_MP)

&& (PlatInfo != (u32)XPLAT_ZYNQ_ULTRA_MPQEMU)) {

/* To confirm house cleaning of PL is started */

do {

RegVal = XFsbl_In32(CSU_PCAP_STATUS) &

CSU_PCAP_STATUS_PL_CFG_RST_MASK;

} while (RegVal != CSU_PCAP_STATUS_PL_CFG_RST_MASK);

/* To confirm house cleaning of PL is done */

do {

RegVal = XFsbl_In32(CSU_PCAP_STATUS) &

CSU_PCAP_STATUS_PL_INIT_MASK;

} while (RegVal != CSU_PCAP_STATUS_PL_INIT_MASK);

} else {

XFsbl_Printf(DEBUG_GENERAL,

"PCAP interface is not supported in this platform \r\n");

}

Load阶段就是FPGA配置信息加载阶段,此阶段使用CSU DMA将Bit Stream加载到PL,此部分可沿用FSBL代码.