usb68013固件之SlaveFIFO

选择SlaveFIFO传输方式

SlaveFIFO传输示意如图1:

图1 Slave FIFO传输示意图

在Slave FIFO方式下,FX2LP内嵌的8051固件的功能只是配置Slave FIFO 相关的寄存器以及控制FX2LP何时工作在Slave FIFO模式下。一旦8051固件将相关的寄存器配置完毕,且使自身工作在SlaveFIFO模式下后,外部逻辑(如FPGA)即可按照SlaveFIFO的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。

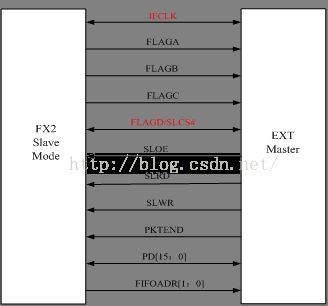

在SlaveFIFO方式下外部逻辑与FX2的连接信号图如图2所示:

图2 FX2 SlaveFIFO模式端口引脚连接信号

SlaveFIFO传输方式可分为同步和异步两种,由于同步方式对时钟要求严格,故选择异步传输方式。以下为异步SlaveFIFO读写方式:

异步SlaveFIFO读

异步SlaveFIFO读的标准连接图如图3所示:

图3 异步FIFO读引脚连接

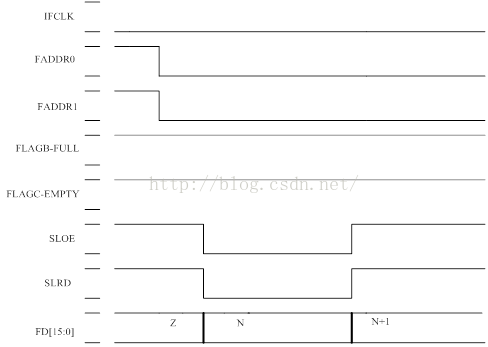

异步Slave FIFO读的标准时序如下:

IDLE:当读事件发生时,进状态1;

状态1:使FIFOADR[1:0]指向OUT FIFO,进状态2;

状态2:如FIFO空,在本状态等待,否则进状态3;

状态3:使SLOE有效,使SLRD有效,从数据线上读数,再使SLRD无效,,以递增FIFO读指针,再使SLOE无效,进状态4;

状态4:如需传输更多的数,进状态2,否则进状态IDLE。

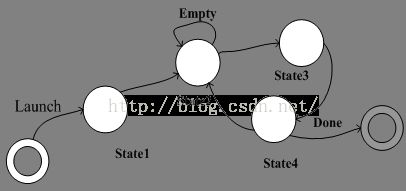

状态跳转示意图如图4:

图4 异步FIFO读状态跳转

几种情况的时序图示意如图5所示(FULL,EMPTY,SLRD,SLOE均假定低有效):

图5 异步FIFO读时序

异步Slave FIFO写:

异步Slave FIFO写的标准连接图如图6:

图6 异步FIFO写连接图

异步Slave FIFO写的标准时序如下:

IDLE:当写事件发生时,进状态1;

状态1:使FIFOADR[1:0]指向IN FIFO,进状态2;

状态2:如FIFO满,在本状态等待,否则进状态3;

状态3:驱动数据到数据线上,使SLWR有效,再无效,以使FIFO写指针递增,进状态4;

状态4:如需传输更多的数,进状态2,否则进状态IDLE。

状态跳转示意图如图7:

图7 异步FIFO写状态跳转

几种情况的时序图示意如图8(FULL,EMPTY,SLWR,PKTEND均假定低有效):

图8 异步FIFO写时序

Slave FIFO模式下常用寄存器

| IFCONFIG |

接口配置寄存器 |

EPxFIFOPFH/L |

FIFO 可编程PF状态长度 |

|

| PINFLAGAB |

FLAGx引脚配置 寄存器 |

PORTACFG |

端口A配置 |

|

| PINFLAGCD |

INPKTEND |

强制结束IN传输寄存器 |

||

| FIFORESET |

端点缓冲复位寄存器 |

EPxFLAGIE |

端点FIFO中段 |

|

| FIFOPINPOLAR |

引脚极性设置寄存器 |

EPxFLAGIRQ |

||

| EPxCFG |

端点2/4/6/8配置 |

EPxFIFOBCH:L |

端点FIFO计数 |

|

| EPxFIFOCFG |

端点FIFO配置 |

EPxFLAGS |

端点状态标志寄存器 |

|

| EPxAUTOINLENH:L |

端点长度设置 |

EPxFIFOBUF |

端点缓冲寄存器 |

|

编程举例

cy7c68013-56在使用Slave FIFO进行数据传输的时候,默认EP2、EP4作为OUT端点,EP6、EP8作为IN端点。一般要用到FLAGA,FLAGB,FLAGC,FLAGD几个引脚,用于得到端点的状态,寄存器PINFLAGSAB,PINFLAGSCD用于设置这四个引脚的功能。程序举例如下:

PINFLAGSAB =0xe8; // FLAGA - fixed EP2EF(empty flag), FLAGB -fixed EP6FF(full flag)

SYNCDELAY; //FLAGA引脚,EP2空时为0,非空为1,FLAGB引脚,EP6满为0,非满为1。信号有效电平通过FIFOPINPOLAR寄存器设置,0为低有效,1为高有效,默认都为低有效。

PINFLAGSCD =0xac; // FLAGC - fixed EP2FF, FLAGD - fixed EP6EF

SYNCDELAY; //FLAGC引脚,EP2满时为0,非空为1,FLAGD引脚,EP6空为0,非满为1

FIFORESET是用于FIFO状态复位的。复位FIFO如下:

FIFORESET =0x80; // activate NAK-ALL toavoid race conditions

SYNCDELAY; // see TRM section 15.5.4

FIFORESET =0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET =0x04; // reset, FIFO 4

SYNCDELAY; //

FIFORESET =0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET =0x08; // reset, FIFO 8

SYNCDELAY; //

FIFORESET =0x00; // deactivate NAK-ALL

SYNCDELAY; //

EPxFIFOCFG,用于设置端点的操作方式。

EP2FIFOCFG =0x11; //AUTOOUT="1", WORDWIDE="1"

SYNCDELAY; //自动输出端点,8位数据总线

EP4FIFOCFG =0x11; // AUTOOUT="1",WORDWIDE="1"

SYNCDELAY; //自动输出端点,8位数据总线

EP6FIFOCFG =0x0c; // AUTOIN="1",ZEROLENIN="1", WORDWIDE="1"

SYNCDELAY; //自动输入端点,允许0长度端点,8位数据总线

EP8FIFOCFG =0x0c; // AUTOIN="1",ZEROLENIN="1", WORDWIDE="1"

SYNCDELAY; //自动输入端点,允许0长度端点,8位数据总线