基于FPGA的扩频系统设计(中)

今天给大侠带来基于FPGA的扩频系统设计,由于篇幅较长,分三篇。今天带来第一篇,中篇。话不多说,上货。

导读

在无线通信系统中,普遍使用扩频通信技术,因此扩频技术对通信系统具有重要的现实意义。直接序列扩频技术是应用最广的一种扩频技术,FPGA具备高速度的并行性特点在无线通信系统中的优势日益增强,利用FPGA实现直接序列扩频技术,可增大传输速率,可以使扩频技术有更好的发展与应用。

本篇利用本原多项式产生伪随机序列用作扩频,通过同步模块对扩频后的信号进行捕获,通过直接序列解扩模块进行解扩。本篇给出了编解码、扩频解扩、同步的整体方案,使用Quartus实现功能,并结合Matlab和ModelSim对模块进行调试和测试,实现扩频通信模块的搭建仿真,验证其设计的正确性。首先概述了方案设计与论证、整体方案的设计、各个模块的设计、个别模块的调试与各个模块的仿真验证。本篇主要实现的模块有:汉明编码模块、直接序列扩频模块、量化器模块、同步模块、直接序列解扩模块和汉明译码模块。各位大侠可依据自己的需要进行阅读,参考学习。

第二篇内容摘要:本篇会介绍软件开发平台及软件模块设计,包括FPGA芯片、设计和仿真验证平台、汉明码编码设计模块、直接序列扩频模块原理、量化器模块设计、同步模块设计、直接序列解扩模块设计、汉明码译码模块设计等相关内容。

三、软件开发平台及软件模块设计

3.1 FPGA芯片

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,通过提高密度、降低功耗和成本等手段,FPGA已经披靡传统ASIC领域,在众多新兴应用领域加速渗透。如今FPGA在通信、图像处理和控制方面也有发展,在未来具有很好的发展前景。

本论文设计采用的FPGA芯片是altera公司的CycloneⅡ系列EP2C70F896C6芯片,该芯片具有4个锁相环,150个内嵌乘法器、622个I/O引脚、48416个寄存器和68416个逻辑单元,其中拥有专用的乘法器,可以大幅度有效地提高系统的整体性能,同时也可以提高系统的整体稳定性。

![]()

3.2 设计和仿真验证平台

3.2.1 Quartus设计软件平台

Quartus II 11.0 是 Altera 公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、Verilog等多种设计形式,自带有综合器和仿真器,支持IP核,包含宏功能模块库,使用户可以充分利用成熟的模块,简化了设计流程,加快了设计速度。该平台支持一个工作环境下的设计要求,其中包括支持基于Internet的协作设计,可以在XP、Linux和Unix上使用。

3.2.2 ModelSim仿真验证软件平台

ModelSim 5.5是Mentor公司的HDL语言仿真软件,是业界唯一的单内核支持VHD和Verilog混合编程仿真器。编译仿真速度快,编译代码与平台无关,有利于IP核的保护,ModelSim 5.5具有以下特点:RTL和门级优化、本地编译结构、编译仿真速度快和跨平台跨版本仿真;集成了性能分析、波形比较和代码覆盖等。选用ModelSim 5.5作为本设计的各个模块的功能及仿真波形验证软件。

3.2.3 Matlab仿真验证软件平台

Matlab是MATrix LABoratory的缩写,是一款由美国The MathWorks公司出品的商业数学软件。Matlab是一种用于算法开发、数据可视化、数据分析以及数值计算的高级技术计算语言和交互式环境。利用Matlab r2011b软件所带库函数,有利于部分功能仿真。

![]()

3.3 汉明码编码模块设计

3.3.1 汉明编码原理

在香农的时代,二战结束的那段时候,贝尔实验室聚集了很多人才,他们那时的工作对我们今天数字世界的影响非常重要,如图基(John Tukey)创始了现代统计学,汉明(Richard Wesley Hamming)成功的进行了纠错码研究,他们的成果恩泽天下。

本文中的汉明编码模块采用汉明(7,4)码,全部码长是7位:C6~C0,其中4位是原始信息位D,3位是奇偶效验位P,通过如下表3.1方式组成:

表3.1 汉明码组成表

由表3.1可知,汉明码具有纠正错码的能力,在后续章节3.5.1节详细介绍。

3.3.2 汉明编码设计

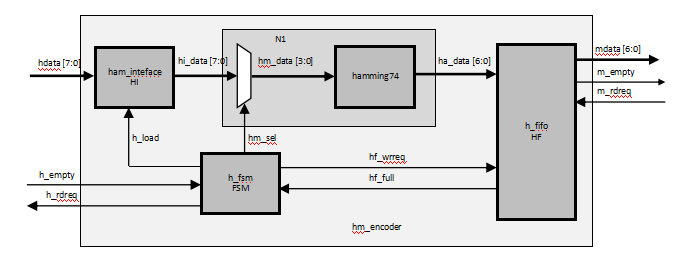

根据表3.1可知,校验位P为对应的原始信息码异或得到,其它位直接输出即可,因此设计得到如图3.1的设计模型:

图3.1 汉明码编码设计模型

如图3.2为汉明编码模块在总设计中的设计模型。首先利用控制模块h_fsm的h_load信号控制输入数据的更新,当完成8bits数据编码后才更新输入数据。由于数据是8bits而汉明码每次编码对象数据为4bits,因此利用控制模块h_fsm的hm_sel信号控制数据高4位或低4位进行汉明编码,利用h_fifo模块(fifo)对数据进行缓存,通过对fifo空标志信号m_empty高电平有效进行判断,如信号m_empty有效则置fifo读操作使能信号m_rdreq高电平进行读取编码后的数据,其他情况为低电平。设计模型对应Verilog代码详见附录A。

图3.2 汉明编码模块总设计模型

![]()

3.4 直接序列扩频模块设计

3.4.1 直接序列扩频原理

直接序列扩频是用待传输的数据信息与伪随机序列异或,用来扩展传输信号的带宽。原理如图3.3所示。传输信号不经过扩频直接传输,受到信道的噪声干扰,导致信号失真。若经过扩频后传输,可以提高抗噪声能力。

图3.3 直接序列扩频原理图

在3.1香农定理公式中,C是信道容量,单位为比特每秒(bps);B是信道带宽,单位是Hz,S/N是信噪比。

![]() (3.1)

(3.1)

根据3.1香农定理公式可知,当信道容量C不变时,增加带宽B,则可以容许信噪比减小;或者说,在信道的信噪比很小时(如无线通信中噪声很大情况下)为了保证正常的通信,则需要增大带宽B。很多情况下,基带(原始数据)信号的带宽不足以满足上式,直接用这样的基带信号经过调制后进行通信,经常会受到噪声的干扰,甚至无法进行正常通信,因此使用直接序列进行扩频。

伪随机序列是最长线性移位寄存器序列的简称,它是由多级移位寄存器或其延迟元件通过线性反馈产生最长的码序列,在移位寄存器里,若移位寄存器级数为n,则能产生2n个状态,除去一个全“0”状态,则还剩2n-1个状态。因此n级移位寄存器能产生的最大长度的码序列为2n-1。

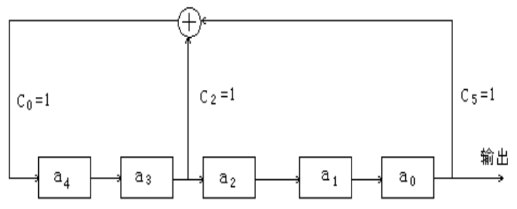

本文采用本原多项式产生伪随机序列,利用伪随机序列与原始信号异或得到扩频后的信号。本原多项式an-i、…a1、a0为一组N位移位寄存器,在每个时钟下,该移位寄存器的每一位发送变化,每一位ai的变化是由其输入信号决定,该输入信号则是后级电路与系数C层次异或的结果决定的,原理图如图3.4所示。

图3.4 伪随机序列原理图

3.4.2 直接序列扩频模块设计

要产生所需的伪随机序列,需要先确定序列级数r,确定级数相当于确定了伪随机序列的长度,本文采用5相多项式:X5+X2+1,对应有31个伪随机数,原理图如图3.5所示:

图3.5 5相伪随机序列原理图

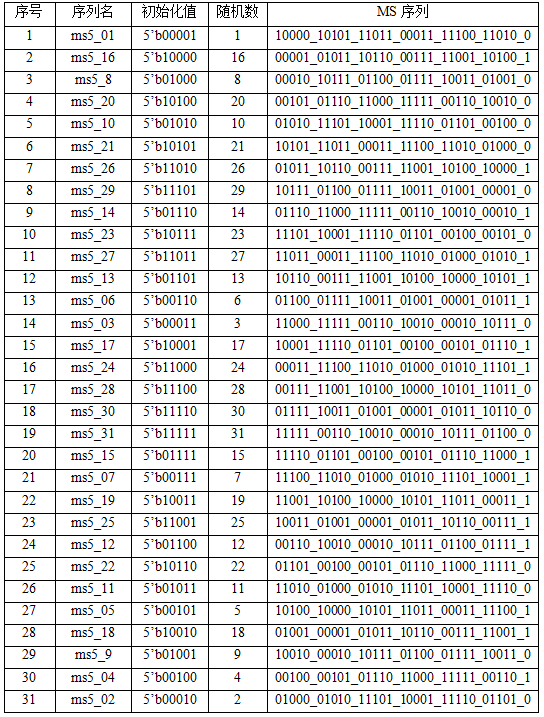

5相多项式的初始状态为a4a3a2a1a0=00001,a4为a0和a3异或得到的,其余的为上一级得到。每到来一个时钟上升沿按上图移位一次,从a0产生输出(1个bit宽度的串行输出,5位变量最多可产生31种组合),不同的初始值对应不同的输出序列,输出的序列都为31bits,对应输出序列如表3.2所示:

表3.2 伪随机序列表

根据表3.2可得出本原多项式具有以下9点特性:

1. 无论设置的初始值是什么,序列仅是开始位置变化,序列本身并无变化;

2. 伪随机数PRN是伪随机序列从置位开始后的头5个比特;

3. 每一个相邻的伪随机序列,其相位差一拍;

3. 每31个时钟周期循环一次;

4. PRN中没有0;

5. 在一个伪随机序列周期内,PRN随机分布(被洗牌);

7. 序列名与ms序列头5比特为镜像对称;

8. 前一个为下一个的向左循环移位;

9. 1的个数比0的个数多1个。

本设计主时钟信号clk为10MHz,设计模型如图3.6所示。首先,编码后的信号经过接口m_interface模块接收到数据信号。其次,将接收到的数据信号通过并串转换模块变成单比特数据,利用计数器counter模块控制伪随机序列与单比特数据进行异或操作,最后达到扩频的目的,设计模型对应Verilog代码详见附录A。

图3.6 扩频模块设计图

![]()

3.5 量化器模块设计

在实际传输过程中,需要用D/A转换芯片将数字信号转换为模拟信号进行发送,在传输过程会引入噪声,量化器的模块主要是模拟此过程,将单比特的信号变为8bits有符号数,也为后续引入噪声做准备。在模块设计中,利用选择器即可实现此操作,设计模型如图3.7所示,对应Verilog代码详见附录A。

图3.7 量化器模块设计图

![]()

3.6 同步模块设计

3.6.1 同步原理

同步的作用就是在时间不确定的情况下,捕获到有用的伪随机序列,使本地的伪随机序列与数据同步,因此在解调前必须对数据进行同步处理。如图3.8所示,接收端无法知道序列中起始位置,无法保证接收序列的开始位与发送序列的开始位一致,同时为避免丢失发送数据和保证正确恢复数据位,所以在发送数据前需加同步头,能够起到接收端接收数据的同步作用。

图3.8 接收端信号接收示意图

同步头需要加到发送端数据信号起始位置,同步头Frame_Head为14bits,数据信号为8bits位宽。具体如表3.3所示:

表3.3 字边界和帧边界定义表

在检测到同步头之前,首先接收端应与同步头扩频后的数据进行对齐,由于接收端采到某位同步头数据的不定位置,所以要用31个不同伪随机序列模板对采集到的31bits数据进行最小二乘法(3.3.2节进行介绍)计算。以进行判定与哪个序列模板最吻合,判定的方法是将累加器的初始值设定为0,利用累加器对最小二乘法运算的结果进行累加,与阈值进行比较,经过多次实验,最终判定阈值为50000。

3.6.2 最小二乘法原理

最小二乘法(least square)由德国数学家高斯发明,其基本思想就是多维空间的点距问题,由此可以解决数学中的相关分析和拟合等问题。

1801年,由于谷神星运行至太阳背后,失去了谷神星的轨迹,奥地利天文学家海因里希·奥尔伯斯根据高斯计算出来的轨道,重新发现了谷神星。高斯计算的轨道,看成是多维空间的一个点,原观察轨道亦为另一个点,将这两点的距离趋于最小化,即是当时高斯所做的一切,这就是最小二乘法的来源。

直接序列同步利用最小二乘法来比对31bits数据与模板之间的相似程度,通过与阈值进行比较,确定是否捕获到有用信号,如果为有用信号,则进行相应的延时处理,已达到能够与同步头数据对齐的目的,尽最大可能地正确还原数据信息。

3.6.3 同步设计

设计模型如图3.9所示,首先,在接收端生成与发送端相同的伪随机数,其次用计数器控制输入31bits数据,输入数据分别与31个模板进行最小二乘法计算,用来比对相似度,通过得到的计算值与阈值进行比较,该模块会判断出输入数据为对应的伪随机数,从而判断出对齐帧头需要多少个系统时钟周期。最后,位置信息输出后利用计数器进行计数,相当于延时操作,当计数值达到所需延时时间后,说明已对齐同步头中的某一位,设计模型对应Verilog代码详见附录A。

图3.9 同步头位置判断模块

![]()

3.7 直接序列解扩模块设计

设计模块如图3.10所示。在同步头对齐后,对于直接序列解扩模块与同步模块相似,首先,利用本地时钟生成与发送端相同的伪随机序列,m_leastsouare模块是对数据“0”和“1”扩频后的伪随机序列模板与对齐后31bits数据进行最小二乘法计算,计算值进行比较大小,计算值小的对应解扩为“0”或“1”,通过判断连续几个“1”后并且判断出“0”,说明同步头结束,下一位则是发送端发送的数据信息,将数据信息解扩后输出送给串并转换及汉明译码模块。设计模型对应Verilog代码详见附录A。

图3.10 直接序列解扩模块设计图

![]()

3.8 汉明译码模块设计

3.8.1 汉明译码原理

由本文3.1节说明了编码模块编码原理,根据表3.1汉明码组成结构,可以知道P0P1P2为校验字节,C0为D3D1D0P0异或得到,C1为D3D2D0P1异或得到,C2为D3D2D1P2异或得到。如果由附加位C0和C1为“1”,C2为“0”,因此可以推断D0发生错误;如果由附加位C1和C2为“1”,C0为“0”,则可以判断D2发生错误;如果附加位C0、C1和C2均为“1”,则可以判断D3发生错误;如果仅C0为“1”,则可以判断校验位P0发生错误。

以此类推,通过判断哪个区域发生共同错误,来判断具体哪一位发生错误,如图3.11所示:

图3.11 汉明纠错码原理图

3.8.2 汉明译码设计

设计模型如图3.12所示。首先,通过inteface模块对数据信息进行串并转换将串行信号转换为并行信号。其次,利用start1_mk模块对haming_decoder模块进行使能控制,当使能信号start高电平有效时,haming_decoder模块对数据进行译码和纠错。haming_decoder模块输出数据位4bits,通过start_mk模块的信号lh进行控制输出信号为数据的高四位还是低四位。counter模块用来辅助inteface模块和haming_decoder模块,对数据比特位置进行判断。最后输出信号为8bits位宽。设计模型对应Verilog代码详见附录A。

图3.12 汉明译码模块设计图

![]()

本篇到此结束,下一篇带来基于FPGA的扩频系统设计(下),介绍分析调试,包括汉明码解码模块调试、直接序列扩频模块调试、同步模块调试、整体设计资源占用率、整体设计RTL设计图,还会介绍系统测试,包括汉明编码模块测试、直接序列扩频模块测试、量化器模块测试、同步模块测试、直接序列解扩模块测试、汉明译码模块测试、系统整体测试等相关内容。

END

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

![]()

精彩推荐

基于FPGA的实时图像边缘检测系统设计(下)

FIR数字滤波器设计(下)

基于 FPGA Vivado 信号发生器设计(附源工程)

“FPGA产品设计与研发 ” 零基础入门及就业