【FPGA】Buffer专题介绍(三)

目录

背景

IOBUF

IOBUFDS

OBUF

OBUFDS

OBUFT

OBUFTDS

背景

首先给出这个专题的第一个地址:【FPGA】Buffer专题介绍(一)

第二篇的地址:【FPGA】Buffer专题介绍(二)

好了,正式进入主题:

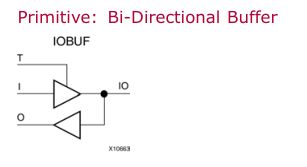

IOBUF

原语:双向缓冲(Primitive: Bi-Directional Buffer)

The design element is a bidirectional single-ended I/O Buffer used to connect internal logic to an external bidirectional pin.

设计元素是双向单端I / O缓冲器,用于将内部逻辑连接到外部双向引脚。

这个Buffer不需要用户自己例化,综合工具来推断什么时候使用,并自动添加到设计中。

有关双向端口我还没用过,这里不便说太多。

如果非要例化使用,也可以,给出例化模板:

Verilog Instantiation Template

// IOBUF: Single-ended Bi-directional Buffer

// All devices

// Xilinx HDL Libraries Guide, version 11.2

IOBUF #(

.DRIVE(12), // Specify the output drive strength

.IBUF_DELAY_VALUE("0"), // Specify the amount of added input delay for the buffer,

// "0"-"12" (Spartan-3E only), "0"-"16" (Spartan-3A only)

.IFD_DELAY_VALUE("AUTO"), // Specify the amount of added delay for input register,

// "AUTO", "0"-"6" (Spartan-3E only), "0"-"8" (Spartan-3A only)

.IOSTANDARD("DEFAULT"), // Specify the I/O standard

.SLEW("SLOW") // Specify the output slew rate

) IOBUF_inst (

.O(O), // Buffer output

.IO(IO), // Buffer inout port (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input, high=input, low=output

);

// End of IOBUF_inst instantiationIOBUFDS

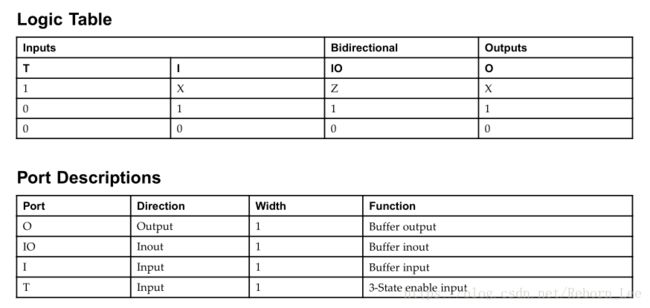

原语:具有低电平有效输出的3态差分信号I / O缓冲器(Primitive: 3-State Differential Signaling I/O Buffer with Active Low Output Enable)

需要自己例化使用,有没有发现只要是差分转单端的,都需要自己例化使用。

Verilog Instantiation Template

// IOBUFDS: Differential Bi-directional Buffer

// Virtex-4/5, Spartan-3/3E/3A

// Xilinx HDL Libraries Guide, version 11.2

IOBUFDS #(

.IBUF_DELAY_VALUE("0"), // Specify the amount of added input delay for the buffer,

// "0"-"12" (Spartan-3E only), "0"-"16" (Spartan-3A only)

.IFD_DELAY_VALUE("AUTO"), // Specify the amount of added delay for input register,

// "AUTO", "0"-"6" (Spartan-3E only), "0"-"8" (Spartan-3A only)

.IOSTANDARD("DEFAULT") // Specify the I/O standard

) IOBUFDS_inst (

.O(O), // Buffer output

.IO(IO), // Diff_p inout (connect directly to top-level port)

.IOB(IOB), // Diff_n inout (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input, high=input, low=output

);

// End of IOBUFDS_inst instantiationOBUF

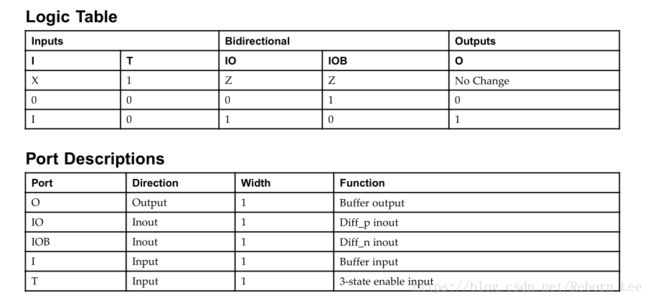

数据手册描述仅供参考:

This design element is a simple output buffer used to drive output signals to the FPGA device pins that do not need to be 3-stated (constantly driven). Either an OBUF, OBUFT, OBUFDS, or OBUFTDS must be connected to every output port in the design.

This element isolates the internal circuit and provides drive current for signals leaving a chip. It exists in input/output blocks (IOB). Its output (O) is connected to an OPAD or an IOPAD. The interface standard used by this element is LVTTL. Also, this element has selectable drive and slew rates using the DRIVE and SLOW or FAST constraints. The defaults are DRIVE=12 mA and SLOW slew.

该设计元素是一个简单的输出缓冲器,用于将输出信号驱动到FPGA器件引脚,这些引脚不需要是三态的(恒定驱动)。 必须将OBUF,OBUFT,OBUFDS或OBUFTDS连接到设计中的每个输出端口。

该元件隔离内部电路并为离开芯片的信号提供驱动电流。 它存在于输入/输出块(IOB)中。 其输出(O)连接到OPAD或IOPAD。 该元素使用的接口标准是LVTTL。 此外,该元件具有可选的驱动和转换速率,使用DRIVE和SLOW或FAST约束。 默认值为DRIVE = 12 mA和SLOW转换。

该元件不需要用户干预,综合工具根据需求自动添加。如果非要例化使用,也可以,给出模板;

Verilog Instantiation Template

// OBUF: Single-ended Output Buffer

// All devices

// Xilinx HDL Libraries Guide, version 11.2

OBUF #(

.DRIVE(12), // Specify the output drive strength

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUF_inst (

.O(O), // Buffer output (connect directly to top-level port)

.I(I) // Buffer input

);

// End of OBUF_inst instantiationOBUFDS

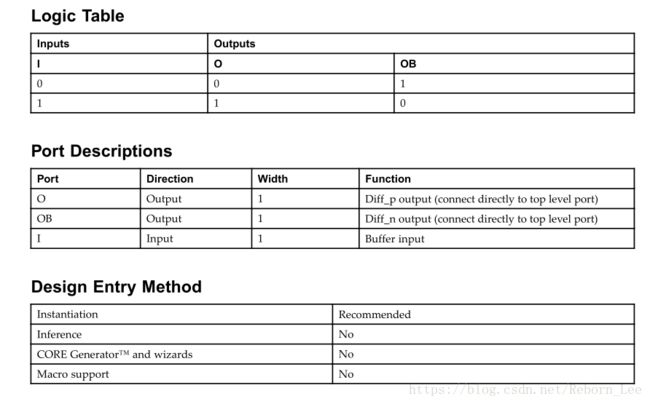

差分信号输出缓冲

看了这么多Buffer,也该总结出规律了,这个是差分的输出buffer,肯定需要用户自己例化使用。

给出用户手册的描述吧:

This design element is a single output buffer that supports low-voltage, differential signaling (1.8 v CMOS). OBUFDS isolates the internal circuit and provides drive current for signals leaving the chip. Its output is represented as two distinct ports (O and OB), one deemed the "master" and the other the "slave." The master and the slave are opposite phases of the same logical signal (for example, MYNET and MYNETB).

该设计元件是单输出缓冲器,支持低压差分信号(1.8 v CMOS)。 OBUFDS隔离内部电路,为离开芯片的信号提供驱动电流。 它的输出表示为两个不同的端口(O和OB),一个被视为“主”,另一个被视为“从属”。 主设备和从设备是相同逻辑信号的相位(例如,MYNET和MYNETB)。

不用看也知道这是干嘛的。

Verilog Instantiation Template

// OBUFDS: Differential Output Buffer

// Virtex-4/5, Spartan-3/3E/3A

// Xilinx HDL Libraries Guide, version 11.2

OBUFDS #(

.IOSTANDARD("DEFAULT") // Specify the output I/O standard

) OBUFDS_inst (

.O(O), // Diff_p output (connect directly to top-level port)

.OB(OB), // Diff_n output (connect directly to top-level port)

.I(I) // Buffer input

);

// End of OBUFDS_inst instantiationOBUFT

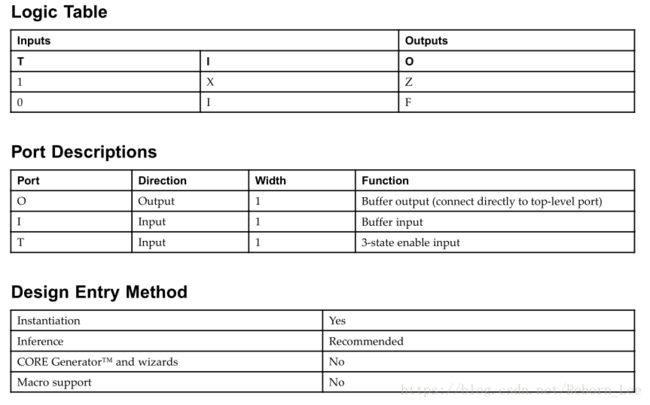

有一个低电平有效的使能端,三态输出缓冲

This design element is a single, 3-state output buffer with input I, output O, and active-Low output enables (T).

This element uses the LVTTL standard and has selectable drive and slew rates using the DRIVE and SLOW or FAST constraints. The defaults are DRIVE=12 mA and SLOW slew.

When T is Low, data on the inputs of the buffers is transferred to the corresponding outputs. When T is High, the output is high impedance (off or Z state). OBUFTs are generally used when a single-ended output is needed with a 3-state capability, such as the case when building bidirectional I/O.

此设计元素是单个3态输出缓冲器,具有输入I,输出O和低电平有效输出使能(T)。

该元件使用LVTTL标准,并使用DRIVE和SLOW或FAST约束选择驱动和转换速率。 默认值为DRIVE = 12 mA和SLOW转换。

当T为低时,缓冲器输入的数据被传送到相应的输出。 当T为高电平时,输出为高阻抗(关闭或Z状态)。 OBUFT通常在需要具有3态功能的单端输出时使用,例如构建双向I / O时的情况。

综合工具自己添加进设计中。但也可以例化使用:

Verilog Instantiation Template

// OBUFT: Single-ended 3-state Output Buffer

// All devices

// Xilinx HDL Libraries Guide, version 11.2

OBUFT #(

.DRIVE(12), // Specify the output drive strength

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFT_inst (

.O(O), // Buffer output (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input

);

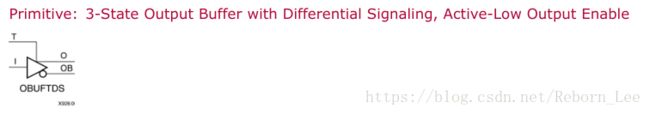

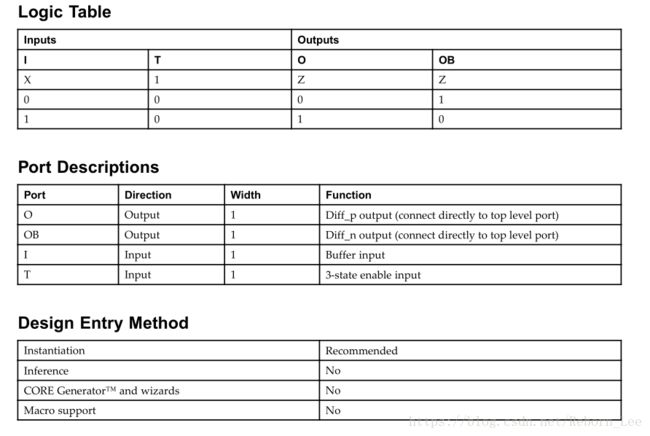

// End of OBUFT_inst instantiationOBUFTDS

这个我真的不想说了,就多了一个输出是差分的。

自己例化使用。

Verilog Instantiation Template

// OBUFTDS: Differential 3-state Output Buffer

// Virtex-4/5, Spartan-3/3E/3A

// Xilinx HDL Libraries Guide, version 11.2

OBUFTDS #(

.IOSTANDARD("DEFAULT") // Specify the output I/O standard

) OBUFTDS_inst (

.O(O), // Diff_p output (connect directly to top-level port)

.OB(OB), // Diff_n output (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input

);

// End of OBUFTDS_inst instantiation三篇文章,终于把有关buffer的东西总结的差不多了,说实话,有点力不从心了,由于感冒,导致胃口也不好,几天没好好吃东西了,眼睛也有点花,可还是坚持学习,把这一块写完,我就可以回去休息了。

有些东西理解的不够,还望见谅。

我最后应该还会总结一篇关于Buffer的博文,聚集需要用户自己例化才能使用的一些常见的buffer,有针对性而非这样笼统。撤了撤了,想法真多,流水线还没总结呢。