https://mp.weixin.qq.com/s/iw8bxdcJr_5bpM6ELaEghA

随着FPGA在数据中心加速和Smart NIC在SDN和NFV领域的广泛应用,基于以太网接口的FPGA开发板越来越受到关注。而更高速率的以太网接口技术则是应用的关键,本文将详细介绍基于FPGA的10G以太网接口的原理及调试技术。欢迎留言讨论。

10G以太网接口简介

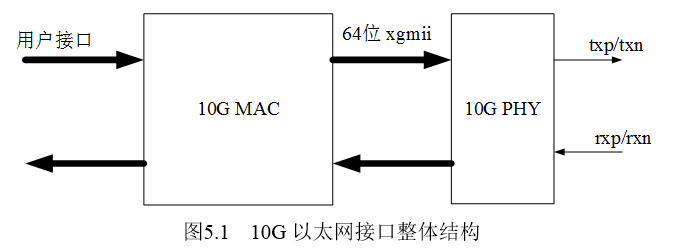

1、10G以太网结构

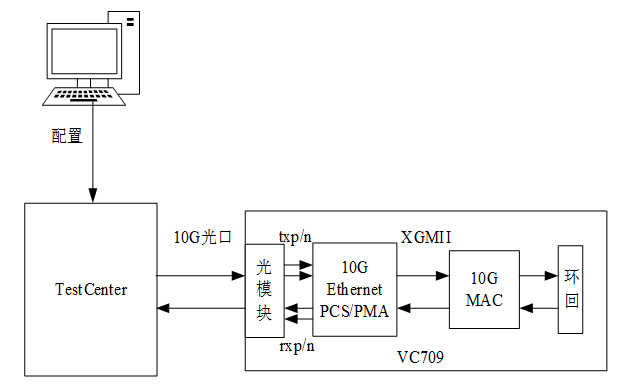

10G以太网接口分为10G PHY和10G MAC两部分。如下图所示。

本设计中使用了Xilinx公司提供的10GEthernet PCS/PMA IP核充当连接10GMAC的PHY芯片,然后将该IP核约束到光模块上构建完整的物理层。需要说明的是本设计主要是完成以太网二层逻辑设计,不涉及PHY层的逻辑设计,如:bit同步、字节同步、字同步、64b/66b编解码等。

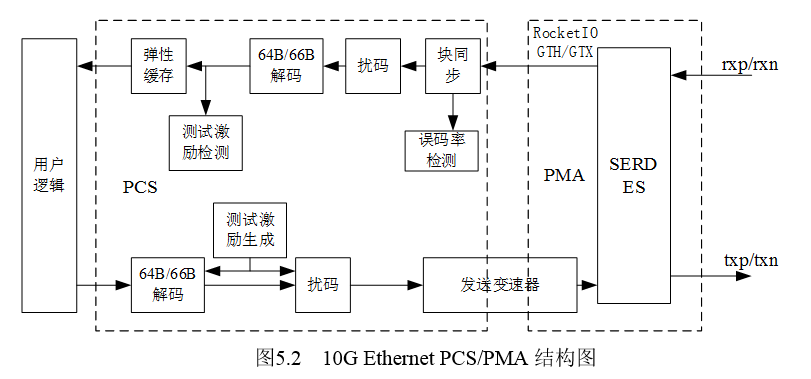

2、10G以太网接口PHY

10G EthernetPCS/PMA的整体结构如图5.2所示,其核心是基于RocketIO GTH/GTX来实现的。从图中可知,该模块分为PCS层和PMA层,对于发送数据,PCS层主要功能是对数据进行64B/66B编码、扰码、发送变速等功能。同时在测试模式下还提供了一个测试激励源,用于对链路进行检测。PMA层的主要功能是提供并串转换、对串行信号进行驱动并发送等功能。对于接收数据,PMA层的主要功能是将接收到的高速差分信号进行串并转换、bit同步、时钟恢复等功能,PCS层对于从PMA层接收到的数据进行块同步、解扰码、64B/66B解码、弹性缓存等。同时在测试模式下还提供测试激励检测功能,用于检测链路工作状态。

在接口调试过程中,可能用到PMA层的近端环回和远端环回功能。PMA近端回环,用于测试IP核内部自回环;PMA远端回环,用于将接收到的远端10G PHY发送的的数据在PMA层直接回环发送给远端10G PHY,而不经过本地的PCS层。

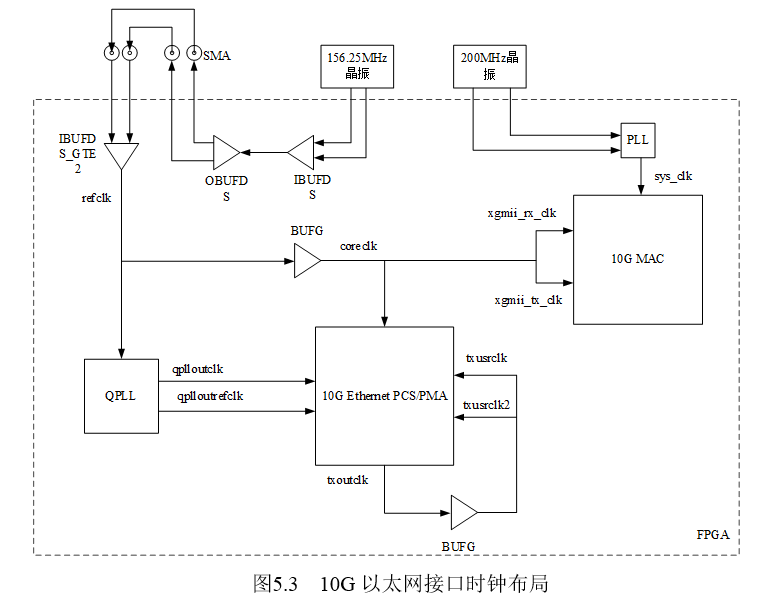

3、10G以太网接口时钟布局设计

由于10G Ethernet PCS/PMA是Xilinx官方提供的一款IP核,所以我们需要做的工作是结合开发板的实际情况,为该IP核以及其他模块设计合理的时钟电路,使其能够正常工作。本文选用Xilinx VC709开发板作为上板调试的硬件平台,因此我们的时钟布局需要充分考虑此开发板的结构来设计,具体的时钟布局如图5.3所示。

由于VC709开发板连接光模块的Quad并没有直接输入的参考时钟,而是连接到一对SMA接口,因此我们将156.25Mhz晶振产生的时钟经过FPGA内部的IBUFDS、OBUFDS驱动后输出到另一对SMA接口,并通过同轴电缆将两对SMA接口互联,从而使连接光模块的Quad具有输入参考时钟。

对于FPGA内部的时钟布局主要分为以下4部分:

(a)输入的差分参考时钟经过一个参考钟专用缓存(IBUFDS_GTE2)变为单端时钟refclk,然后将refclk分为两路,一路接到QPLL(QuadraturephasePhase Locking Loop),另一路时钟经过一个BUFG后转变为全局时钟coreclk,继续将coreclk分为两路,一路作为10G MAC核XGMII接口的收发时钟(xgmii_rx_clk和xgmii_tx_clk),另一路用于驱动10G Ethernet PCS/PMA IP核内部用户侧的逻辑。

(b) 对于QPLL输出的两路时钟qplloutclk和qplloutrefclk,主要是用于IP核内GTH收发器使用的高性能时钟,其中qplloutclk直接用于驱动GTH内发送端的串行信号,其频率为5.15625GHz。qplloutrefclk用于驱动GTH内部部分逻辑模块,频率为156.25MHz。

(c) txoutclk是由10G Ethernet PCS/PMA IP产生的一个322.26MHz的时钟,该时钟经过BUFG后分为两路,其中txusrclk用于驱动IP核内GTH的32bits总线数据,txusrclk2用于驱动IP核内PCS层部分模块。

(d)200MHz的晶振产生差分时钟输入到FPGA内的PLL(Phase LockingLoop)模块,PLL模块以200MHz差分钟为驱动时钟生成192MHz用户钟(sys_clk)发送给10G MAC核用户侧。

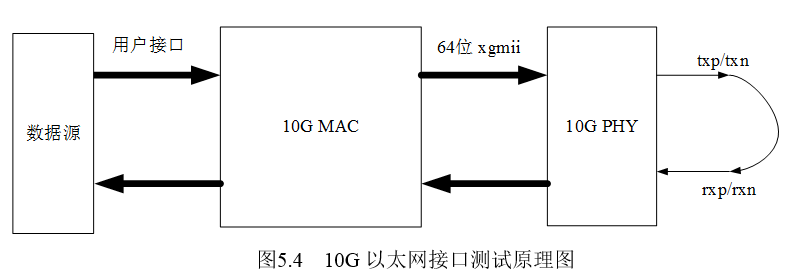

4、仿真验证

在本节中我们主要是对10G MAC核和10G Ethernet PCS/PMA IP核进行联合仿真测试,用于检测两个模块结合后能否稳定运行。具体的测试原理如图5.4所示。

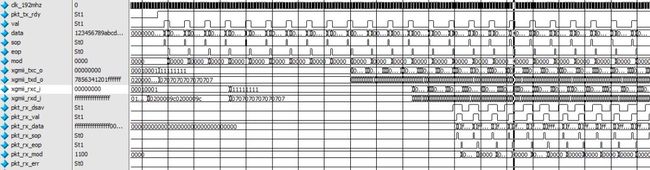

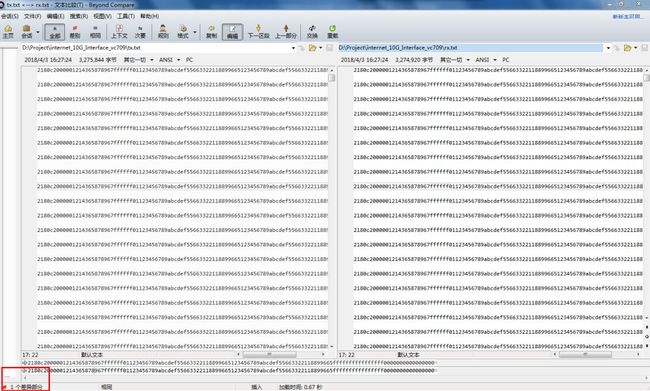

将10G Ethernet PCS/PMA IP核的高速串行差分信号的输入输出相连,实现回环测试。我们在10G MAC核的用户侧的设置一个数据源用于发送数据帧,数据经过MAC核后转变为标准以太网帧,通过XGMII接口发送到10G Ethernet PCS/PMA IP核,10G Ethernet PCS/PMA IP核将其变为高速串行差分信号输出,高速串行差分信号经过回环被10GEthernet PCS/PMA IP核接收,重复上述过程的逆过程,最终数据在10G MAC核的用户侧接收接口被恢复。本测试具体分为3个步骤:定长最短帧(64Bytes)仿真测试、定长最长帧(1518Bytes)仿真测试、随机帧长仿真测试。在每一个测试步骤中,我们要尽可能模拟10Gbps的业务流。对于数据的检测,我们不但要对比波形是否正确,还要将10GMAC核用户侧的收发数据分别记录到两个文档内,并使用软件对两个文档内的数据对比来判断收发数据是否一致。由于篇幅限制,我们只给出定长最短帧的仿真结果截图。

10G以太网接口板级调试

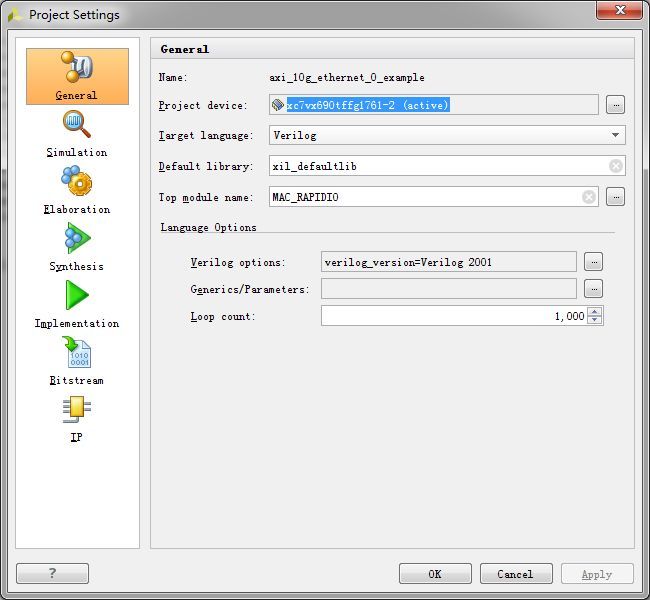

1、工程设置

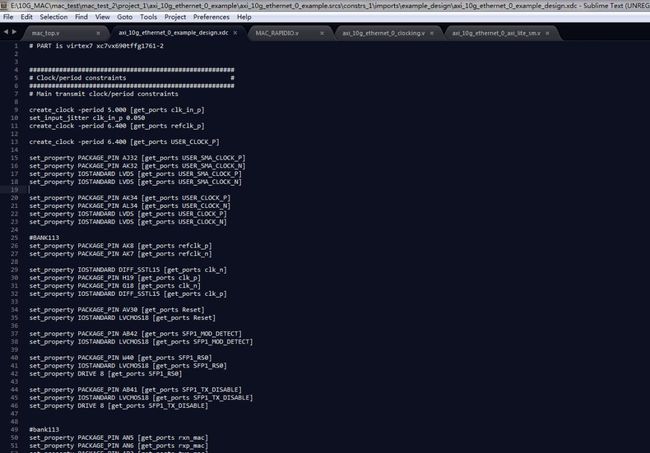

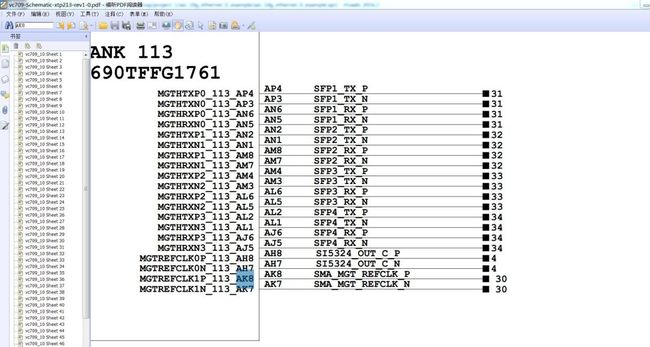

软件环境为VIVADO2016.2,芯片设置为xc7vx690tffg1761-2 (active),板子采用Xilinx的VC709开发板。

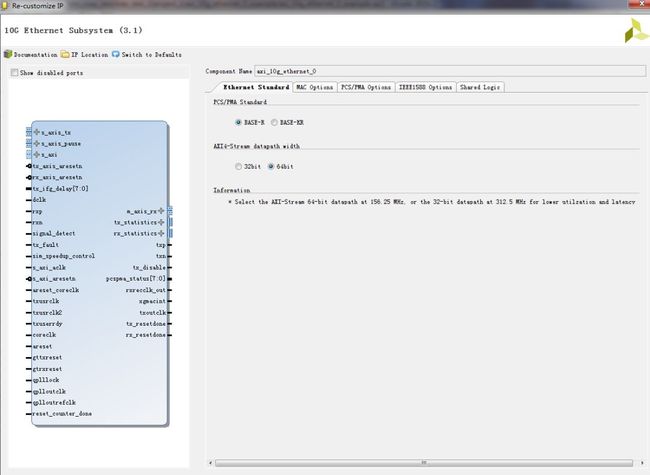

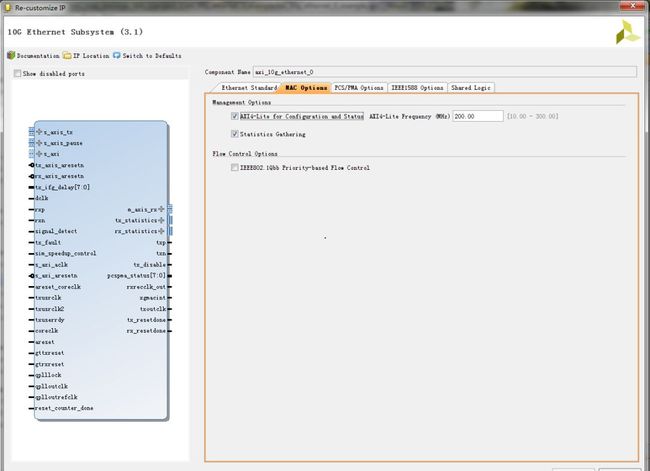

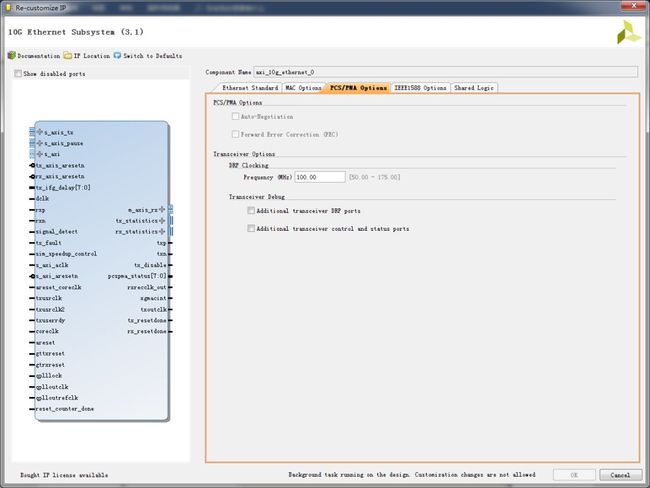

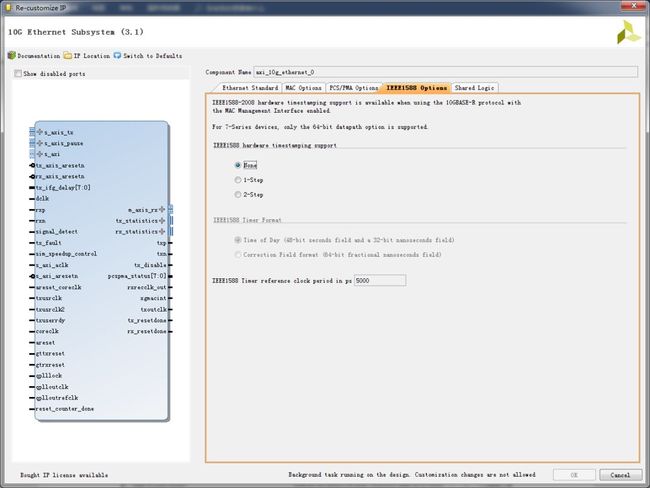

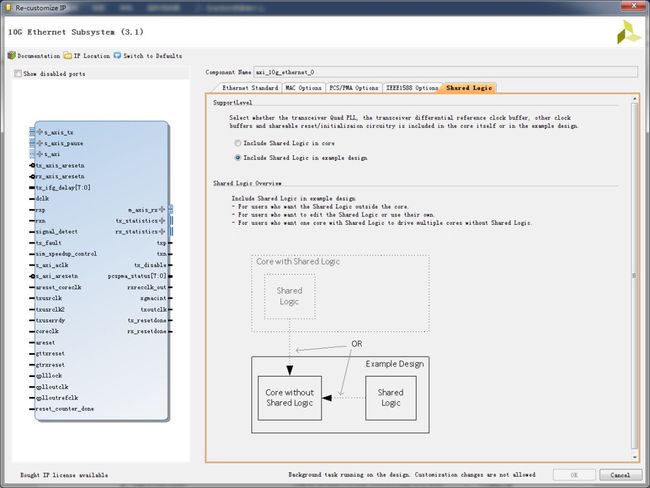

首先选择IP核,在界面中选择10G Ethernet Subsystem,PCS/PMA选择 BASE-R,位宽选择为64bit,其他标签中的选项默认即可。

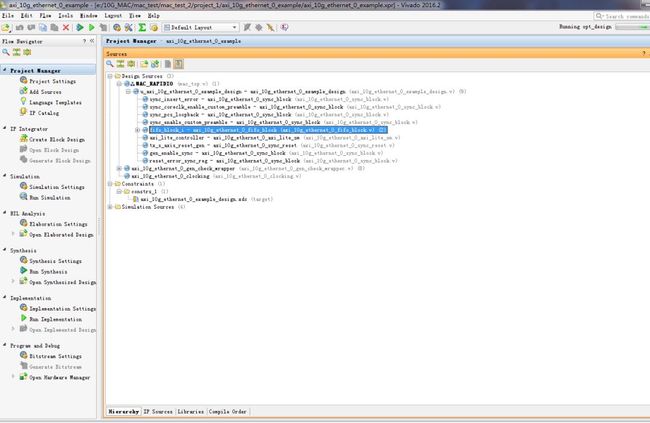

待IP核生成结束之后,右键IP核,选择Open Ip Example Design,VIVADO便会自动生成一个Example Design,如下图所示:

此时example design设置完成,此时的工程中自带一个数据源,即axi_10g_ethernet_0_gen_check_wrapper模块,但此数据源通过函数产生数据,不能综合,所以为配合Testcenter打流测试,将此数据源删掉。

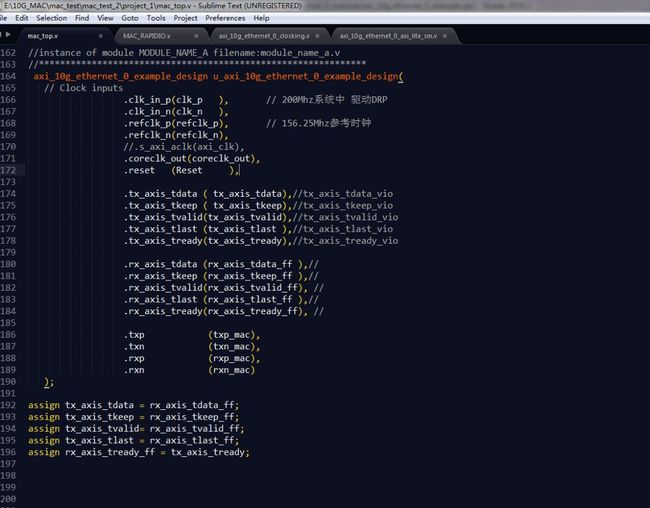

为方便进行管脚分配,在生成的example design上新生成了一个顶层文件,并在此顶层模块中将用户侧输入输出的数据接在一起,实现MAC核的自回环。

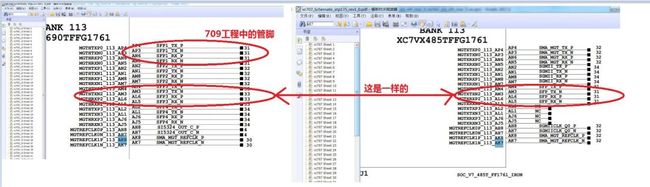

此外在xdc文件中,管脚分配如下图所示:

2、上板验证

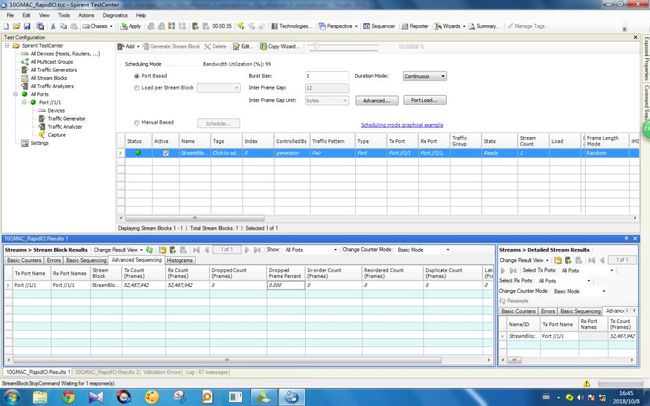

板级验证环境连接图如下,通过10G TestCenter用光口给VC709板子打流,在VC709板子的690T FPGA内部编写逻辑进行用户侧的环回,通过观察连接TestCenter的配置PC机上界面,就可以判断回环的测试是否成功。

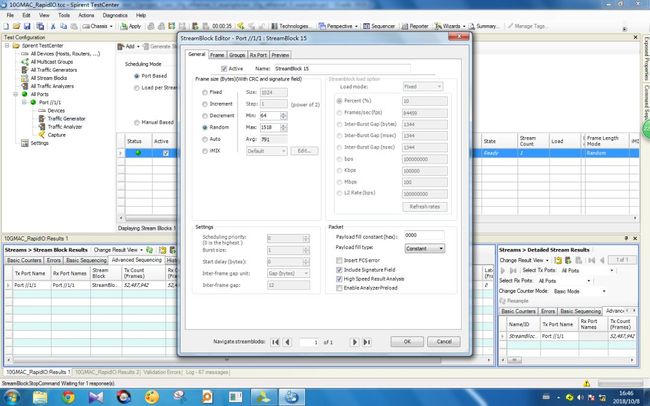

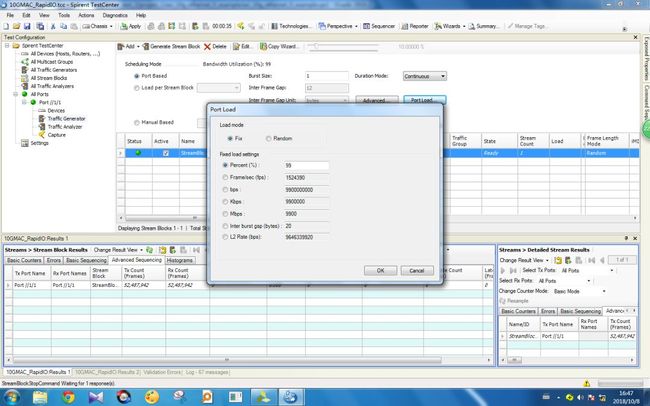

通过10G Testcenter打流测试,首先配置测试环境,帧长为随机帧长(64~1518),速率设置为10G(实际设置为9.9G,当满速10G时Testcenter会出现一些丢帧错误,9.9G不会出现问题,但我们采用自己写的10G以太网MAC核,而非Vivado工具生成的MAC核时,可以支持满负荷线速处理,本文只给出采用Vivado生成的MAC核的演示结果)。

测试结果如下图所示,可以发现数据可以正常收发,且没有丢帧。

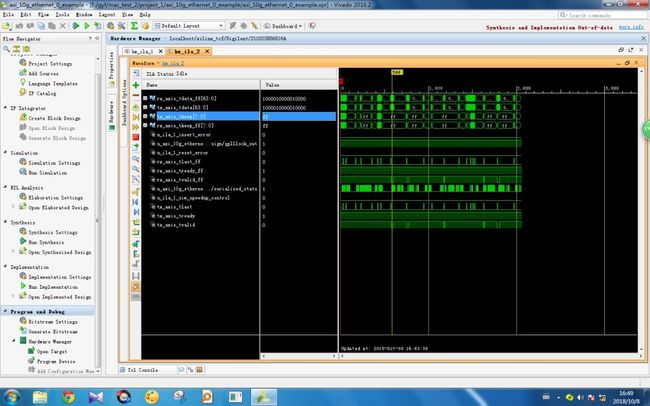

并在VIVADO中抓取了用户侧信号,结果如下图所示,数据收发正常。

本例程仅说明回环测试,在实际应用中,数据进来后,就可以用FPGA进行各种需要的处理。如矩阵运算、图像处理、机器学习、压缩、非对称加密、Bing 搜索等。可以大幅度的降低CPU软件的负荷,提高整体的处理能力。

参考时钟管脚分配注意事项

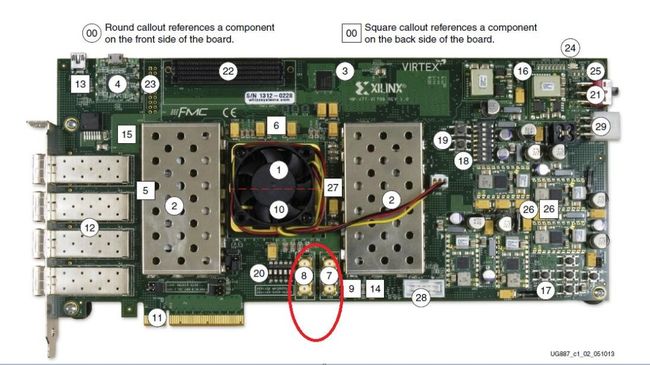

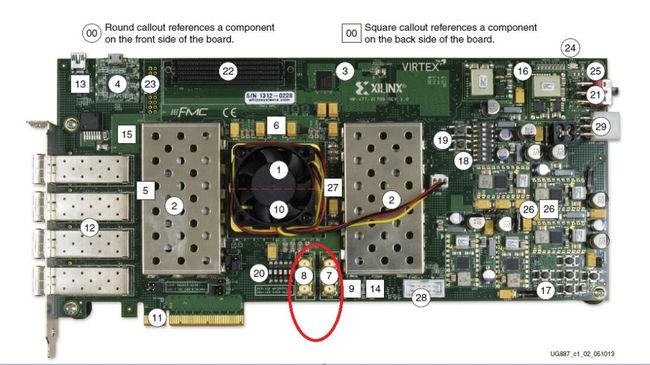

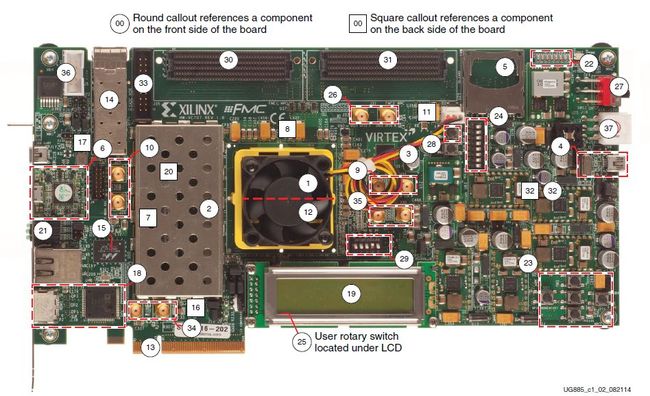

根据第一部分图5.3有关VC709板子时钟布局的介绍,给10G以太网接口提供参考时钟的SMA接口如下图VC709开发板上红色框内标记7和8两个接口,在实际上板调试过程中,需要手动用同轴电缆将两个接口连接起来。

用同轴线连接后的实物图如下所示:

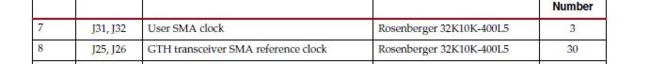

查看用户手册,可以发现7和8接口描述如下。

查看VC709原理图,可以发现对应690T FPGA管脚的参考时钟如下图:

另外,在Xilinx系列开发板中,VC707板子也具有10G的以太网接口,使用方法与VC709相同。

在VC707板子上,需要用同轴线连接的管脚是上图中的9和10。

VC709板子上VC707板子上与10G接口相关的FPGA管脚对比图如下,从图中可以看出,VC709开发板可以接10G的接口数明显多于VC707开发板。

上板调试过程中遇到的问题

1、时序违例问题。

问题描述:在使用软件vivado 2016.2完成对10G以太网接口综合实现后,发现软件报告该工程有几处时序路径的建立时间无法满足,可能会出现时序错误。

查找原因:通过查看时序报告,并结合工程的实际设计了解到,出现问题的位置是10G MAC核的异步FIFO,由于此FIFO的两个时钟为异步时钟,导致软件在对其进行布局布线时无法同时满足两个时钟域的要求,因此出现建立时间报红的问题。

解决方法:由于此FIFO内的核心是一个双口RAM,此RAM本身就可以实现数据的跨时钟域传输,所以,此问题并不会出现时序错误。通过时序约束对几处时序违例的位置的时序路径进行忽略,解决该问题。

2、10G以太网接口无法接收数据的问题

问题描述:在对10G以太网接口进行上板测试时,发现此接口无法从交换机接收数据,10G EthernetPCS/PMA IP核的状态信号显示链路失同步、链路状态为低。

查找原因:由于是接口出现问题,因此使用Xilinx官方提供的专用测试接口的ibertIP核对其进行测试,发现ibert的近端PCS回环和PMA回环都可以通过测试,但是在使用外部光纤进行回环时无法通过测试,因此分析可能是光模块的问题导致10G以太网接口无法接收数据。通过查阅开发板VC709的官方手册后发现,此开发板的光模块的默认状态是关闭的,要通过代码对其进行配置才能使光模块正常工作。

解决方法:查阅手册,根据手册对光模块进行配置。再次进行测试,10G以太网接口可以接收数据,问题解决。

3、Vivado 2016.2软件BUG问题

见本公众号之前文章:[发现了vivado2016.2版本的一个BUG!](https://mp.weixin.qq.com/s?__biz=MzU1MzI4ODA5OA==&mid=2247484368&idx=1&sn=d7dc5db71d536342d7987af37edea409&chksm=fbf46b1dcc83e20b38044c48ffb7ce7585a12de342f2238fedc04ccb782d3cc59ce887676c45&token=1998245080&lang=zh_CN&scene=21#wechat_redirect)

参考文献

[1] Xilinx.ug887-2013.VC709evaluation board for the Virtex-7 FPGA user guide[S].Xilinx, 2013.

[2] Xilinx.ug885-2016.VC707evaluation board for the Virtex-7 FPGA user guide[S].Xilinx, 2016.

[3] 付新宇. 10G HIMAC协处理器关键技术研究.[D].西安电子科技大学,2018.

应用场景

VC709和VC707开发板上还有千兆的接口模式,如SGMII接口等,具体调试见本公众号之前文章:[SGMII接口调试](https://mp.weixin.qq.com/s?__biz=MzU1MzI4ODA5OA==&mid=2247484513&idx=1&sn=fcffe7e7e634a84696f5f57db47a276f&chksm=fbf46caccc83e5bacb560b203eebf2b3a0be3289c2a5367e4ff9b8b787f3a070374dcadd3922&token=1998245080&lang=zh_CN&scene=21#wechat_redirect)。同时,随着以太网接口速率的提升,10G、20G、40G甚至100G的以太网接口应用越来越广泛,具体来讲主要有两个关键的应用领域。

1、数据中心加速。

在一些数据中心采用10G或者更高速率的以太网接口加FPGA的模式,可以在数据进入到服务器之前采用硬件的方式进行快速的处理,降低服务器CPU的负荷,见本公众号之前文章:[深度 | 如何评价微软在数据中心使用 FPGA ?](https://mp.weixin.qq.com/s?__biz=MzU1MzI4ODA5OA==&mid=2247484711&idx=1&sn=aae3fa310ac314b4b6960bf2b8033811&chksm=fbf46deacc83e4fc4444ddfcb019c382827725579a3ac09cfb619e11a38e4548f7994c66a1a8&token=1998245080&lang=zh_CN&scene=21#wechat_redirect);

2、SDN/NFV

把上面的应用场景扩展一下,就可以把带有FPGA的以太网卡用来降低各种各样场景下的CPU负荷,目前较为流行的概念是SMART NIC即**智能网卡**,其核心是通过FPGA(现场可编程门阵列)协助CPU处理网络负载,编程网络接口功能,具有以下特征:

通过FPGA本地化编程支持数据面和控制面功能定制,协助CPU处理网络负载;

通常包含多个端口和内部交换机,快速转发数据并基于网络数据包、应用程序套接字等智能映射到到相关应用程序;

-

检测和管理网络流量。

Smart NIC能够提升应用程序和虚拟化性能,实现软件定义网络(SDN)和网络功能虚拟化(NFV)的诸多优势,将网络虚拟化、负载均衡和其他低级功能从服务器CPU中移除,确保为应用提供最大的处理能力。与此同时,智能网卡还能够提供分布式计算资源,使得用户可以开发自己的软件或提供接入服务,从而加速特定应用程序。

目前业界提供基于FPGA的Smart NIC的厂商包括Accolade、BittWare、Enyx、Ethernity、Napatech、Netcope、Reflex CES、Silicom和Solarflare,通常集成自Intel或Xilinx的FPGA来实现。此外,Broadcom,Cavium,Intel,Kalray,Mellanox,Netronome,Silicom和SolidRun均可提供基于处理器的Smart NIC,使用带有集成处理器内核或FPGA的处理器或智能I/O处理器;亚马逊和谷歌已经开发了Smart NIC ASIC。

后期我们还将继续推出相关的介绍。