Vivado使用技巧(1):使用Tcl在Shell中进行FPGA开发

概述

通常我们使用的是Vivado IDE进行FPGA的开发,IDE提供了图形化的界面和自动化管理方案,我们只需要点击几个按钮就会得到结果。有时候还会用到另外一种开发方式:在Vivado Tcl Shell中使用Tcl命令的方式控制开发设计流程。使用Tcl的好处是每一个命令都有一个具体的操作,我们可以详细的控制设计过程中的每一步,设计更加灵活,也更有效率。

通常的情况下都会根据需求事先编辑好一个完整的Tcl脚本,直接运行即可得到想要的结果。本文将会保留一个设计过程的每一步(实际使用时不会用到这么多的步骤)。以下Tcl命令对于所有的Vivado版本都是通用的。进行操作前需要准备好已经设计好的Verilog文件和约束XDC文件,并放在一个固定目录下。本文参考了Xilinx官方文档与《Xilinx FPGA权威设计指南》这本书中的内容。

一.准备

1.1 在开始菜单的Xilinx工具集中找到“Vivado xxxx.x Tcl Shell”,xxxx.x代表安装的Vivado版本号。在Shell中先将当前环境指向设计源文件的目录(注意路径中斜线方向是左斜杠):

Vivado% cd C:/Users/GodWa/Desktop/SDK_Test/gate1.2 指定一个设计文件的输出路径,所有生成的报告、结果文件等都将存放在该路径文件夹下

Vivado% set outputDir ./gate/gate_Created_Data/top_output1.3 生成输出路径的目标文件夹

Vivado% file mkdir $outputDir1.4 读取设计的Verilog源文件和XDC约束文件

Vivado% read_verilog top.v

Vivado% read_xdc test.xdc二.综合

2.1 对设计进行综合,需要指定目标FPGA器件型号。接下来的每一步都会反馈一个结果,如果发生错误会有警告、错误提示,可以根据提示修改源文件的程序。

Vivado% synth_design -top top -part xc7a100tcsg324-12.2 综合后写入一个检查点。

Vivado% write_checkpoint -force $outputDir/post_synth2.3 生成综合后的时序报告。

Vivado% report_timing_summary -file $outputDir/post_synth_timing_summary.rpt2.4 生成综合后的功耗报告。

Vivado% report_power -file $outputDir/post_synth_power.rpt2.5 对设计进行优化,优化操作一般都需要指定一些参数。

Vivado% opt_design2.6 对功耗进行优化。

Vivado% power_opt_design三.实现

3.1 对设计进行布局。

Vivado% place_design3.2 对布局后的设计进行逻辑物理优化。

Vivado% phys_opt_design3.3布局后写入一个设计检查点。

Vivado% write_checkpoint -force $outputDir/post_place3.4生成布局后的时序总结报告

Vivado% report_timing_summary -file $outputDir/post_place_timing_summary.rpt3.5对设计进行布线。

Vivado% route_design3.6布线后写入一个检查点。

Vivado% write_checkpoint -force $outputDir/post_route3.7 生成布线后的时序总结报告。

Vivado% report_timing_summary -file $outputDir/post_route_timing_summary.rpt3.8 生成布线后的时序报告。

Vivado% report_timming -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt3.9 生成布线后的利用率报告。

Vivado% report_clock_utilization -file $outputDir/post_route_util.rpt3.10 生成布线后的功耗报告。

Vivado% report_power -file $outputDir/post_imp_drc.rpt3.11 生成布线后的drc报告。

Vivado% report_drc -file $outputDir/post_impl_drc.rpt3.12 写Verilog文件。

Vivado% write_verilog -force $outputDir/top_impl_netlist.v3.13 写xdc文件。

Vivado% write_xdc -no_fixed_only -force $outputDir/top_impl.xdc四.下载

4.1 生成bit流文件。

Vivado% write_bitstream -force $outputDir/top.bit4.2 打开硬件管理器。

Vivado% open_hw4.3 连接硬件。

Vivado% connect_hw_server4.4 打开硬件目标。

Vivado% open_hw_target4.5 分配编程文件。

Vivado% set_property PROGRAM.FILE{bit文件地址} [lindex [get_hw_devices]0]4.6 下载。

program_hw_devices [lindex[get_hw_devices]0] 观察就会发现与设计步骤相关的命令都会有一个“design”后缀,与生成报告相关的命令都会有一个“report”前缀。文本在使用Tcl命令时几乎没有加任何的属性和参数,其实使用Tcl进行FPGA开发的好处就是可以通过添加和修改属性的方式控制设计过程中的每一步。

本文使用的Tcl命令只是Shell中的命令。在Vivado IDE中的Tcl控制台,还可以使用一些与图形化界面配套的命令,这些命令是无法在Shell中使用的。在IDE界面中使用Tcl命令时软件会对命令做出比较详细的补全和提示工作,使用起来也不会感觉到困难。

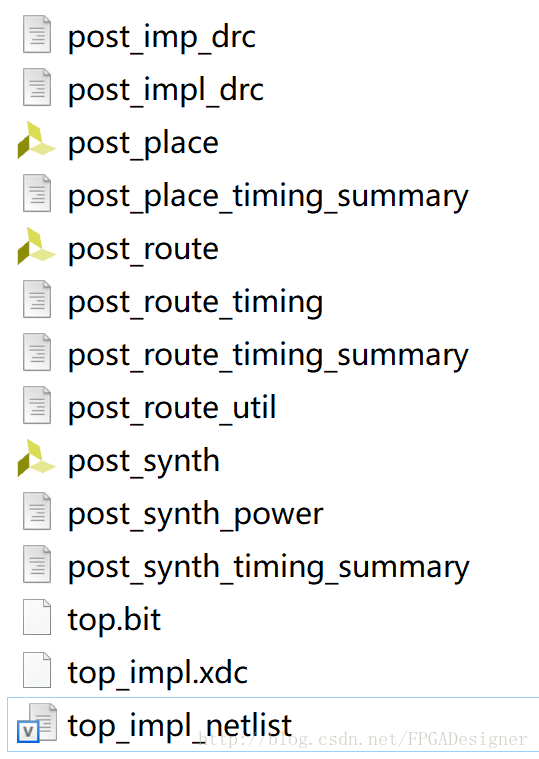

打开生成文件的文件夹,将看到设计过程中的所有文件,这些文件是可以用Vivado IDE打开查看的:

Tcl作为一种脚本语言而网上目前可以找到的学习资料很少。与Vivado操作有关的Tcl其实都分布在Xilinx介绍Vivado的官方文档中。