HLS简介

HLS(High Level Synthesis)即高层次综合,不同于以往的FPGA逻辑开发,是用HDL编写的,开发周期长、难度大。而HLS可以使用C,C++,SystemC以及OPenCL等编写,通过高层次综合,可以把软件代码转化为硬件描述语言,可以大大加快开发速度,使软件工程师也可以编写硬件语言。

HLS OpenCV简介

OpenCV是开源的图像处理和计算机视觉库,它支持多种操作系统、包含多种计算机语言的接口。HLS opencv是HLS里带有的可综合成HDL的OpenCV库函数,换句话说,由于HDL和C++的特性(例如动态内存分配不可以综合成HDL)并不是所有的OpenCV库函数都可以综合成HDL,当然目前Xilinx提供了较多的HLS OpenCV库函数,可以满足一定的需求,相信以后会越来越多的。

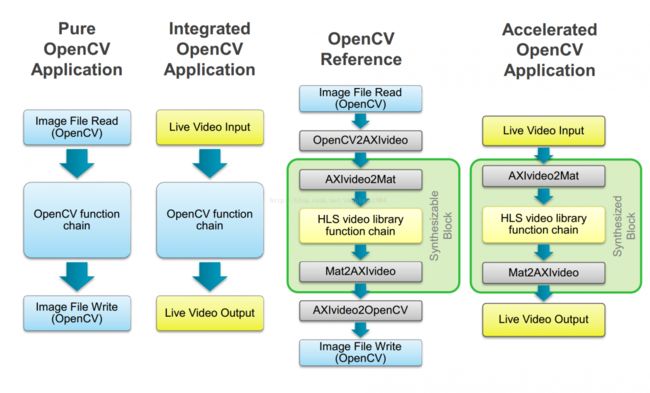

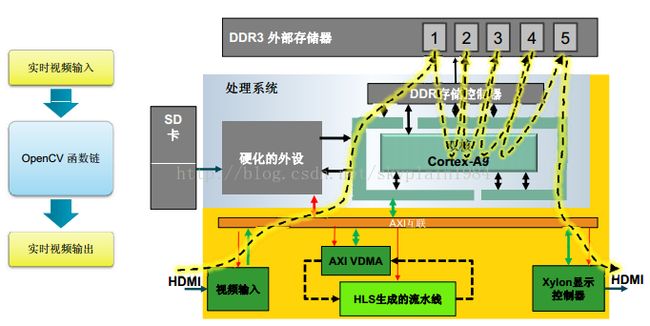

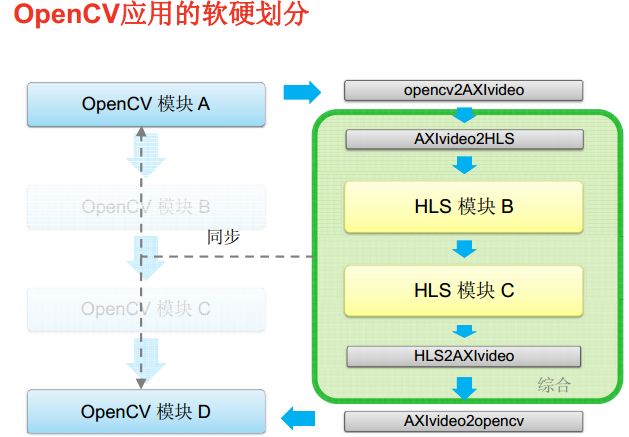

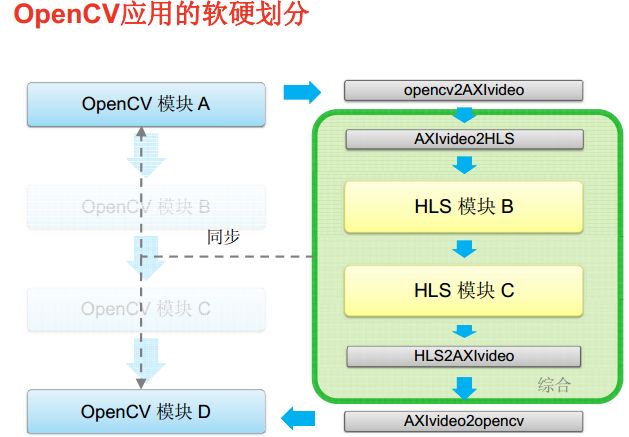

HLS加速模型

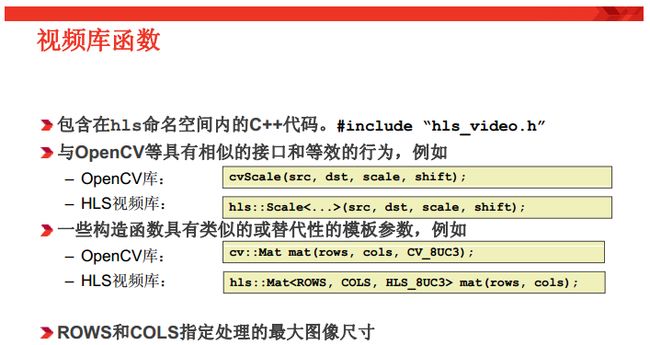

HLS OpenCV和OpenCV有着相似的书写风格

OpenCV library : cvScale(src, dst, scale, shift);

HLS video library : hls::Scale<…>(src, dst, scale, shift);

加速的opencv应用

开发注意

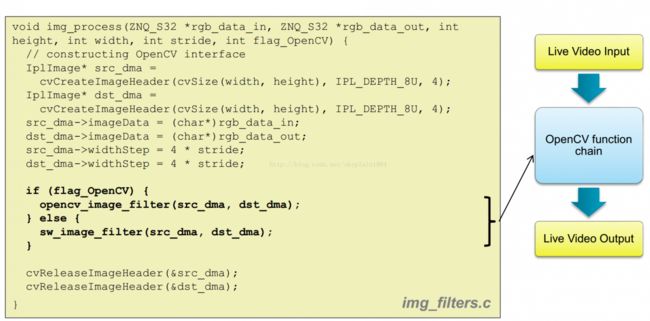

实例

#ifndef _IMAGE_CORE_H_

#define _IMAGE_CORE_H_

#include"hls_video.h" //这里调用可以综合的视频库

// maximum image size

#define MAX_WIDTH 1920

#define MAX_HEIGHT 1080

// I/O Image Settings

#define INPUT_IMAGE "test_1080p.jpg"

#define OUTPUT_IMAGE "result_1080p.jpg"

#define OUTPUT_IMAGE_GOLDEN "result_1080p_golden.jpg"

// typedef video library core structures

typedef hls::stream

typedef hls::stream

typedef hls::Mat

// top level function for HW synthesis

void image_core(AXI_STREAM_IN& src_axi, AXI_STREAM_OUT& dst_axi, int rows, int cols);

#endif

#include "image_core.h"

void image_core(AXI_STREAM_IN& input, AXI_STREAM_OUT& output, int rows, int cols) {

#pragma HLS RESOURCE variable=input core=AXI4Stream metadata="-bus_bundle INPUT_STREAM"

#pragma HLS RESOURCE variable=output core=AXI4Stream metadata="-bus_bundle OUTPUT_STREAM"

#pragma HLS INTERFACE ap_none port=cols

#pragma HLS INTERFACE ap_none port=rows

//AP_CONTROL_BUS_AXI(CONTROL_BUS);

//set_directive_interface -mode ap_ctrl_none hls_sobel

#pragma HLS interface ap_ctrl_none port=return

RGB_IMAGE img_0(rows, cols);

RGB_IMAGE img_1(rows, cols);

#pragma HLS DATAFLOW // must use data flow to stream the data

hls::AXIvideo2Mat(input, img_0); //read video stream by frames

hls::Sobel<1,0,3>(img_0, img_1);//use Hls Sobel

hls::Mat2AXIvideo(img_1, output); //write the frames to video stream

}

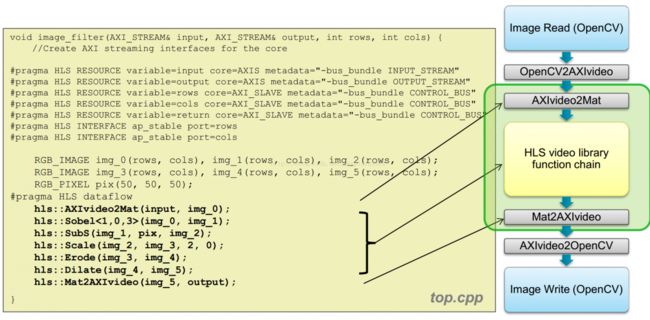

将“input”指定为以 “ S INPUT_STREAM” 命名的AXI4 Stream

#pragma HLS RESOURCE variable=input core=AXIS metadata="-bus_bundle INPUT_STREAM"

将控制接口分配到AXI4 Lite接口

#pragma HLS RESOURCE variable=return core=AXI_SLAVE metadata="-bus_bundle CONTROL_BUS"

指定“rows”可通过AXI4-Lite接口进行访问

#pragma HLS RESOURCE variable=rows core=AXI_SLAVE metadata="-bus_bundle CONTROL_BUS"

声明在函数执行过程中 “rows”不会改变

#pragma HLS INTERFACE ap_stable port=rows

启用数据流优化

#pragma HLS dataflow

C综合

点击Solution -> Run C Synthesis -> Active Solution

运行test.cpp C仿真测试

#include "image_core.h"

#include "opencv/cv.h"

#include "opencv/cxcore.h"

#include "opencv/highgui.h"

#include "hls_opencv.h"

int main (int argc, char** argv) {

IplImage* src = cvLoadImage(INPUT_IMAGE);

IplImage* dst = cvCreateImage(cvGetSize(src), src->depth, src->nChannels);

AXI_STREAM_IN src_axi;

AXI_STREAM_OUT dst_axi;

IplImage2AXIvideo(src, src_axi); //将图像转为视频流结构

image_core(src_axi, dst_axi, src->height, src->width);

AXIvideo2IplImage(dst_axi, dst);

cvSaveImage(OUTPUT_IMAGE, dst);

cvReleaseImage(&src);

cvReleaseImage(&dst);

}

点击Project -> Run C simulation,弹出的对话框点确定即可。

文章来源:skyplain1984的博客

- 嵌入式开发

- HLS

- Zynq

- FPGA菜鸟's blog

- 要发表评论,请先登录 或 注册

- 1360 次点击