8、存储器

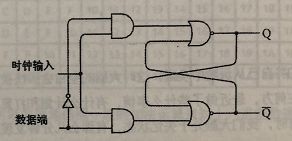

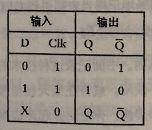

回忆一下,前面所学习到的D型电平触发器,它可以保存1个bit的信息。下面再来看看它的电路图以及真值表。

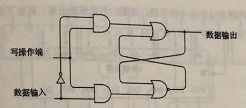

现在我们对输入端和输出端重新命名,如下所示:

现在Q的输出被命令为数据输出,时钟输入端被命名为写操作端。

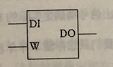

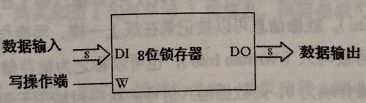

写操作端的信号同样使得数据输入信号被写入,也可以称之为被存储到电路中。一般情况下,写操作端为0,则数据输入信号的状态对输出无影响。而当我们想把数据输入信号在触发器中时,可以把写入信号应先置1后置0。这种类型的电路也被称之为锁存器,因为它存储进去的数据好像被锁住了一样。下面给出该锁存器的简化框图:

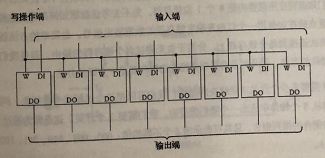

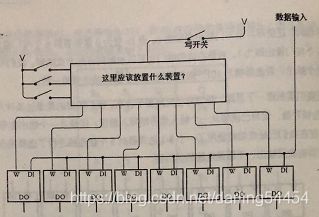

我们很容易想到,如何把一个1bit的锁存器组织成多位存储器,所要做的就是把所有锁存器的写操作端信号连接在到系统中,如下所示:

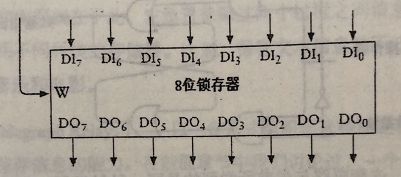

图中显示的8位锁存器,其输入和输出各有8个,另外还有一个写操作端。在非工作状态下,写操作端为0。如果想把一个8位二进制数存储在锁存器,则首先把写操作端置1。我们同样可以把这个锁存器用框图的形式表现出来,如下所示:

到此,我们就已经实现了一个8位的锁存器,该锁存器一次存储8个位的数据。

现在假设有这么一个需求:

数据端输入只有1位,数据的输入保存到锁存器里面,锁存在哪个位由开关来控制,最后同时把该位数据输出。

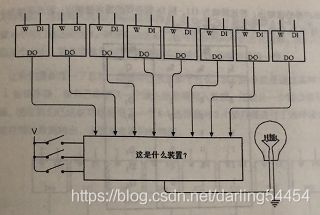

现在先来看一下输出的需求,需要添加一个额外装置,这个额外装置由一个灯泡和3个开关组成,通过开关来选择某个输出端的状态表现在灯泡上。

这种装置的框图,如下所示:

这个“额外装置“就是上图的神秘盒子,它顶部有8个输入端,左侧也有3个输入端。通过这3个开关的闭合和断开,对顶部的输入进行8选1操作,输出结果被传递到其底部连接的灯泡。

这个神秘盒子,它其实就是一个8-1数据选择器,在前面实现加法器的电路中,已经有了解到类型的电路,那时候是一个2-1选择器,用来选择加数是来自于面板的开关输入或者是存储器的输入。

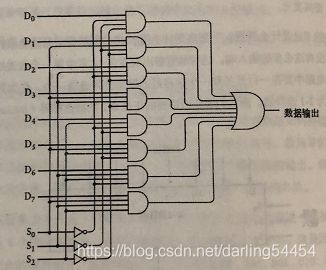

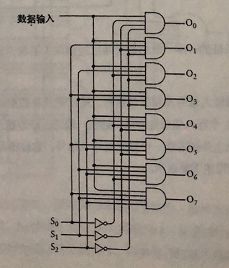

8-1数据选择器的主要组成部件为:三个反向器、八个4端口输入与门、一个8端口输出或门,系统的组成结构如下图所示:

这个电路看上去线路密布,看个例子来理解一下它是如何工作的。

假设S2初始化等于1,S1初始化为0,S0初始化为1。从顶部往下第6个与门输入则为:S0,S1反,S2,也就是值(1,1,1)。

而其他的与门的这3项输入都和第6个与门不尽相同(不全1),则使得其他与门的输出全部为0。

若D5为0,那么意味着第六个与门的输入为0,那数据输出为0,反之输出为1。

因此可以得出结论,当选择端101的时候,数据输出端与D5的输出保持一致。

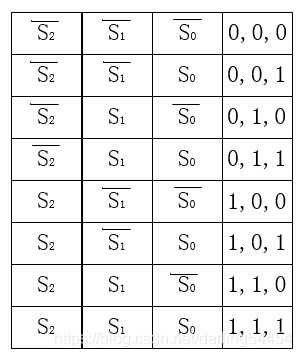

下面给出S0,S1,S2分别对应到与门的输入,要让与门的输出不为0,那么这3个输入都应该为1。

假如说,要让第一个与门的3个输入都为1,那么S0=0, S1=0, S2=0,此时与门的输出则由D0的值来决定。

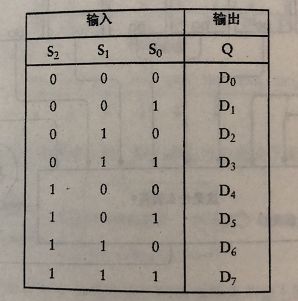

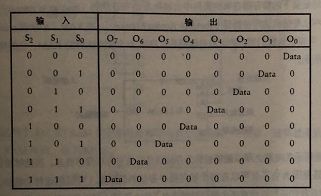

8-1数据选择器的真值表如下所示:

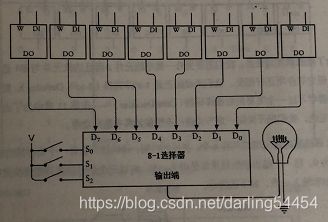

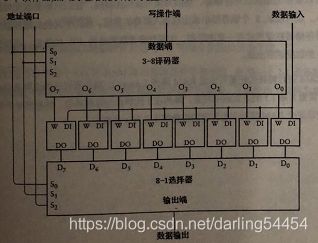

好的,到此了解了8-1数据选择器的工作原理了,把前面电路图的神秘盒子给替换进去,则如下图所示:

到此,再来看一下输入的需求。锁存器的输入有数据输入端和写操作端。我们可以把所有的数据输入端连接在一起,但是8个写操作端不可以连接在一起,因为需要单独的操作锁存器里面的某个位。系统的结构可用下图表示:

这个神秘盒子,它的功能正好和选择器相反。选择器是8个数据端的输入,通过3个开关来选择其中一端输出。而这个装置是3个开关输入来输出8个信号,并且只有一个输出信号的值等于1,该信号用来作为锁存器写操作端的输入,因此用来控制是否生效写操作。这个装置叫做“3-8译码器”。

电路图如下所示:

我们也举个例子来说明该电路图的实现,从上往下数的第六个与门,它的输入是S0,S1反,S2。没有任何一个与门具备和它相同的三个输入。在这种情况下,如果选择输入端为101,则O5输出为1,其他与门的输出都是为0。输出端又连接到锁存器的写操作端,此时则只有O5所连接的锁存器开启了写操作,它锁存器的输入信号没有影响。因此,译码器的真值表如下所示:

现在,我们把8位锁存器,以及8-1选择器,和3-8译码器连接在一起,形成下面的整个系统电路:

这里需要注意的是,译码器和选择器具有相同的选择信号,在上图中把这三个信号一起被称之为地址端口。地址的作用就像是我们平时使用的邮箱号,长度为三位的地址决定了8个锁存器中哪一个将被引用。在3-8译码器的输入端,地址起到了决定哪些锁存器可以被写操作端的信号触发来保存数据的作用。在输出端,8-1选择器通过地址来选择8个锁存器中的一个,最后将被输出。

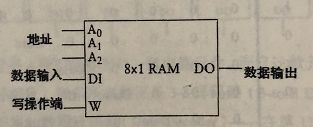

这种配置的锁存器在有的资料里面被称之为读/写存储器(read/write memory),但是更普通的叫法是随机访问存储器(random access memory),或RAM。可以认为我们讨论的这种存储器是可存储8个独立比特的RAM,它的简化结构如下所示:

将RAM进行特殊的配置可形成RAM阵列(Array),我们所讨论的这种RAM阵列以8x1的方式组织起来。阵列以1比特作为存储单位,共存储了8个单位的数据。

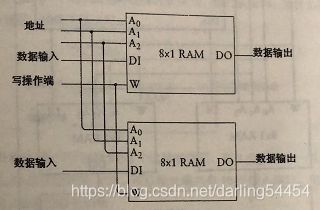

RAM阵列的组合形式多种多样。比如我们可以通过共享地址的方式可以把两个8x1的RAM阵列连接起来,如下图所示:

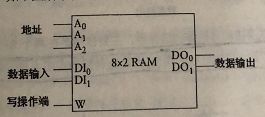

把这两个8x1的RAM阵列的地址和输出都分别看成是一个整理,就可以得到了一个8x2的RAM阵列,如下所示:

这个RAM阵列可存储的单位仍然是8个,但是每个的位宽是2位。

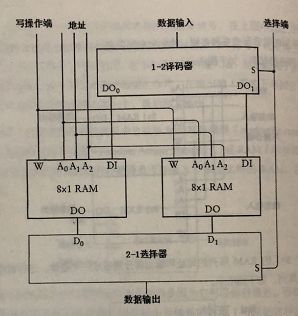

我们还可以把这两个8x1的RAM阵列看做是两个锁存器,使用一个2-1选择器和一个1-2译码器就可以把它们按照单个锁存器连接方式进行集成,下面给出这种方案的电路图。

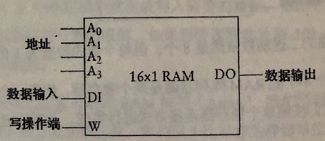

“选择”端之所以连接到译码器和选择器,主要作用是在两个8x1的RAM阵列中选择一个,本质上它扮演了第四根地址线的角色。因此这种结构实质上是一种16x1的RAM阵列。如下图所示:

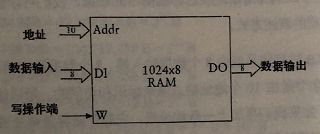

既然可以搭建小型RAM阵列,那当然也可以搭建一个大型的RAM阵列。如下所示,一个1024 x 8的RAM阵列:

该阵列有10个地址端口,8个数据输入以及8个数据输出端口,它的容量1024字节。