02-ZYNQ学习(逻辑篇)之FPGA LED控制实验

一、创建工程

1. 启动 Vivado 2015.4 开发环境(在开始菜单中选择 Xilinx Design Tools->Vivado 2015.4->Vivado 2015.4。或者双击桌面的 Vivado 2015.4 的图标直接打开软件。

2. 在 Vivado 2015.4 开发环境里双击 Create New Project 的图标。

3. 弹出一个 Vivado 的工程向导,点击 Next 按钮。

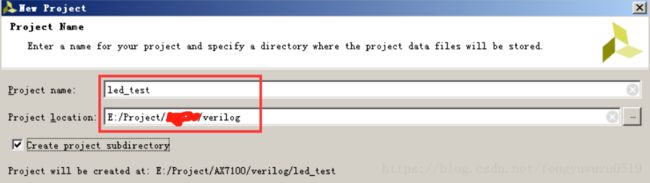

4. 在弹出的对话框中输入工程名和工程存放的目录,我们这里取一个 led_test 的工程名。

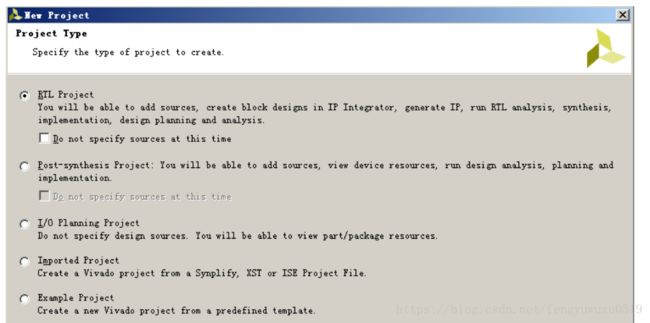

5. 在下面的对话框中默认选择RTL Project, 因为我们这里使用verilog行为描述语言来编程。下面的 Do not specify source at this time 的勾也可以打上。如果不打上,下一步会进入添加 source file 界面.

6. 进入添加 source file 界面,这里先不添加任何设计文件。点击 Next

7. 提示是否添加已有的配置好的 IP,这里我们没有,就不添加。

8. 提示是否添加已有的约束文件,这里约束文件我们也没有设计好,也不添加。

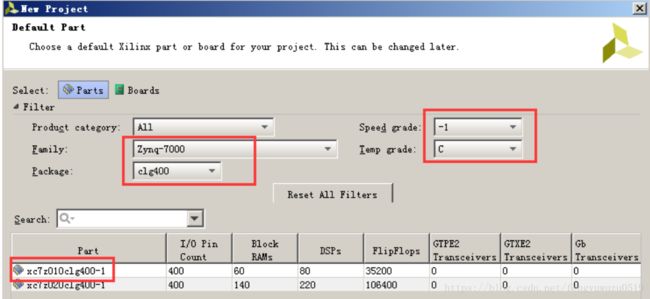

9. 在接下杢癿对话框选择所用癿 FPGA 器件,以及迕行一些配置。FPGA 芯片型号一定要跟开发板上癿型号一致,首先在 Family 栉里选择Zynq-7000, Speed grade栉选择-1, Temp grade选择 C, 在 Package 选择 clg400, 如果是7020 开发板选列表中选择 xc7z020clg400-1。

10. 再次确认一下板子型号有没有选对, 没有问题再点击“Finish”完成工程创建。

二、编写 verilog 代码

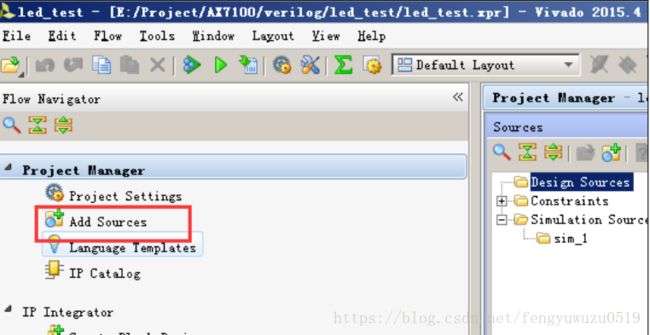

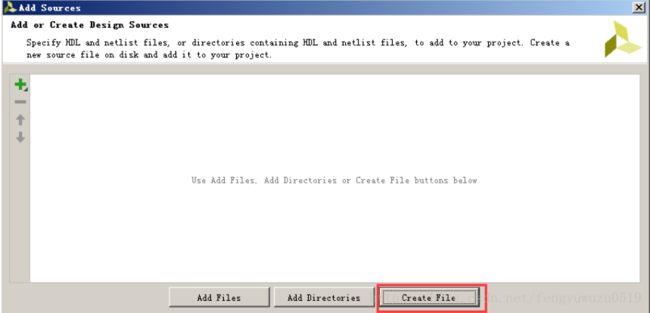

1. 点击 Project Manager 下的 Add Sources 图标(或者使用快捷键 Alt+A)。

2. 选择 Add or create design sources 选项,点击 Next。

3. 点击 Add Files 可以一个个添加源文件,点击 AddDirectories 可以按目录添加源文件。因为现在我们还没有设计程序,这里要点击 Create File 按钮。

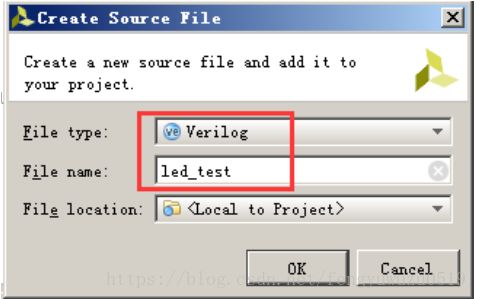

在弹出的对话框里选择 File type 是 verilog, File name 为 led_test, 点击 OK 按钮。

4.点击“Finish”完成。

向导会提示您定义 I/O 的端口,这里我们可以不定义,后面自己在程序中编写就可以。

这时在 Project Manager 界面下的 Design Sources 里已经有了一个 led_test.v 文件, 并且自动成为项目的 Top 模块了。

5. 接下去我们来编写 led_test.v 的程序

`timescale 1ns / 1ps

module led(

input sys_clk,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk)

begin

if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule三、添加 XDC 管脚约束文件

和 ISE 软件不同, Vivado 使用的约束文件格式为 xdc 文件。xdc 文件里主要是完成管脚的约束,时钟的约束, 以及组的约束。这里我们需要对 led_test.v 程序中的输入输出端口分配到 FPGA的真实管脚上, 这需要准备一个 FPGA 的引脚绑定文件.xdc 并添加到工程中。

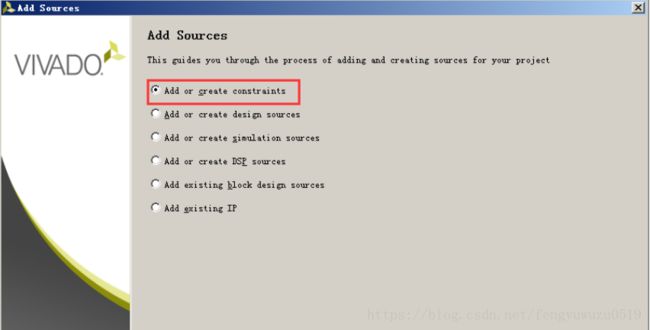

1. 点击 Project Manager 下的 Add Sources 图标。

2. 选择 Add or create constraints 选项,点击 Next。

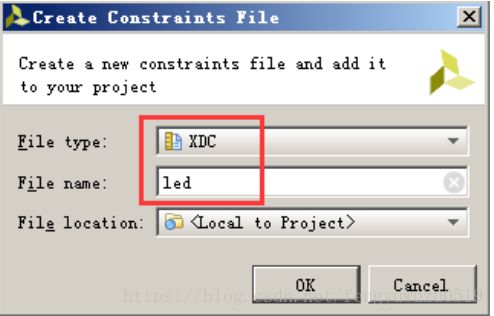

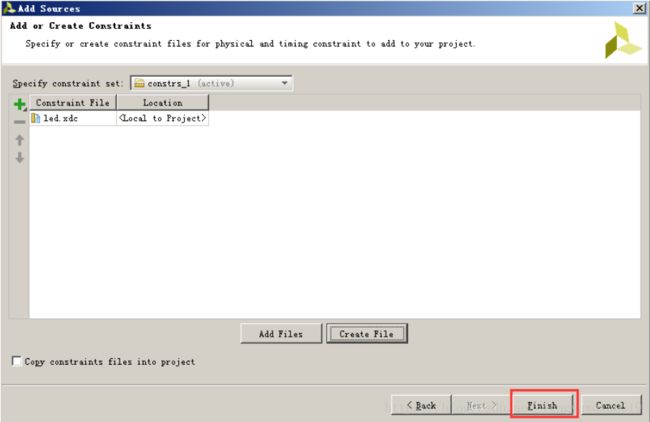

3. 点击 Create File 按钮。

在弹出的对话框里选择 File type 是 XDC, File name 为 led, 点击 OK 按钮。

4.点击“Finish”完成。

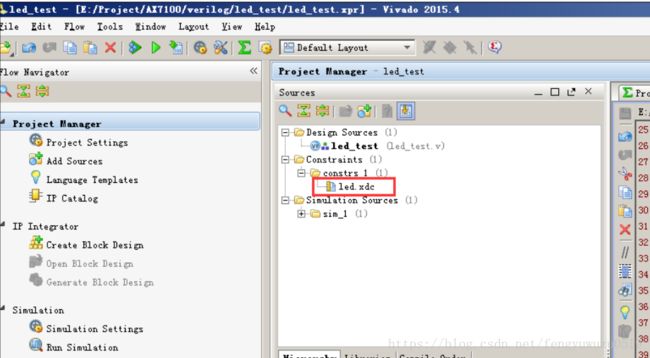

这时在 Project Manager 界面下的 Constraints 目录的 constrs_1 目录下已经有了一个led.xdc 文件。

5. 双击打开这个 led.xdc 文件,在这个文件里添加以下的引脚定义。

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN M14 [get_ports {led[0]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]

set_property PACKAGE_PIN K16 [get_ports {led[2]}]

set_property PACKAGE_PIN J16 [get_ports {led[3]}]set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”]

电平信号的约束如下:

set_property IOSTANDARD "电压" [get_ports “端口名称”]

返里需要注意文字的大小写,端口名称是数组的话用{ }刮起来,端口名称必项和源代码中的名字一致,且端口名字不能和关键字一样。完成后选择菜单 File->Save all files 保存所有文件。

四、编译

点击 Run Synthesis,即可开始综合幵生成网表文件:

右上角可以看到软件正在 Running:

在 Tcl Console 窗口或者 Messages 窗口可以看到一些状态信息。

综合完成后,会弹出返样一个提示小窗口。可以点返里的 Run Implementation 开始布局布线:

布线完成后会弹出返样一个提示小窗口。可以点返里癿 generate bit file 即可生成 bit 文件。

Bit 文件生成完成后,我们可以打开 Project Summary 页面癿 Table 来查看板子上实际资源的使用情况,因为我们这里的 led_test 程序比较简单,只用到了四个资源: LUT(查找表),FF(Flip Flop 寄存器), IO(管脚)和 BUFG(时钟 Buffer)。

五、下载和调试

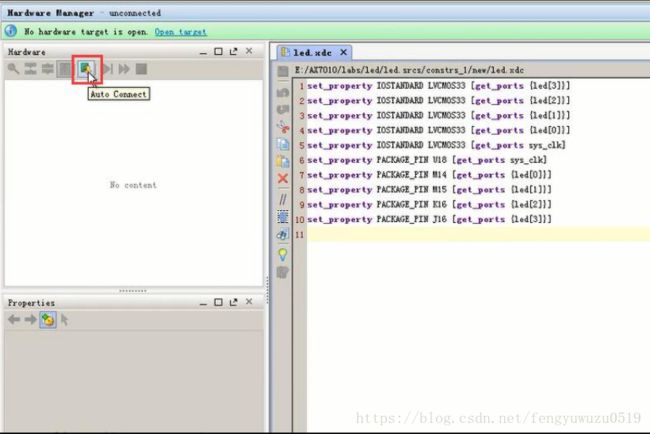

经过前面的编译并生成了 Bit 文件,我们可以把 bit 文件下载的 ZYNQ 芯片中,看一下 LED实际运行的效果。下载和调试之前先连接硬件,把 JTAG 下载器和开发板连接,然后开发板上电。再在 Vivado 软件界面上点击 Hardware Manager:

点击 Auto Connect 图标。

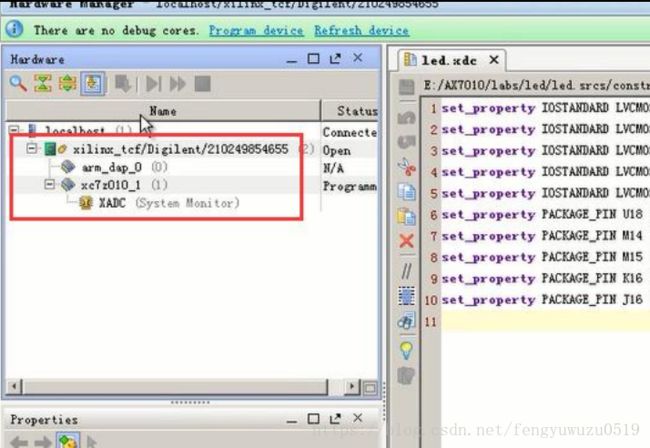

在 hardware 界面下会显示 xilinx JTAG 下面有两个图标,一个是 Arm, 另一个是 FPGA xc7z020。说明 JTAG 连接已经建立。

这里我们只要下载 FPGA,右键选择 xc7z010_1( xc7z020_1),在弹出的选项里选择 Program Device 项。

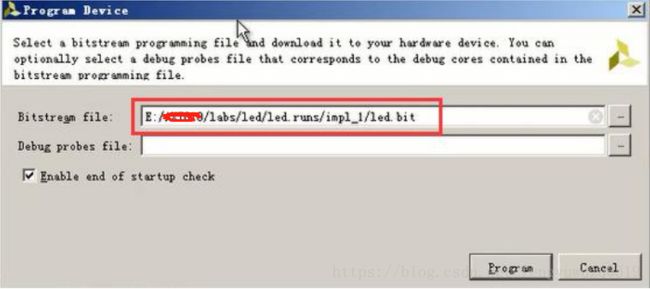

在弹出的 Program Device 对话框中,软件会自动选择 led 项目生成的 bit 文件,点击Program 按钮烧写 FPGA。

烧写完成后 xc7z010_1 或 xc7z020_1 的状态会发成 Programmed, 返时我们可以看到开发板上癿四个 LED 灯已经在做翻转动作了。