IBIS 模型简介

IBIS(Input/Output Buffer Information Specification)模型是一种基于V/I曲线的对I/O BUFFER快速准确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入 负载等参数,非常适合做振荡和串扰等高频效应的计算与仿真。

IBIS规范最初由一个被称为IBIS开放论坛的工业组织编写,这个组织是由一些EDA厂商、计算机制造商、半导体厂商和大学组成的。IBIS的版本发布 情况为:1993年4月第一次推出Version1.0版,同年6月经修改后发布了Version1.1版,1994年6月在San Diego通过了Version2.0版,同年12月升级为Version2.1版,1995年12 月其Version2.1版成为ANSI/EIA-656标准,1997年6月发布了Version3.0版,同年9月被接纳为IEC 62012-1 标准,1998年升级为Version3.1版,1999年1月推出了当前最新的版本Version3.2版。

IBIS本身只是一种文件格式,它说明在一标准的IBIS文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些被记录的参数如何使用,这些参数需要由使用IBIS模型的仿真工具来读取。欲使用IBIS进行实际的仿真,需要先完成以下四件工作:

- 获取有关芯片驱动器和接收器的原始信息源;

- 获取一种将原始数据转换为IBIS格式的方法;

- 提供用于仿真的可被计算机识别的布局布线信息;

- 提供一种能够读取IBIS和布局布线格式并能够进行分析计算的软件工具。

IBIS是一种简单直观的文件格式,很适合用于类似于Spice(但不是Spice,因为IBIS文件格式不能直接被Spice工具读取)的电路仿真工 具。它提供驱动器和接收器的行为描述,但不泄漏电路内部构造的知识产权细节。换句话说,销售商可以用IBIS模型来说明它们最新的门级设计工作,而不会给 其竞争对手透露过多的产品信息。并且,因为IBIS是一个简单的模型,当做简单的带负载仿真时,比相应的全Spice三极管级模型仿真要节省 10~15倍的计算量。

IBIS提供两条完整的V-I曲线分别代表驱动器为高电平和低电平状态,以及在确定的转换速度下状态转换的曲线。V-I曲线的作用在于为IBIS提供保护二极管、TTL图腾柱驱动源和射极跟随输出等非线性效应的建模能力。

由上可知,IBIS模型的优点可以概括为:

- 在I/O非线性方面能够提供准确的模型,同时考虑了封装的寄生参数与ESD结构;

- 提供比结构化的方法更快的仿真速度;

- 可用于系统板级或多板信号完整性分析仿真。可用IBIS模型分析的信号完整性问题包括:串扰、反射、振荡、上冲、下冲、不匹配阻抗、传输 线分析、拓扑结构分析。IBIS尤其能够对高速振荡和串扰进行准确精细的仿真,它可用于检测最坏情况的上升时间条件下的信号行为及一些用物理测试无法解决 的情况;

- 模型可以免费从半导体厂商处获取,用户无需对模型付额外开销;

- 兼容工业界广泛的仿真平台。

当然,IBIS不是完美的,它也存在以下缺点:

- 许多芯片厂商缺乏对IBIS模型的支持。而缺乏IBIS模型,IBIS工具就无法工作。虽然IBIS文件可以手工创建或通过Spice模型自动转换,但是如果无法从厂家得到最小上升时间参数,任何转换工具都无能为力。

- IBIS不能理想地处理上升时间受控的驱动器类型的电路,特别是那些包含复杂反馈的电路;

- IBIS缺乏对地弹噪声的建模能力。IBIS模型2.1版包含了描述不同管脚组合的互感,从这里可以提取一些非常有用的地弹信息。它不工作的原因在于建模方式,当输出由高电平向低电平跳变时,大的地弹电压可以改变输出驱动器的行为。

IBIS模型采用I/V和V/T表的形式来描述数字集成电路I/O单元和引脚的特性。由于IBIS模型无需描述I/O 单元的内部设计和晶体管制造参数,因而得到了半导体厂商的欢迎和支持。现在各主要的数字集成电路制造商都能够在提供芯片的同时提供相应的IBIS模型。

IBIS模型的分析精度主要取决于I/V和V/T表的数据点数和数据的精确度。由于基于IBIS模型的PCB板级仿真采用查表计算,因而计算量较小,通常只有相应的SPICE模型的1/10到1/100。

采用SPICE,产品推向市场的时间取决于获得模型,得到仿真结果的时间;在IBIS中,主要是从SPICE仿真界果中建立模型。换句话说, IBIS模型能够很容易的验证产品测试结果(并且,如果有必要产生新的模型)。如果同样进行测量和模型验证的话,IBIS模型能够同SPICE具有同样的 精度。IBIS模型提供的信息需要I/O传输特性、而不是内部电路的信息。

IBIS是为了满足信号完整性(SI)仿真的需要,其结果是IBIS模型具有信号完整性(signal integrity)分析所需要的信息,如在不同的负载下信号上升/下降时间。由于提取的水平如此之高,所以模型不能够很容易的调整大小,但是对于信号完 整性(SI)的应用不成问题。

IBIS是为了满足信号完整性(SI)仿真的需要,其结果是IBIS模型具有信号完整性(signal integrity)分析所需要的信息,如在不同的负载下信号上升/下降时间。由于提取的水平如此之高,所以模型不能够很容易的调整大小,但是对于信号完 整性(SI)的应用不成问题。

IBIS模型介绍

1、IBIS模型

随着数字系统性能的不断提升,信号输出的转换速度也越来越快,在信号完整性分析中,不能简单的认为这些高速转换的信号是纯粹的数字信号,还必须考虑到它们 的模拟行为。为了在PCB进行生产前进行精确的信号完整性仿真并解决设计中存在的问题,要求建立能描述器件I/O特性的模型。这样,Intel最初提出了 IBIS的概念,IBIS就是I/O BufferInformation Specification的缩写。

为了制定统一的IBIS格式,EDA公司、IC供应商和最终用户成立了一个IBIS格式制定委员会,IBIS公开论坛也随之诞生。在1993年,格式制定 委员会推出了IBIS的第一个标准Version 1.0,以后不断对其进行修订,现在的版本是1999年公布的Version 3.2, 这一标准已经得到了EIA的认可,被定义为ANSI/EIA-656-A标准。每一个新的版本都会加入一些新的内容,但这些新内容都只是一个IBIS模型 文件中的可选项目而不是必须项目,这就保证了IBIS模型的向后兼容性能。

现在,已经有几十个EDA公司成为IBIS公开论坛的成员,支持IBIS的EDA公司提供不同器件的IBIS模型以及软件仿真工具。有越来越多的半导体厂商开始提供自己产品的IBIS模型。

随着数字系统性能的不断提升,信号输出的转换速度也越来越快,在信号完整性分析中,不能简单的认为这些高速转换的信号是纯粹的数字信号,还必须考虑到它们 的模拟行为。为了在PCB进行生产前进行精确的信号完整性仿真并解决设计中存在的问题,要求建立能描述器件I/O特性的模型。这样,Intel最初提出了 IBIS的概念,IBIS就是I/O BufferInformation Specification的缩写。

为了制定统一的IBIS格式,EDA公司、IC供应商和最终用户成立了一个IBIS格式制定委员会,IBIS公开论坛也随之诞生。在1993年,格式制定 委员会推出了IBIS的第一个标准Version 1.0,以后不断对其进行修订,现在的版本是1999年公布的Version 3.2, 这一标准已经得到了EIA的认可,被定义为ANSI/EIA-656-A标准。每一个新的版本都会加入一些新的内容,但这些新内容都只是一个IBIS模型 文件中的可选项目而不是必须项目,这就保证了IBIS模型的向后兼容性能。

现在,已经有几十个EDA公司成为IBIS公开论坛的成员,支持IBIS的EDA公司提供不同器件的IBIS模型以及软件仿真工具。有越来越多的半导体厂商开始提供自己产品的IBIS模型。

2、IBIS与SPICE的比较

SPICE作为一种通用的电路模拟语言,最早由加州大学伯克利分校发明。SPICE模型是对电路中实际的物理结构进行描述。由于其精确性和多功能性,已经 成为电子电路模拟的标准语言。SPICE模型目前有两个主要的版本:HSPICE和PSPICE,HSPICE主要应用于集成电路设计,而PSPICE主 要应用于PCB板和系统级的设计。

采用SPICE模型在PCB板级进行SI分析时,需要集成电路设计者和制造商提供能详细准确的描述集成电路I/O单元子电路的SPICE模型和半导体特性 的制造参数。由于这些资料通常都属于设计者和制造商的知识产权和机密,所以只有较少的半导体制造商会在提供芯片产品的同时提供相应的SPICE模型。 SPICE模型的分析精度主要取决于模型参数的来源(即数据的精确性),以及模型方程式的适用范围。而模型方程式与各种不同的数字仿真器相结合时也可能会 影响分析的精度。有的半导体生产者在向外界提供SPICE模型时,常常会对一些涉及到知识产权的部分进行‘清理’,这样也会导致仿真结果的不准确。

IBIS模型不对电路的具体结构进行描述,而只是采用I/V和V/t表的形式来描述数字集成电路I/O单元和引脚的特性。半导体厂商很容易在不透露自己的知识产权的同时为客户提供这种模型。

IBIS模型的分析精度主要取决于I/V和V/T表的数据点数和数据的精确度。由于基于IBIS模型的PCB板级仿真采用查表计算,因而计算量较小,通常 只有相应的SPICE模型的1/10到1/100。用它进行仿真的速度要比用SPICE模型快很多。随着电路板的设计越来越复杂,使用SPICE模型仿真 会花去很长的时间,而使用IBIS模型使得对整个电路板上的系统进行仿真成为可能。虽然IBIS模型没有SPECE模型那么精确,但对于系统级分析而言已 经是完全足够了。

使用IBIS模型的另外一个优点就是,很多的IBIS模型都是由实际的器件得到,这样,一旦有了完全的IBIS数据,那么仿真得到的数据就与实际的器件有了直接的关系。

总之,由于IBIS模型的方便,快捷,以及具有必要的精确度,越来越多的半导体厂商都愿意向客户免费提供自己产品的IBIS模型。

由于目前还没有一种统一的模型来完成所有的PCB板级信号完整性分析,因此在高速数字PCB板设计中,需要混合各种模型来最大程度地建立关键信号和敏感信号的传输模型。

对于分立的无源器件,可以寻求厂家提供的SPICE模型,或者通过实验测量直接建立并使用简化的SPICE模型。对于关键的数字集成电路,则必须寻求厂家 提供的IBIS模型。目前大多数集成电路设计和制造商都能够通过web网站或其它方式在提供芯片的同时提供所需的IBIS模型。对于非关键的集成电路,若 无法得到厂家的IBIS模型,还可以依据芯片引脚的功能选用相似的或缺省的IBIS模型。当然,也可以通过实验测量来建立简化的IBIS模型。对于PCB 板上的传输线,在进行信号完整性预分析及解空间分析时可采用简化的传输线SPICE模型,而在布线后的分析中则需要依据实际的版图设计使用完整的传输线 SPICE模型。

SPICE作为一种通用的电路模拟语言,最早由加州大学伯克利分校发明。SPICE模型是对电路中实际的物理结构进行描述。由于其精确性和多功能性,已经 成为电子电路模拟的标准语言。SPICE模型目前有两个主要的版本:HSPICE和PSPICE,HSPICE主要应用于集成电路设计,而PSPICE主 要应用于PCB板和系统级的设计。

采用SPICE模型在PCB板级进行SI分析时,需要集成电路设计者和制造商提供能详细准确的描述集成电路I/O单元子电路的SPICE模型和半导体特性 的制造参数。由于这些资料通常都属于设计者和制造商的知识产权和机密,所以只有较少的半导体制造商会在提供芯片产品的同时提供相应的SPICE模型。 SPICE模型的分析精度主要取决于模型参数的来源(即数据的精确性),以及模型方程式的适用范围。而模型方程式与各种不同的数字仿真器相结合时也可能会 影响分析的精度。有的半导体生产者在向外界提供SPICE模型时,常常会对一些涉及到知识产权的部分进行‘清理’,这样也会导致仿真结果的不准确。

IBIS模型不对电路的具体结构进行描述,而只是采用I/V和V/t表的形式来描述数字集成电路I/O单元和引脚的特性。半导体厂商很容易在不透露自己的知识产权的同时为客户提供这种模型。

IBIS模型的分析精度主要取决于I/V和V/T表的数据点数和数据的精确度。由于基于IBIS模型的PCB板级仿真采用查表计算,因而计算量较小,通常 只有相应的SPICE模型的1/10到1/100。用它进行仿真的速度要比用SPICE模型快很多。随着电路板的设计越来越复杂,使用SPICE模型仿真 会花去很长的时间,而使用IBIS模型使得对整个电路板上的系统进行仿真成为可能。虽然IBIS模型没有SPECE模型那么精确,但对于系统级分析而言已 经是完全足够了。

使用IBIS模型的另外一个优点就是,很多的IBIS模型都是由实际的器件得到,这样,一旦有了完全的IBIS数据,那么仿真得到的数据就与实际的器件有了直接的关系。

总之,由于IBIS模型的方便,快捷,以及具有必要的精确度,越来越多的半导体厂商都愿意向客户免费提供自己产品的IBIS模型。

由于目前还没有一种统一的模型来完成所有的PCB板级信号完整性分析,因此在高速数字PCB板设计中,需要混合各种模型来最大程度地建立关键信号和敏感信号的传输模型。

对于分立的无源器件,可以寻求厂家提供的SPICE模型,或者通过实验测量直接建立并使用简化的SPICE模型。对于关键的数字集成电路,则必须寻求厂家 提供的IBIS模型。目前大多数集成电路设计和制造商都能够通过web网站或其它方式在提供芯片的同时提供所需的IBIS模型。对于非关键的集成电路,若 无法得到厂家的IBIS模型,还可以依据芯片引脚的功能选用相似的或缺省的IBIS模型。当然,也可以通过实验测量来建立简化的IBIS模型。对于PCB 板上的传输线,在进行信号完整性预分析及解空间分析时可采用简化的传输线SPICE模型,而在布线后的分析中则需要依据实际的版图设计使用完整的传输线 SPICE模型。

3、IBIS模型的构成

一个IBIS文件包括了从行为上模拟一个器件的输入、输出和I/O缓冲器所需要的数据,它以ASCII的格式保存。IBIS文件中的数据被用来构成一个模 型,这个模型可以用来对印刷电路板进行信号完整性仿真和时序分析。进行这些仿真所需的最基本的信息是一个缓冲器的I/V参数和开关参数(输出电压与时间的 关系)。要注意的是,IBIS本身只是一种文件格式,它说明在一个标准的IBIS文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些被记 录的数据如何使用,这些参数要由使用IBIS模型的工具来读取。

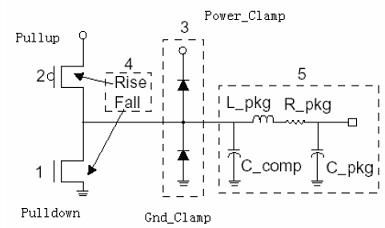

IBIS模型是以元件为中心的,也就是说,一个IBIS文件允许你模拟整个的一个元件,而不仅仅是一个特定的输入、输出或I/O缓冲器。因而,除了器件缓 冲器的电学特性参数以外,IBIS文件还包括了器件的管脚信息以及器件封装的电学参数。从Version 1.1开始,就定义了一个IBIS模型文件的最基本的组成元素为I/V数据表、开关信息和封装信息(图1)。

图1 IBIS模型的基本组成元素

图中,模块2 Pullup和模块1 PullDown表现了标准输出缓冲器的上拉和下拉晶体管,用直流I/V数据表来描述它们的行为。模块3中的Power_Clamp和Gnd_Clamp 是静电放电或钳位二极管,也是用直流I/V数据表来描述的。模块4在IBIS文件中是Ramp参数,表示输出从一个逻辑状态转换到另一个逻辑状态,用dV /dt来描述某一特定阻性负载下输出波形的上升沿和下降沿。模块5描述的是体电容和封装寄生参数,其中C_comp是硅晶元电容,它是不包括封装参数的总 的输出电容_L_pkg、R_pkg和C_pkg分别是由封装带来的寄生电感、寄生电阻和寄生电容。如果描述的仅仅是输入管脚的IBIS模型,则只由模块 3和模块5两部分组成即可。

IBIS规范要求的I/V曲线的范围是Vcc到(2*Vcc),制定这一电压范围的原因是,由全反射所引起的过冲理论上的最大值是两倍的信号摆幅。 Gnd_Clamp的I/V曲线范围定义为-Vcc到Vcc,而Power_Clamp的I/V曲线范围是0到(2*Vcc)。要注意的是,Pullup 和Power_Clamp在IBIS文件中的电压Vtable为Vcc-Voutput。

[Pulldown]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -40.0m -34.0m -45.0m

-4.0V -39.0m -33.0m -43.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V 40.0m 34.0m 45.0m

10.0V 45.0m 4 0.0m 4 9.0m

|

[Pullup] | Note: Vtable=Vcc -Voutput

|

Voltage I(typ) I(min) I(max)

-5.0V 32.0m 30.0m 35.0m

-4.0V 3 1.0m 2 9.0m 33.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V -32.0m -30.0m -35.0m

10.0V -38.0m -35.0m -40.0m

|

[GND C1amp]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -390 0.0m -3800.0m -4000.0m

-0.7V -80.0m -75.0m -85.0m

-0.6V -22.0m -20.0m -25.0m

-0.5V -2.4m -2.0m -2.9m

-0.4V 0.0m 0.0m 0.0m

5.0V 0.0m 0.0m 0.0m

|

[POWER Clamp] | Note:Vtable=Vcc—Voutput

|

| Voltage I(typ) I(min) I(max)

|

-5.0V 4450.0m NA NA

-0.7V 95.0m NA NA

-0.6V 23.0m NA NA

-0.5V 2.4m NA NA

-0.4V 0.0m NA NA

0.0V 0.0m NA NA

Ramp参数表示了缓冲器的上升和下降时间,Ramp中的dV是缓冲器输出电压由20%变化到80%间的差值。这一参数只计入了晶元电容C_comp的影 响,而不考虑封装寄生参数的影响。有时也用dV/&曲线来描述同样的开关特性,相比之下dV/&曲线要更加精确一些。R_load表示这 些数据是在什么样的负载状况下得到的,如果使用的是标准的50 ohm负载,那么这一项是可选择的。

[Ramp]

| variable typ min max

dV/dt_r 2.20/1.06n 1.92/1.28n 2.49/650p

dV/dt_f 2.46/1.21n 2.21/1.54n 2.70/770p

R_load=300ohms

上面所提到的这些数据都有三个值可供选择:典型值、最小值和最大值.这些是由工作环境的温度、电源电压以及工艺制程的变化来决定的。使用各种数据的最小值 和最大值,就可以表现出模型的最差和最好情况。例如,要得到一个快速的模型,可以使用最高值的电流、最快的ramp数据以及最小的封装寄生参数:而要得到 慢速的模型则正好相反。在有的模型中,并不提供最小值和最大值,只是用N/A来表示,如上面举的Power Clamp的例子。而典型值在模型中是必须要提供的。

封装寄生参数在IBIS模型文件中用R_pkg、L_pkg和C_pkg来表示,如果在文件中对管脚的说明部分对每个管脚又赋予了具体的封装参数值,那么全局定义的封装参数就不起作用。

在前面给出的IBIS文件的例子中可以看到,每一部分的开头都由方括号开始,在方括号中的是定义语句的关键字,它对跟在后面的数据作出了说明,这样仿真器 就可以使用这些数据。在一个IBIS文件中,有的关键字是必须的,而有的则是可选择的。一个有效的IBIS文件必须包括以下三部分的数据和关键字:

一个IBIS文件包括了从行为上模拟一个器件的输入、输出和I/O缓冲器所需要的数据,它以ASCII的格式保存。IBIS文件中的数据被用来构成一个模 型,这个模型可以用来对印刷电路板进行信号完整性仿真和时序分析。进行这些仿真所需的最基本的信息是一个缓冲器的I/V参数和开关参数(输出电压与时间的 关系)。要注意的是,IBIS本身只是一种文件格式,它说明在一个标准的IBIS文件中如何记录一个芯片的驱动器和接收器的不同参数,但并不说明这些被记 录的数据如何使用,这些参数要由使用IBIS模型的工具来读取。

IBIS模型是以元件为中心的,也就是说,一个IBIS文件允许你模拟整个的一个元件,而不仅仅是一个特定的输入、输出或I/O缓冲器。因而,除了器件缓 冲器的电学特性参数以外,IBIS文件还包括了器件的管脚信息以及器件封装的电学参数。从Version 1.1开始,就定义了一个IBIS模型文件的最基本的组成元素为I/V数据表、开关信息和封装信息(图1)。

图1 IBIS模型的基本组成元素

图中,模块2 Pullup和模块1 PullDown表现了标准输出缓冲器的上拉和下拉晶体管,用直流I/V数据表来描述它们的行为。模块3中的Power_Clamp和Gnd_Clamp 是静电放电或钳位二极管,也是用直流I/V数据表来描述的。模块4在IBIS文件中是Ramp参数,表示输出从一个逻辑状态转换到另一个逻辑状态,用dV /dt来描述某一特定阻性负载下输出波形的上升沿和下降沿。模块5描述的是体电容和封装寄生参数,其中C_comp是硅晶元电容,它是不包括封装参数的总 的输出电容_L_pkg、R_pkg和C_pkg分别是由封装带来的寄生电感、寄生电阻和寄生电容。如果描述的仅仅是输入管脚的IBIS模型,则只由模块 3和模块5两部分组成即可。

IBIS规范要求的I/V曲线的范围是Vcc到(2*Vcc),制定这一电压范围的原因是,由全反射所引起的过冲理论上的最大值是两倍的信号摆幅。 Gnd_Clamp的I/V曲线范围定义为-Vcc到Vcc,而Power_Clamp的I/V曲线范围是0到(2*Vcc)。要注意的是,Pullup 和Power_Clamp在IBIS文件中的电压Vtable为Vcc-Voutput。

[Pulldown]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -40.0m -34.0m -45.0m

-4.0V -39.0m -33.0m -43.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V 40.0m 34.0m 45.0m

10.0V 45.0m 4 0.0m 4 9.0m

|

[Pullup] | Note: Vtable=Vcc -Voutput

|

Voltage I(typ) I(min) I(max)

-5.0V 32.0m 30.0m 35.0m

-4.0V 3 1.0m 2 9.0m 33.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V -32.0m -30.0m -35.0m

10.0V -38.0m -35.0m -40.0m

|

[GND C1amp]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -390 0.0m -3800.0m -4000.0m

-0.7V -80.0m -75.0m -85.0m

-0.6V -22.0m -20.0m -25.0m

-0.5V -2.4m -2.0m -2.9m

-0.4V 0.0m 0.0m 0.0m

5.0V 0.0m 0.0m 0.0m

|

[POWER Clamp] | Note:Vtable=Vcc—Voutput

|

| Voltage I(typ) I(min) I(max)

|

-5.0V 4450.0m NA NA

-0.7V 95.0m NA NA

-0.6V 23.0m NA NA

-0.5V 2.4m NA NA

-0.4V 0.0m NA NA

0.0V 0.0m NA NA

Ramp参数表示了缓冲器的上升和下降时间,Ramp中的dV是缓冲器输出电压由20%变化到80%间的差值。这一参数只计入了晶元电容C_comp的影 响,而不考虑封装寄生参数的影响。有时也用dV/&曲线来描述同样的开关特性,相比之下dV/&曲线要更加精确一些。R_load表示这 些数据是在什么样的负载状况下得到的,如果使用的是标准的50 ohm负载,那么这一项是可选择的。

[Ramp]

| variable typ min max

dV/dt_r 2.20/1.06n 1.92/1.28n 2.49/650p

dV/dt_f 2.46/1.21n 2.21/1.54n 2.70/770p

R_load=300ohms

上面所提到的这些数据都有三个值可供选择:典型值、最小值和最大值.这些是由工作环境的温度、电源电压以及工艺制程的变化来决定的。使用各种数据的最小值 和最大值,就可以表现出模型的最差和最好情况。例如,要得到一个快速的模型,可以使用最高值的电流、最快的ramp数据以及最小的封装寄生参数:而要得到 慢速的模型则正好相反。在有的模型中,并不提供最小值和最大值,只是用N/A来表示,如上面举的Power Clamp的例子。而典型值在模型中是必须要提供的。

封装寄生参数在IBIS模型文件中用R_pkg、L_pkg和C_pkg来表示,如果在文件中对管脚的说明部分对每个管脚又赋予了具体的封装参数值,那么全局定义的封装参数就不起作用。

在前面给出的IBIS文件的例子中可以看到,每一部分的开头都由方括号开始,在方括号中的是定义语句的关键字,它对跟在后面的数据作出了说明,这样仿真器 就可以使用这些数据。在一个IBIS文件中,有的关键字是必须的,而有的则是可选择的。一个有效的IBIS文件必须包括以下三部分的数据和关键字:

- 被模拟的器件及IBIS文件本身的信息,包含这些信息的关键字为[IBIS Ver]、[FileName]、 [File Rev]、 [Component]、 [Manufacturer]。

- 与封装的电气特性相关的信息以及管脚分布情况,用关键字[Package]和[Pin]说明。

- 模拟器件的输入、输出及I/O缓冲器所需的数据,用关键字[Model]、[Pullup]、[Pulldown]、 [GND Camp]、 [Power Clamp]和[Ramp]说明。

4、建立IBIS模型

IBIS模型可以通过仿真器件的SPICE模型来获得,也可以用直接测量的方法来获得。作为最终用户,最常见的方法是到半导体制造厂商的网站上去下载各种器件的IBIS模型,在使用前要对得到的IBIS模型进行语法检查。

建立一个器件的IBIS模型需要以下几个步骤:

IBIS模型可以通过仿真器件的SPICE模型来获得,也可以用直接测量的方法来获得。作为最终用户,最常见的方法是到半导体制造厂商的网站上去下载各种器件的IBIS模型,在使用前要对得到的IBIS模型进行语法检查。

建立一个器件的IBIS模型需要以下几个步骤:

- 进行建立模型前的准备工作。这包括了:决定模型的复杂程度;根据模型所要表现的内容和元件工作的环境,来确定电压和温度范围以及制程限制等因素;获取元件相关信息,如电气特性以及管脚分布;器件的应用信息。

- 完成了上面的工作后,接下来就是要获得I-V曲线或上升/下降曲线的数据,这可以通过直接测量或是仿真得到。

- 将得到的数据写入IBIS模型。不同的数据在各自相应的关键字后列出,要注意满足IBIS的语法要求。

- 初步建立了模型后,应当用s2iplt等工具来查看以图形方式表现的V/I曲线,并检查模型的语法是否正确。如果模型是通过仿真得到的,应当分别用IBIS模型和最初的晶体管级模型进行仿真,比较其结果,以检验模型的正确性。

- 得到了实际的器件后,或者如果模型是由测量得到的,要对模型的输出波形和测量的波形进行比较。

5、使用IBIS模型

IBIS模型可以通过仿真器件的SPICE模型来获得,也可以用直接测量的方法来获得。最为最终用户,最常见的方法是到半导体制造厂商的网站上去下载各种器件的IBIS模型,在使用前要对得到的IBIS模型进行语法检查。

IBIS模型主要用于板级系统或多板信号的信号完整性分析。可以用IBIS模型分析的信号完整性问题包括:串扰、反射、振铃、上冲、下冲、不匹配阻抗、传 输线分析、拓扑结构分析等等。IBIS模型尤其能够对高速信号的振铃和串扰进行准确精细的仿真,它可用于检测最坏情况的上升时间条件下的信号行为,以及一 些用物理测试无法解决的问题。在使用时,用户用PCB的数据库来生成电路板上的连线的传输线模型,然后将IBIS模型赋给电路板上相应的驱动端或接收端, 就可以进行仿真了。

图2和图3给出了一个用IBIS模型进行信号完整性分析的例子。可以看到,在使用IBIS模型进行仿真后,发现信号质量不佳,于是采取了添加终端匹配的方法,使信号质量有了较大的改善。

图2 未添加终端匹配的例子

图3 添加了串联匹配的例子

为了满足多板信号仿真的要求,IBIS最新的版本Version3.2中添加了EBD(ElectricalBoard Description)的新特点。EBD模型的基本语法与IBIS模型相同,它是将整块电路板做为一个器件来对待,这样,在多板仿真时就可以直接调用 EBD模型,而不用关心EBD模型所描述的电路板内部的具体情况。使用一些电路板仿真软件可以自动生成EBD模型,例如HyperLynx6.1就有这一 功能。

虽然IBIS模型有很多的优点,但是也存在一些不足。目前,仍有许多厂商缺乏对IBIS模型的支持。而缺乏IBIS模型,IBIS仿真工具就无法工作。虽 然IBIS文件可以手动创建或通过Spice模型来转换,但是如果无法从厂家得到最小上升时间参数,任何转换工具都无能为力。另外,IBIS还缺乏对地弹 噪声的建模能力。

IBIS模型可以通过仿真器件的SPICE模型来获得,也可以用直接测量的方法来获得。最为最终用户,最常见的方法是到半导体制造厂商的网站上去下载各种器件的IBIS模型,在使用前要对得到的IBIS模型进行语法检查。

IBIS模型主要用于板级系统或多板信号的信号完整性分析。可以用IBIS模型分析的信号完整性问题包括:串扰、反射、振铃、上冲、下冲、不匹配阻抗、传 输线分析、拓扑结构分析等等。IBIS模型尤其能够对高速信号的振铃和串扰进行准确精细的仿真,它可用于检测最坏情况的上升时间条件下的信号行为,以及一 些用物理测试无法解决的问题。在使用时,用户用PCB的数据库来生成电路板上的连线的传输线模型,然后将IBIS模型赋给电路板上相应的驱动端或接收端, 就可以进行仿真了。

图2和图3给出了一个用IBIS模型进行信号完整性分析的例子。可以看到,在使用IBIS模型进行仿真后,发现信号质量不佳,于是采取了添加终端匹配的方法,使信号质量有了较大的改善。

图2 未添加终端匹配的例子

图3 添加了串联匹配的例子

为了满足多板信号仿真的要求,IBIS最新的版本Version3.2中添加了EBD(ElectricalBoard Description)的新特点。EBD模型的基本语法与IBIS模型相同,它是将整块电路板做为一个器件来对待,这样,在多板仿真时就可以直接调用 EBD模型,而不用关心EBD模型所描述的电路板内部的具体情况。使用一些电路板仿真软件可以自动生成EBD模型,例如HyperLynx6.1就有这一 功能。

虽然IBIS模型有很多的优点,但是也存在一些不足。目前,仍有许多厂商缺乏对IBIS模型的支持。而缺乏IBIS模型,IBIS仿真工具就无法工作。虽 然IBIS文件可以手动创建或通过Spice模型来转换,但是如果无法从厂家得到最小上升时间参数,任何转换工具都无能为力。另外,IBIS还缺乏对地弹 噪声的建模能力。

6、IBIS相关工具及链接

IBIS问世以来,出现了很多相关的工具,下面介绍几种常用的免费工具 :

IBIS问世以来,出现了很多相关的工具,下面介绍几种常用的免费工具 :

- Ibischk:能够对IBIS文件进行语法检查

- S2ibis:NCSU发明的SPICE到IBIS的转换工具,支持HSPICE、PSPICE和SPICE3

- S2iplt:NCSU发明,能够将IBIS文件中的V/I数据以图的形式表现。

- Visual IBIS editor:HyperLynx中提供的工具,能够对IBIS模型进行语法检查,编辑以及对V/I数据绘图。

- IBIS Cookbook:详细描述了产生一个IBIS模型所需的步骤。

如果需要到网上查找一些IBIS的相关内容,下面的几个链接可能会提供一些帮助:

http://www.eigroup.org/ibis/ibis.htm

http://www.innoveda.com/products/datasheets_HTML/ibis.asp

http://www2.ncsu.edu/eos/project/erl_htm

http://www.eigroup.org/ibis/ibis.htm

http://www.innoveda.com/products/datasheets_HTML/ibis.asp

http://www2.ncsu.edu/eos/project/erl_htm

IBIS 学习笔记

IBIS(Input/Output Buffer Information Specification)模型是基于V/I曲线的对I/O Buffer快速准确建模的方法,其目的是提供一种集成电路制造商与仿真软件供应商以及设计工程师之间相互交换电子元件仿真数据的标准方法。IBIS是一 种行为模型,它不是从要仿真的元件的结构出发定义的,而是从元件的行为出发定义的。IBIS本身是一种标准的文本格式,它记录驱动器和接收器的不同参数, 如驱动源输出阻抗、上升/下降时间以及输入负载等参数,但它不说明这些记录参数是如何使用的。

IBIS模型分为驱动器模型和接收器模型,如下图示:

Pull up/pull down:标准输出缓冲器的上拉和下拉晶体管,用直流I/V数据表来描述它们的行为。

Power clamp/gnd clamp:静电放电和钳位二极管,用直流I/V数据表来描述它们的行为。

Ramp:表示输出从一个逻辑状态转换到另一个逻辑状态,用dV/dt来描述。

C_comp:硅晶圆电容,它是不包括封装参数的总输出电容。

R_pkg/L_pkg/C_pkg:封装带来的寄生电阻、电感和电容。。

无论是驱动器模型还是接收器模型都是由两部分组成的:缓冲器结构模型([model] section)和封装因子([component]&[pin] section)。

IBIS模型分为驱动器模型和接收器模型,如下图示:

Pull up/pull down:标准输出缓冲器的上拉和下拉晶体管,用直流I/V数据表来描述它们的行为。

Power clamp/gnd clamp:静电放电和钳位二极管,用直流I/V数据表来描述它们的行为。

Ramp:表示输出从一个逻辑状态转换到另一个逻辑状态,用dV/dt来描述。

C_comp:硅晶圆电容,它是不包括封装参数的总输出电容。

R_pkg/L_pkg/C_pkg:封装带来的寄生电阻、电感和电容。。

无论是驱动器模型还是接收器模型都是由两部分组成的:缓冲器结构模型([model] section)和封装因子([component]&[pin] section)。

IBIS文件结构

IBIS文件包括了从行为上模拟一个器件的输入、输出和I/O缓冲器所需要的数据,它以ASCII的格式保存。IBIS文件的格式如下图示:

IBIS文件主要由三部分构成:

1. 文件头描述:包括IBIS版本、文件名以及资料来源、修订等信息。

2. 元件描述:该部分包含从数据手册中得到的元件引脚、封装电特性等信息,用关键字[package]和[pin]说明。

3. 模 型描述:该部分描述电流、电压曲线和开关特性,模型用[pull up]、[Pull down]、[gnd clamp]、[power clamp]和[ramp]等关键字说明,[model]后的参数定义了模型的类型(输入、输出、I/O、开漏极等)以及它的输入/输出电容。

IBIS模型有3组可能的值:min、max以及typ。

IBIS文件中的V/I曲线数据包括:pull up、pull down、power clamp、gnd clamp四种,V/I曲线数据描述电压从-Vcc~+2Vcc的对应电流的情况,输入芯片的电流为正。

IBIS文件包括了从行为上模拟一个器件的输入、输出和I/O缓冲器所需要的数据,它以ASCII的格式保存。IBIS文件的格式如下图示:

IBIS文件主要由三部分构成:

1. 文件头描述:包括IBIS版本、文件名以及资料来源、修订等信息。

2. 元件描述:该部分包含从数据手册中得到的元件引脚、封装电特性等信息,用关键字[package]和[pin]说明。

3. 模 型描述:该部分描述电流、电压曲线和开关特性,模型用[pull up]、[Pull down]、[gnd clamp]、[power clamp]和[ramp]等关键字说明,[model]后的参数定义了模型的类型(输入、输出、I/O、开漏极等)以及它的输入/输出电容。

IBIS模型有3组可能的值:min、max以及typ。

IBIS文件中的V/I曲线数据包括:pull up、pull down、power clamp、gnd clamp四种,V/I曲线数据描述电压从-Vcc~+2Vcc的对应电流的情况,输入芯片的电流为正。

IBIS模型类型:

1. 输入(input):作为接收器,必须定义输入门限(Vinh、Vinl)、Power clamp和gnd clamp;

2. 输出(output):作为驱动器,必须定义power clamp、gnd clamp、pull up、pull down、ramp(dV/dt),此外可以有输出高低电平门限(不属于IBIS模型规范);

3. I/O:根据使能既可以作为驱动器也可以作为接收器;

4. 三态(3-state):通常作为驱动器,也可通过使能端关闭;

5. open_drain:典型的驱动器模型,有一个开路的上拉侧;

6. I/O_open_drain:具有I/O和open_drain双重特性;

7. open_sink:驱动器模型,有一个开路的上拉侧,由用户提供一个上拉的电阻和一个电压连接;

8. I/O_open_sink:具有I/O和open_sink双重特性;

9. open_source:驱动器的模型,有一个开路的下拉侧,由用户提供一个下拉电阻和地或电源的电压连接;

10. I/O_open_source:具有I/O和open_source双重特性;

11. ECL:Emitter Coupled Logic,包括input_ECL、output_ECL、I/O_ECL、3-state_ECL;

12. 终端terminator:通常是输入模型,当没有数字逻辑门限时作为模拟的负载效应,如电阻、电容、二极管等。

1. 输入(input):作为接收器,必须定义输入门限(Vinh、Vinl)、Power clamp和gnd clamp;

2. 输出(output):作为驱动器,必须定义power clamp、gnd clamp、pull up、pull down、ramp(dV/dt),此外可以有输出高低电平门限(不属于IBIS模型规范);

3. I/O:根据使能既可以作为驱动器也可以作为接收器;

4. 三态(3-state):通常作为驱动器,也可通过使能端关闭;

5. open_drain:典型的驱动器模型,有一个开路的上拉侧;

6. I/O_open_drain:具有I/O和open_drain双重特性;

7. open_sink:驱动器模型,有一个开路的上拉侧,由用户提供一个上拉的电阻和一个电压连接;

8. I/O_open_sink:具有I/O和open_sink双重特性;

9. open_source:驱动器的模型,有一个开路的下拉侧,由用户提供一个下拉电阻和地或电源的电压连接;

10. I/O_open_source:具有I/O和open_source双重特性;

11. ECL:Emitter Coupled Logic,包括input_ECL、output_ECL、I/O_ECL、3-state_ECL;

12. 终端terminator:通常是输入模型,当没有数字逻辑门限时作为模拟的负载效应,如电阻、电容、二极管等。

参考资料:

Cadence高速PCB设计与仿真分析 北京航空航天大学出版社 黄豪佑等

Cadence高速PCB设计与仿真分析 北京航空航天大学出版社 黄豪佑等

IBIS 原理说明

IBIS 模型在做类似板级SI 仿真得到广泛应用。在做仿真的初级阶段,经常对于ibis 模型的描述有些疑问,只知道把模型拿来转换为软件所支持的格式或者直接使用,而对于IBIS 模型里面的数据描述什么都不算很明白,因此下面的一些描述是整理出来的一点对于ibis 的基本理解。在此引用很多presention来描述ibis 内容(有的照抄过来,阿弥陀佛,不要说抄袭,只不过习惯信手拈来说明一些问题),仅此向如muranyi 等ibis 先驱者致敬。本文难免有些错误或者考虑不周,随时欢迎进行讨论并对其进行修改!

IBIS 模型的一些基本概念

IBIS 这个词是Input/Output buffer information specification 的缩写。本文是基于IBIS ver3.2 所撰写出来( www.eigroup.org/IBIS/可下载到各种版本spec),ver4.2增加很多新特性,由于在目前设计中没用到不予以讨论。。。

在业界经常会把spice 模型描述为transistor model 是因为它描述很多电路细节问题。而把ibis 模型描述为behavioral model 是因为它并不象spice 模型那样描述电路的构成,IBIS 模型描述的只不过是电路的一种外在表现,象个黑匣子一样,输入什么然后就得到输出结果,而不需要了解里面驱动或者接收的电路构成。因此有所谓的 garbage in, garbage out,ibis 模型的仿真精度依赖于模型的准确度以及考虑的worse case,因此无论你的模型如何精确而考虑的worse case 不周全或者你考虑的worse case 如何周全而模型不精确,都是得不到较好的仿真精度。

IBIS 这个词是Input/Output buffer information specification 的缩写。本文是基于IBIS ver3.2 所撰写出来( www.eigroup.org/IBIS/可下载到各种版本spec),ver4.2增加很多新特性,由于在目前设计中没用到不予以讨论。。。

在业界经常会把spice 模型描述为transistor model 是因为它描述很多电路细节问题。而把ibis 模型描述为behavioral model 是因为它并不象spice 模型那样描述电路的构成,IBIS 模型描述的只不过是电路的一种外在表现,象个黑匣子一样,输入什么然后就得到输出结果,而不需要了解里面驱动或者接收的电路构成。因此有所谓的 garbage in, garbage out,ibis 模型的仿真精度依赖于模型的准确度以及考虑的worse case,因此无论你的模型如何精确而考虑的worse case 不周全或者你考虑的worse case 如何周全而模型不精确,都是得不到较好的仿真精度。

IBIS 模型的构成

经典示意图如下:

从上图可以看出,基本的IBIS模型包括如下的一些信息(对于不同类型的model有一些信息会省略掉)

VI 曲线: Pullup & Pulldown &POWER clamp& GND clamp

VT曲线: Rise waveform, Fall waveform

还有一些其它比较重要的信息比如Die capacitance: C_comp(最近好像那个muranyi对这个很感兴趣,一直发布presentation讨论怎么把这个做的更精确)以及RLC package parameter。至于一些基本的输入以及使能信息会在软件设置自动生成,不需要我们多关注。对于于ibis模型长什么样子,大家去micron主页 ddr2 sdram模块下载几个io buffer看看是什么样。希望你先看看长啥样再看下面的一些说明。

经典示意图如下:

从上图可以看出,基本的IBIS模型包括如下的一些信息(对于不同类型的model有一些信息会省略掉)

VI 曲线: Pullup & Pulldown &POWER clamp& GND clamp

VT曲线: Rise waveform, Fall waveform

还有一些其它比较重要的信息比如Die capacitance: C_comp(最近好像那个muranyi对这个很感兴趣,一直发布presentation讨论怎么把这个做的更精确)以及RLC package parameter。至于一些基本的输入以及使能信息会在软件设置自动生成,不需要我们多关注。对于于ibis模型长什么样子,大家去micron主页 ddr2 sdram模块下载几个io buffer看看是什么样。希望你先看看长啥样再看下面的一些说明。

IBIS 的应用场合

任何电路都可以用下面的模型(好像是Shannon 模型我不知道。。。)来描述

Driver -------------interconnect------------------Receiver

注意IBIS 模型描述的是Driver/Receiver 的行为特性而并不是它们的电路特性,因而内部的一些逻辑延时是没有考虑的(在此你就该好好明白为啥要区分Tco的概念),通过使用IBIS 模型,从而得出interconnect 对于电路的影响。在目前一些使用ibis model 仿真的软件中,在Cadence 里面,ibis 模型是转换为dml 格式,在Hyperlynx 里面直接调用ibis 模型。由于ibis 支持的buffer type 很多,每个类型都会有对应的格式以及需要包含的信息,常用有output, input 以及IO 模型,至于其他的模型,大家可以参照ibis 说明,有些些微的差异。

任何电路都可以用下面的模型(好像是Shannon 模型我不知道。。。)来描述

Driver -------------interconnect------------------Receiver

注意IBIS 模型描述的是Driver/Receiver 的行为特性而并不是它们的电路特性,因而内部的一些逻辑延时是没有考虑的(在此你就该好好明白为啥要区分Tco的概念),通过使用IBIS 模型,从而得出interconnect 对于电路的影响。在目前一些使用ibis model 仿真的软件中,在Cadence 里面,ibis 模型是转换为dml 格式,在Hyperlynx 里面直接调用ibis 模型。由于ibis 支持的buffer type 很多,每个类型都会有对应的格式以及需要包含的信息,常用有output, input 以及IO 模型,至于其他的模型,大家可以参照ibis 说明,有些些微的差异。

IBIS 模型中vi/vt 曲线的由来

有大牛的示意图形,不多说

Pull down 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

Ground clamp 曲线由来

Pull up 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

Power clamp 曲线由来

注意:ibis 里面定义电流流入方向为正;在此图中pull up 以及power clamp 曲线都没经过转化(传说的vcc relative 没出现,^_^,使用Vcc relative 从目前得到的解释是模型可以应用在兼容电压模式,举个例子2.5v 兼容3.3V 的器件,2.5v 和3.3v 工作状态下可以使用相同的模型而不用建立两模型描述单个器件)

有大牛的示意图形,不多说

Pull down 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

Ground clamp 曲线由来

Pull up 曲线由来(此曲线需要考虑与clamp 曲线重复的部分)

Power clamp 曲线由来

注意:ibis 里面定义电流流入方向为正;在此图中pull up 以及power clamp 曲线都没经过转化(传说的vcc relative 没出现,^_^,使用Vcc relative 从目前得到的解释是模型可以应用在兼容电压模式,举个例子2.5v 兼容3.3V 的器件,2.5v 和3.3v 工作状态下可以使用相同的模型而不用建立两模型描述单个器件)

IBIS 模型在软件中的应用

目前高速信号软件大部分都是spice-compatible 软件,而且很多都内嵌field solver分析传输线,因而在仿真中势必会把ibis 模型的信息转换成spice 信息来使用,来看看ibis 模型是如何转换成spice 信息使用的。看下如下的示意图,

当外接fixture,此部分电路可以直接在spice 中求解

但是VI 曲线仅仅描述的是DC 状态,那么在ibis 模型中描述瞬态的vt 曲线如何

转换值得商讨,看以下的等效图

可以得出等式:-Iout=Ku*Ipu+Kd*Ipd+Ipc+Igc

如果rising/falling waveform 只有一条曲线,比如VCC+Rfixture,可假设

得方程

如果有两条曲线,比如VCC/GND+Rfixture,Ku 与Kd 独立解出,从而可以得出仿真的瞬态曲线

目前高速信号软件大部分都是spice-compatible 软件,而且很多都内嵌field solver分析传输线,因而在仿真中势必会把ibis 模型的信息转换成spice 信息来使用,来看看ibis 模型是如何转换成spice 信息使用的。看下如下的示意图,

当外接fixture,此部分电路可以直接在spice 中求解

但是VI 曲线仅仅描述的是DC 状态,那么在ibis 模型中描述瞬态的vt 曲线如何

转换值得商讨,看以下的等效图

可以得出等式:-Iout=Ku*Ipu+Kd*Ipd+Ipc+Igc

如果rising/falling waveform 只有一条曲线,比如VCC+Rfixture,可假设

得方程

如果有两条曲线,比如VCC/GND+Rfixture,Ku 与Kd 独立解出,从而可以得出仿真的瞬态曲线

比较有趣的问题

Vi/Vt 曲线的匹配(参考hyperlynx 的帮助)

对 于falling waveform R_fixture=50 Ohms and V_fixture=3.3V负载线与pull up 曲线交界为falling waveform 起始点,与pull down 曲线交界为falling waveform 终点(始终记住pull up 是Vcc relative 需要转换)

对于Rising waveform R_fixture=50 Ohms and V_fixture=3.3V

负载线与pull down 曲线交界为rising waveform 起始点,与pull up 曲线交界为rising waveform 终点

Vi/Vt 曲线的匹配(参考hyperlynx 的帮助)

对 于falling waveform R_fixture=50 Ohms and V_fixture=3.3V负载线与pull up 曲线交界为falling waveform 起始点,与pull down 曲线交界为falling waveform 终点(始终记住pull up 是Vcc relative 需要转换)

对于Rising waveform R_fixture=50 Ohms and V_fixture=3.3V

负载线与pull down 曲线交界为rising waveform 起始点,与pull up 曲线交界为rising waveform 终点

Package model 的应用

在ibis 里面有三个地方可以使用package model

A, [Pin] 语句里面,描述的是local package 参数,只有typ 值

B, [Package]语句里面,描述的是global package 参数,有slow/typ/fast 取值

C, [Define Package Model]里面,描述的是local package 参数,能带传输线,只有typ 值

在ibis 里面有三个地方可以使用package model

A, [Pin] 语句里面,描述的是local package 参数,只有typ 值

B, [Package]语句里面,描述的是global package 参数,有slow/typ/fast 取值

C, [Define Package Model]里面,描述的是local package 参数,能带传输线,只有typ 值

Ramp 数值由来

测量vt 曲线

dv=(80%-20%)*(Vmaximum-Vminimum)

dt= t [80%*(Vmaximum-Vminimum)]- t [20%*(Vmaximum-Vminimum)]

测量vt 曲线

dv=(80%-20%)*(Vmaximum-Vminimum)

dt= t [80%*(Vmaximum-Vminimum)]- t [20%*(Vmaximum-Vminimum)]

总结

1,很多人告诉我说想验证ibis 模型,比较好玩,实际上你用软件检查后你会发现很少有其它事情我们可以做的。。。毕竟,你不是做芯片的,不要扁我!对于有问题的ibis 模型,我们有办法做什么事情么?没有,但你一定要知道问题在那儿,灭那些芯片的而不用被他们嘲笑,哈哈。

2,关于ibis 的发展前途,从目前发展趋势,它的归宿只有两个:

a 由于自动化的需要,迟早要成为一个编程语言,哈哈,又多一个求生的饭碗,大家快去学。。。

b 不要高兴太早,它有可能语法太庞大复杂最终被其它取代。。。

1,很多人告诉我说想验证ibis 模型,比较好玩,实际上你用软件检查后你会发现很少有其它事情我们可以做的。。。毕竟,你不是做芯片的,不要扁我!对于有问题的ibis 模型,我们有办法做什么事情么?没有,但你一定要知道问题在那儿,灭那些芯片的而不用被他们嘲笑,哈哈。

2,关于ibis 的发展前途,从目前发展趋势,它的归宿只有两个:

a 由于自动化的需要,迟早要成为一个编程语言,哈哈,又多一个求生的饭碗,大家快去学。。。

b 不要高兴太早,它有可能语法太庞大复杂最终被其它取代。。。

参考文献

1.Hyperlynx 帮助

2.The Development of Analog SPICE Behavioral Model Based on IBIS Model

3.Introduction to IBIS models and IBIS model making

尚且不清楚的几个问题

1.对于一个I/O Buffer,IBIS file的table哪些是描述输入特性的,哪些是描述输出特性的?

2.对于pull down 和pull up tables, voltage sweep range是-V到2V,所以必然会存在电流倒灌(倒灌到供电电源或者从地流出)的现象,这对于电路使用者有什么作用?实际电路中这种情况会对供电电源造成伤害吗?

3.怎么从IBIS里面的table计算出Buffer的输出电阻来?这个电阻应该是一个变化的值,当输出不同的电流时取值不同。那么如果对其做源端串行端接的话使用怎样的电阻值?

1.Hyperlynx 帮助

2.The Development of Analog SPICE Behavioral Model Based on IBIS Model

3.Introduction to IBIS models and IBIS model making

尚且不清楚的几个问题

1.对于一个I/O Buffer,IBIS file的table哪些是描述输入特性的,哪些是描述输出特性的?

2.对于pull down 和pull up tables, voltage sweep range是-V到2V,所以必然会存在电流倒灌(倒灌到供电电源或者从地流出)的现象,这对于电路使用者有什么作用?实际电路中这种情况会对供电电源造成伤害吗?

3.怎么从IBIS里面的table计算出Buffer的输出电阻来?这个电阻应该是一个变化的值,当输出不同的电流时取值不同。那么如果对其做源端串行端接的话使用怎样的电阻值?