学习笔记:FPGA设计Verilog基础(四)——Verilog各部分的写法

1、verilog的程序

module 模块名 (

input wire 端口名;

output reg 端口名;//端口定义+I/O说明+内部信号声明

);

....//功能定义

endmodule2、测试文件Testbench:

`timescale 1ns/1ns

module count_text;

reg clk;

reg clear;

wire[3:0] Q;

count m1 (.clk(clk), .clear(clear), .Q(Q));

always #10 clk = ~clk; /*"#10"表示半个时钟周期, parameter #10 clk = ~clk;

这句定义了20ns为一个周期,频率为f=1/T=1/20*10^-9=5*10^7Hz=50MHz*/

initial

begin

clk = 0;

clear = 1;

#15 clear = 0;

#1000 $stop; //要有终止时间,否则程序会一直运行

end

endmodule时间间的进制:1s=10^3ms=10^6us=10^9ns=10^12ps 秒、毫秒、微秒、纳秒、皮秒。

Verilog程序包括4个主要部分:端口定义、I/O说明、内部信号声明、功能定义。

一、端口定义

1、本模块应用:

在程序开始的端口定义部分,可以直接将I/O说明,内部信号声明整合到端口定义中去。用在always块里的参数要定义为reg型。

2、引用其他模块时:

用“.”符号,即

要调用的模块名 任意起名 (.端口1名(连接信号1名),.端口2名(连接信号2名),.。。。。。)

eg:muxtwo m (.out(outw), .a(ain), .b(bin), .s1(select)); //

这句话表示实例引用多路选择器,并加入测试信号流,以观察模块的输出out。其中,muxtwo是要调用的已经定义的(行为的或结构的)模块,m表示在本测试模块中有一个名为m的muxtwo的模块(可以随意取),其四个端口分别为:

.out(), .a(), .b(), .s1()

“.”表示端口,后面紧跟端口名,其名称必须与muxtwo模块定义的端口名一致。小括号里的信号名是与该端口连接的信号线名,是在本模块中定义的,说明其类型。

二、结构说明语句

Verilog语言中的任何过程模块都属于以下4种结构的说明语句:

(1)initial说明语句:在仿真开始时初始化各变量或者生成激励波形作为电路的仿真信号。

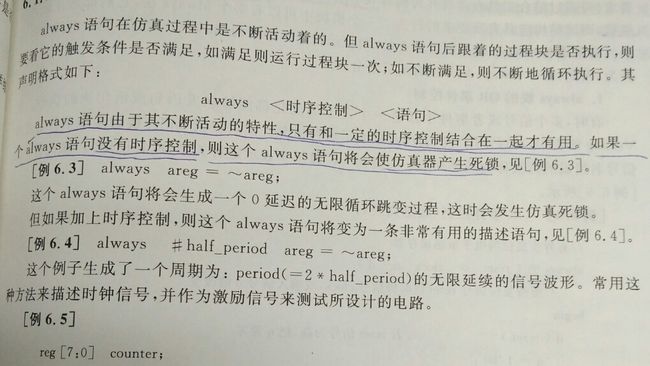

(2)always说明语句:和时序控制结合在一起,作为激励信号。或者做沿/电平触发。

(3)task说明语句

(4)function说明语句

一个程序模块可以有多个initial和always过程块。每个initial和always说明语句在仿真一开始同时立即执行,initial语句只执行一次,always语句会不断地重复执行直到仿真结束。但always语句后跟着的过程块是否运行,要看它的触发条件是否满足,满足就执行一次,再次满足则再次执行直到仿真结束。

注:一个模块中可有多个initial块,它们都是并行运行的。initial块常用于测试文件和虚拟模块的编写,用来产生仿真测试信号和设置信号记录等仿真环境。

三、条件语句——case语句

case语句是一种多分支选择语句,可直接处理多分支选择,常用于微处理器的指令译码,一般形式如下:

(1)case(表达式) //括号内的表达式称为控制表达式,其通常表示控制信号的某些位

分支表达式:语句 //分支表达式(常量表达式)则用这些控制信号的具体状态值来表示。

当控制表达式的值等于分支表达式的值时,执行分支表达式后面的语句。

若所有分支表达式的值都没有与控制表达式的值相匹配,就执行default后面的语句。

默认项(default项): 语句; //default项可有可无,一个case语句里只准有一个default项。

endcase

(2)casez(表达式)

即分支表达式: 语句;

默认项(default项): 语句;

endcase

(3)casex(表达式)

即分支表达式: 语句;

默认项(default项): 语句;

endcase

说明:

(1)每个case分项的分支表达式的值必须互不相同

(2)执行完case分项后的语句,则跳出该case语句结构,终止case语句的执行

(3)case语句的所有表达式值的位宽必须相等,这样控制表达式和分支表达式才能进行对应位比较。

注:不能用'bx,'bz来代替n'bx,n'bz.因为信号x(不定值),z(高阻值)的默认位宽是机器的字节宽度,通常是32位(此处n是case控制表达式的位宽)