F28335上实现浮点FFT

点击打开链接

硬件:

- ICETEK-F28335-A开发板 花了1900米买来,硬件和配套的软件(TI提供的例程加上一点icetek实验)都比较粗糙,文档错误不少,整个东东给人的感觉是匆忙的赶工出来的,不过总算有个可以跑的硬件平台,软件基本可以无视icetek的(除了存储器空间分配,不过icetek在这个问题上和我开了一个玩笑,拿到手的资料讲特别提到外部RAM映射到zone7,测试确怎么都不对,所以奇怪了好一阵,试了换到zone6才恍然大悟,icetek这样的错误也能犯,无语了)资料。

- SEEDDSP的USB510仿真器,由于SEEDDSP还未有正式版的驱动发布,所以向seeddsp的zag兄讨了一份测试版的驱动,几个月下来倒也没出什么问题。

软件:

开发环境:

- CCS3.3.54

- 浮点支持库 文件名: setup_C28XFPU_CSP_v3[1].3.1207.exe 下载地址: http://www.fs2you.com/files/e86a863a-57e2-11dd-9007-0014221b798a/

大小:5.7M

- C2000代码生成器 文件名: C2000CodeGenerationTools5[1].0.0Beta2.exe

下载地址: http://www.fs2you.com/files/c8217dd4-57e2-11dd-ac64-0014221b798a/

大小:12.4M

- 浮点信号处理库 提供了实时浮点fft算法 C28x Floating-Point Unit Library 1.00 Beta1 http://focus.ti.com.cn/cn/lit/sw/sprc624/sprc624.zip

安装好上述软件后,在ccs的component manager里边选择Code Composer Studio->build tools->tms320c28xx->选中Texas Instrument C2000 Code generation tools<5.0.0B2> 保存设置退出,Rebuild project,就不会出现下面的报错了。

WARNING: invalid compiler option --float_support=fpu32 (ignored)

C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\TI2323, line 24: error:

can't find input file 'rts2800_fpu32.lib'

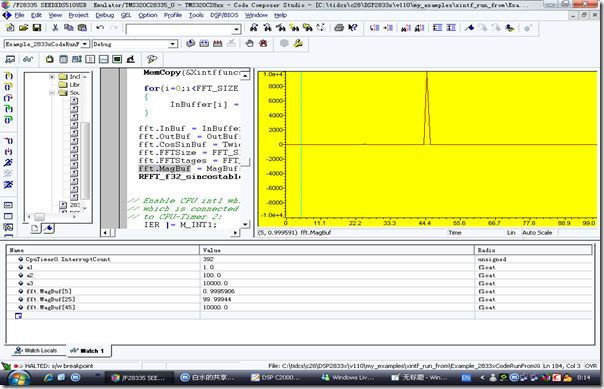

从外部存储器执行的FFT测试代码:fft输入数据和输出数据定位在外部存储器空间zone6, 包括FFT功能的timer0中断服务程序从zone6执行。

以下是代码:

//###########################################################################

//

// FILE: Example_2833xFFTExecuteFromXINTF.c

//

// TITLE: Example FFT Program That Executes From XINTF

//

// ASSUMPTIONS:

//

// This program requires the DSP2833x header files.

//

// As supplied, this project is configured for "boot to SARAM"

// operation. The 2833x Boot Mode table is shown below.

// For information on configuring the boot mode of an eZdsp,

// please refer to the documentation included with the eZdsp,

//

// $Boot_Table:

//

// GPIO87 GPIO86 GPIO85 GPIO84

// XA15 XA14 XA13 XA12

// PU PU PU PU

// ==========================================

// 1 1 1 1 Jump to Flash

// 1 1 1 0 SCI-A boot

// 1 1 0 1 SPI-A boot

// 1 1 0 0 I2C-A boot

// 1 0 1 1 eCAN-A boot

// 1 0 1 0 McBSP-A boot

// 1 0 0 1 Jump to XINTF x16

// 1 0 0 0 Jump to XINTF x32

// 0 1 1 1 Jump to OTP

// 0 1 1 0 Parallel GPIO I/O boot

// 0 1 0 1 Parallel XINTF boot

// 0 1 0 0 Jump to SARAM <- "boot to SARAM"

// 0 0 1 1 Branch to check boot mode

// 0 0 1 0 Boot to flash, bypass ADC cal

// 0 0 0 1 Boot to SARAM, bypass ADC cal

// 0 0 0 0 Boot to SCI-A, bypass ADC cal

// Boot_Table_End$

//

// DESCRIPTION:

//

// This example configures CPU Timer0 and increments

// a counter each time the timer asserts an interrupt.

//

// The ISR code is loaded into SARAM. The XINTF Zone 6 is

// configured for x16-bit data bus. A porition of the code including FFT

// is copied to XINTF for execution there.

//

// Watch Variables:

// CpuTimer0.InterruptCount

// InBuffer

// OutBuffer

// MagBuffer

//###########################################################################

// $TI Release: DSP2833x Header Files V1.10 $

// $Release Date: February 15, 2008 $

//###########################################################################

#include "DSP2833x_Device.h" // DSP2833x Headerfile

#include "DSP2833x_Examples.h" // DSP2833x Examples headerfile

#include "math.h"

#define PI 3.1415926

// This function will be loaded into SARAM and copied to

// XINTF zone 6 for execution

#pragma CODE_SECTION(cpu_timer0_isr,"xintffuncs");

//LED indicating the state of ISR execution

#define LED (*(unsigned short int *)0x180000)

//FFT Parameters

#include "FPU.h"

#define FFT_SIZE 1024 /* 32, 64, 128, 256, etc */

#define FFT_STAGES 10 /* log2(FFT_SIZE) */

/* Align the INBUF section to 2*FFT_SIZE in the linker file */

#pragma DATA_SECTION(InBuffer, "FFTBUF");

float32 InBuffer[FFT_SIZE];

#pragma DATA_SECTION(OutBuffer, "ZONE6DATA");

float32 OutBuffer[FFT_SIZE];

#pragma DATA_SECTION(TwiddleBuffer, "ZONE6DATA");

float32 TwiddleBuffer[FFT_SIZE];

#pragma DATA_SECTION(MagBuffer, "ZONE6DATA");

float32 MagBuffer[FFT_SIZE/2];

RFFT_F32_STRUCT fft;

float32 a1=1.0,a2=100.0,a3=10000.0;//amplitudes

float32 f1=5.00,f2=25.00,f3=45.00; //frequencies

// Prototype statements for functions found within this file:

void init_zone6(void);

interrupt void cpu_timer0_isr(void);

void main(void)

{

unsigned int i;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Interrupts that are used in this example are re-mapped to

// ISR functions found within this file.

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS; // This is needed to disable write to EALLOW protected registers

// Step 4. Initialize the Device Peripheral. This function can be

// found in DSP2833x_CpuTimers.c

InitCpuTimers(); // For this example, only initialize the Cpu Timers

// Configure CPU-Timer 0, 1, and 2 to interrupt every second:

// 100MHz CPU Freq, 1 second Period (in uSeconds)

ConfigCpuTimer(&CpuTimer0, 100, 10000);

// To ensure precise timing, use write-only instructions to write to the entire register. Therefore, if any

// of the configuration bits are changed in ConfigCpuTimer and InitCpuTimers (in DSP2833x_CpuTimers.h), the

// below settings must also be updated.

CpuTimer0Regs.TCR.all = 0x4001; // Use write-only instruction to set TSS bit = 0

// Step 5. User specific code, enable interrupts:

// Initalize XINTF Zone 6

init_zone6();

// Copy non-time critical code to XINTF

// This includes the following ISR functions: cpu_timer0_isr(), cpu_timer1_isr()

// The XintffuncsLoadStart, XintffuncsLoadEnd, and XintffuncsRunStart

// symbols are created by the linker. Refer to the F28335_ram_xintf.cmd file.

MemCopy(&XintffuncsLoadStart, &XintffuncsLoadEnd, &XintffuncsRunStart);

for(i=0;i { InBuffer[i] = a1 * sin(2 * PI * f1 * i / FFT_SIZE) + a2 * sin(2 * PI * f2 * i / FFT_SIZE)+a3 * sin(2 * PI * f3 * i / FFT_SIZE); } fft.InBuf = InBuffer; /* Input data buffer */ fft.OutBuf = OutBuffer; /* FFT output buffer */ fft.CosSinBuf = TwiddleBuffer;/* Twiddle factor buffer */ fft.FFTSize = FFT_SIZE; /* FFT length */ fft.FFTStages = FFT_STAGES; /* FFT Stages */ fft.MagBuf = MagBuffer; /* Magnitude buffer */ RFFT_f32_sincostable(&fft); /* Initialize twiddle buffer */ // Enable CPU int1 which is connected to CPU-Timer 0, CPU int13 // which is connected to CPU-Timer 1, and CPU int 14, which is connected // to CPU-Timer 2: IER |= M_INT1; // Enable TINT0 in the PIE: Group 1 interrupt 7 PieCtrlRegs.PIEIER1.bit.INTx7 = 1; // Enable global Interrupts and higher priority real-time debug events: EINT; // Enable Global interrupt INTM ERTM; // Enable Global realtime interrupt DBGM // Step 6. IDLE loop. Just sit and loop forever (optional): for(;;); } interrupt void cpu_timer0_isr(void) { unsigned int i; CpuTimer0.InterruptCount++; for(i = 0; i < FFT_SIZE; i++) { InBuffer[i] = a1 * sin( 2 * PI * f1 * i / FFT_SIZE) + a2 * sin( 2 * PI * f2 * i / FFT_SIZE)+a3*sin(2*PI*f3*i/FFT_SIZE); } RFFT_f32(&fft); /* Calculate output */ RFFT_f32s_mag(&fft); /* Calculate magnitude */ LED = CpuTimer0.InterruptCount; // Acknowledge this interrupt to receive more interrupts from group 1 PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; } // Configure the timing paramaters for Zone 7. // Notes: // This function should not be executed from XINTF // Adjust the timing based on the data manual and // external device requirements. void init_zone6(void) { // Make sure the XINTF clock is enabled SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; // Configure the GPIO for XINTF with a 16-bit data bus // This function is in DSP2833x_Xintf.c InitXintf16Gpio(); EALLOW; // All Zones--------------------------------- // Timing for all zones based on XTIMCLK = SYSCLKOUT XintfRegs.XINTCNF2.bit.XTIMCLK = 0; // Buffer up to 3 writes XintfRegs.XINTCNF2.bit.WRBUFF = 3; // XCLKOUT is enabled XintfRegs.XINTCNF2.bit.CLKOFF = 0; // XCLKOUT = XTIMCLK XintfRegs.XINTCNF2.bit.CLKMODE = 0; // Zone 6------------------------------------ // When using ready, ACTIVE must be 1 or greater // Lead must always be 1 or greater // Zone write timing XintfRegs.XTIMING6.bit.XWRLEAD = 1; XintfRegs.XTIMING6.bit.XWRACTIVE = 2; XintfRegs.XTIMING6.bit.XWRTRAIL = 1; // Zone read timing XintfRegs.XTIMING6.bit.XRDLEAD = 1; XintfRegs.XTIMING6.bit.XRDACTIVE = 3; XintfRegs.XTIMING6.bit.XRDTRAIL = 0; // don't double all Zone read/write lead/active/trail timing XintfRegs.XTIMING6.bit.X2TIMING = 0; // Zone will not sample XREADY signal XintfRegs.XTIMING6.bit.USEREADY = 0; XintfRegs.XTIMING6.bit.READYMODE = 0; // 1,1 = x16 data bus // 0,1 = x32 data bus // other values are reserved XintfRegs.XTIMING6.bit.XSIZE = 3; EDIS; //Force a pipeline flush to ensure that the write to //the last register configured occurs before returning. asm(" RPT #7 || NOP"); } //=========================================================================== // No more. //=========================================================================== /* // TI File $Revision: /main/1 $ // Checkin $Date: August 29, 2007 14:08:00 $ //########################################################################### // // FILE: 28335_RAM_xintf_lnk.cmd // // TITLE: Linker Command File For 28335 examples that run out of RAM // // This ONLY includes all SARAM blocks on the 28335 device. // This does not include flash or OTP. // // Keep in mind that L0 and L1 are protected by the code // security module. // // What this means is in most cases you will want to move to // another memory map file which has more memory defined. // //########################################################################### // $TI Release: DSP2833x Header Files V1.10 $ // $Release Date: February 15, 2008 $ //########################################################################### */ /* ====================================================== // For Code Composer Studio V2.2 and later // --------------------------------------- // In addition to this memory linker command file, // add the header linker command file directly to the project. // The header linker command file is required to link the // peripheral structures to the proper locations within // the memory map. // // The header linker files are found in // // For BIOS applications add: DSP2833x_Headers_BIOS.cmd // For nonBIOS applications add: DSP2833x_Headers_nonBIOS.cmd ========================================================= */ /* ====================================================== // For Code Composer Studio prior to V2.2 // -------------------------------------- // 1) Use one of the following -l statements to include the // header linker command file in the project. The header linker // file is required to link the peripheral structures to the proper // locations within the memory map */ /* Uncomment this line to include file only for non-BIOS applications */ /* -l DSP2833x_Headers_nonBIOS.cmd */ /* Uncomment this line to include file only for BIOS applications */ /* -l DSP2833x_Headers_BIOS.cmd */ /* 2) In your project add the path to library search path under project->build options, linker tab, library search path (-i). /*========================================================= */ /* Define the memory block start/length for the F28335 PAGE 0 will be used to organize program sections PAGE 1 will be used to organize data sections Notes: Memory blocks on F28335 are uniform (ie same physical memory) in both PAGE 0 and PAGE 1. That is the same memory region should not be defined for both PAGE 0 and PAGE 1. Doing so will result in corruption of program and/or data. L0/L1/L2 and L3 memory blocks are mirrored - that is they can be accessed in high memory or low memory. For simplicity only one instance is used in this linker file. Contiguous SARAM memory blocks can be combined if required to create a larger memory block. */ MEMORY { PAGE 0 : /* BEGIN is used for the "boot to SARAM" bootloader mode */ /* BOOT_RSVD is used by the boot ROM for stack. */ /* This section is only reserved to keep the BOOT ROM from */ /* corrupting this area during the debug process */ BEGIN : origin = 0x000000, length = 0x000002 /* Boot to M0 will go here */ BOOT_RSVD : origin = 0x000002, length = 0x00004E /* Part of M0, BOOT rom will use this for stack */ RAMM0 : origin = 0x000050, length = 0x0003B0 RAML0 : origin = 0x008000, length = 0x001000 RAML1 : origin = 0x009000, length = 0x001000 RAML2 : origin = 0x00A000, length = 0x001000 RAML3 : origin = 0x00B000, length = 0x001000 ZONE6A : origin = 0x100000, length = 0x00E000 /* XINTF zone 6 - program space */ CSM_RSVD : origin = 0x33FF80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */ CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */ ADC_CAL : origin = 0x380080, length = 0x000009 RESET : origin = 0x3FFFC0, length = 0x000002 IQTABLES : origin = 0x3FE000, length = 0x000b50 IQTABLES2 : origin = 0x3FEB50, length = 0x00008c FPUTABLES : origin = 0x3FEBDC, length = 0x0006A0 BOOTROM : origin = 0x3FF27C, length = 0x000D44 PAGE 1 : RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */ RAML4 : origin = 0x00C000, length = 0x001000 RAML5 : origin = 0x00D000, length = 0x001000 RAML6 : origin = 0x00E000, length = 0x001000 RAML7 : origin = 0x00F000, length = 0x001000 ZONE6B : origin = 0x10E000, length = 0x002000 /* XINTF zone 6 - data space */ } SECTIONS { /* Setup for "boot to SARAM" mode: The codestart section (found in DSP28_CodeStartBranch.asm) re-directs execution to the start of user code. */ codestart : > BEGIN, PAGE = 0 ramfuncs : > RAML0, PAGE = 0 .text : > RAML1, PAGE = 0 .cinit : > RAML0, PAGE = 0 .pinit : > RAML0, PAGE = 0 .switch : > RAML0, PAGE = 0 xintffuncs : LOAD = RAML1, RUN = ZONE6A, LOAD_START(_XintffuncsLoadStart), LOAD_END(_XintffuncsLoadEnd), RUN_START(_XintffuncsRunStart), PAGE = 0 .stack : > RAMM1, PAGE = 1 .ebss : > RAML4, PAGE = 1 .econst : > RAML5, PAGE = 1 .esysmem : > RAMM1, PAGE = 1 IQmath : > RAML1, PAGE = 0 IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD FPUmathTables : > FPUTABLES, PAGE = 0, TYPE = NOLOAD DMARAML4 : > RAML4, PAGE = 1 DMARAML5 : > RAML5, PAGE = 1 DMARAML6 : > RAML6, PAGE = 1 DMARAML7 : > RAML7, PAGE = 1 FFTBUF ALIGN( 2048 ) : { } > RAML6 PAGE 1 //FFTBUF ALIGN( 2048 ) : { } > ZONE6B PAGE 1 ZONE6DATA : > ZONE6B, PAGE = 1 .reset : > RESET, PAGE = 0, TYPE = DSECT /* not used */ csm_rsvd : > CSM_RSVD PAGE = 0, TYPE = DSECT /* not used for SARAM examples */ csmpasswds : > CSM_PWL PAGE = 0, TYPE = DSECT /* not used for SARAM examples */ /* Allocate ADC_cal function (pre-programmed by factory into TI reserved memory) */ .adc_cal : load = ADC_CAL, PAGE = 0, TYPE = NOLOAD } /* //=========================================================================== // End of file. //=========================================================================== */ 结果截图如下: