I2C协议研读(一):规范介绍和基本概念

写在开始,因工作需要,对I2C的spec文档进行研读,主要工作就是将规范翻译为中文并补充自己的理解,根据每个章节内容进行划分,便于以后查阅,如有错误和疑问欢迎指正交流。

目录

1.规范介绍:INTRODUCTION TO THE I2C-BUS SPECIFICATION

2.基本概念:THE I2C-BUS CONCEPT

3.一般特征:GENERAL CHARACTERISTICS

4.位传输:BIT TRANSFER

5.数据传输:TRANSFER DATA

6.仲裁和时钟同步:ARBITRATION AND CLOCK GENERATION

7.7位地址格式:FORMATS WITH 7-BIT ADDRESSES

8.7位寻址:7-BIT ADDRESSING

9.标准模式的扩展:EXTENSIONS TO THE STANDARD-MODE I2C-BUS SPECIFICATION

10.快速模式:FAST-MODE

11.高速模式:HS-MODE

12.十位寻址:10-BIT ADDRESSING

13.电气规范:ELECTRICAL SPECIFICAITONS AND TIMING FOR I/O STAGES AND BUS LINES

14.总线设备和总线的电气连接:ELECTRICAL CONNECTION OF I2C-BUS DEVICES TO THE BUS LINES

一些特征:

1.仅需要两根总线:数据总线SDA和时钟总线SCL

2.连接到总线的每个设备都是可通过唯一地址进行软件寻址,并且始终存在简单的主/从关系。 主机可以用作主机发送器或主机接收器。

3.它是真正的多主机总线,包括冲突检测和仲裁功能,以防止两个或多个主机同时启动数据传输时的数据损坏。

4.串行,面向8位的双向数据传输在标准模式下可以达到100 kbit / s,在快速模式下可以达到400 kbit / s,在高速模式下可以达到3.4 Mbit / s。

5.片上滤波可抑制总线数据线上的尖峰,以保持数据完整性。

6.可连接至同一总线的IC的数量仅受最大总线电容400 pF的限制。

1.规范介绍:INTRODUCTION TO THE I2C-BUS SPECIFICATION

对于面向8位的数字控制应用(例如需要微控制器的应用),可以建立某些设计标准:

1.一个完整的系统通常包含至少一个微控制器和其他外围设备,例如存储器和I / O扩展器。

2.必须将连接系统内各种设备的成本降至最低

3.执行控制功能的系统不需要高速数据传输

4.整体效率取决于所选的设备以及互连总线结构的性质

为了生产满足这些标准的系统,需要串行总线结构。 尽管串行总线不具备并行总线的吞吐能力,但它们确实需要更少的布线和更少的IC连接引脚。 但是,总线不仅是互连线,还体现了系统内通信的所有格式和过程。

在串行总线上相互通信的设备必须具有某种形式的协议,该协议应避免出现混淆,数据丢失和信息阻塞的所有可能性。快速设备必须能够与慢速设备通信。该系统不得依赖于与其相连的设备,否则将无法进行修改或改进。还必须设计一个程序来决定哪个设备将控制总线以及何时控制总线。 并且,如果将具有不同时钟速度的不同设备连接到总线,则必须定义总线时钟源。

所有这些标准都包含在I2C总线的规范中。

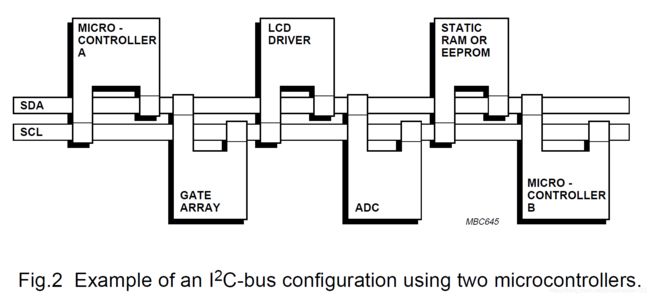

2.基本概念:THE I2C-BUS CONCEPT

I2C总线支持任何IC制造工艺(NMOS,CMOS,双极性)。 两条数据线,即串行数据(SDA)和串行时钟(SCL),在连接到总线的设备之间传递信息。 每个设备都有一个唯一的地址(无论是微控制器,LCD驱动器,内存还是键盘接口),并且可以根据设备的功能用作发送器或接收器。显然,LCD驱动器只是接收器,而存储器可以接收和发送数据。 除了发送器和接收器外,在执行数据传输时,设备也可以视为主机或从机。 主设备是启动总线上的数据传输并生成时钟信号以允许该传输的设备。 那时,任何寻址的设备都被视为从设备。

| TERM | DESCRIPTION |

| Transmitter | the device which sends data to the bus |

| Receiver | the device which receives data from the bus |

| Master | the device which initiates a transfer, generates clock signals and terminates a transfer |

| Slave | the device addressed by a master |

| Multi-master | more than one master can attempt to control the bus at the same time without corrupting the message |

| Arbitration仲裁 | procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the winning message is not corrupted确保如果一个以上的主机同时尝试控制总线,则仅允许一个主机这样做,并且获胜消息不会被破坏 |

| Synchronization同步化 | procedure to synchronize the clock signals of two or more devices同步两个或更多设备的时钟信号的过程 |

I2C总线是一个多主机总线,这意味着可以连接一个以上的能够控制总线的设备。主机多为微控制器,考虑连接到I2C总线上的两个微控制器之间的数据传输。

上图强调了I2C总线上主机-从机和接收器-发送器之间的关系,这种关系并不是永久的,仅取决于数据传输方向。

数据传输如下:

1)假设微控制器A要发送数据给微控制器B:

微控制器A(主机)寻址微控制器B(从机)

微控制器A(主机-发送器)发送数据给微控制器B(从机-接收器)

微控制器A终止传输

2)如果微控制器A要接收数据从微控制器B:

微控制器A(主机)寻址微控制器B(从机)

微控制器A(主机-发送器)接收数据从微控制器B(从机-接收器)

微控制器A终止传输

总线上连接一个以上的微控制器时,有可能多个控制器同时尝试初始化传输数据,因此为了避免产生混乱,利用仲裁来决定主机,即如果多个控制器尝试发送信息到总线,在其他控制器都产生“0”的情况下,首先产生“1”的控制器将丢失仲裁。

主设备始终负责在I2C总线上生成时钟信号。 每个主机在总线上传输数据时都会产生自己的时钟信号。 来自主机的总线时钟信号只有在通过慢速从动设备按住时钟线来延长信号时才可以更改,或者在发生仲裁时被另一个主机改变。