I2C协议研读(八)

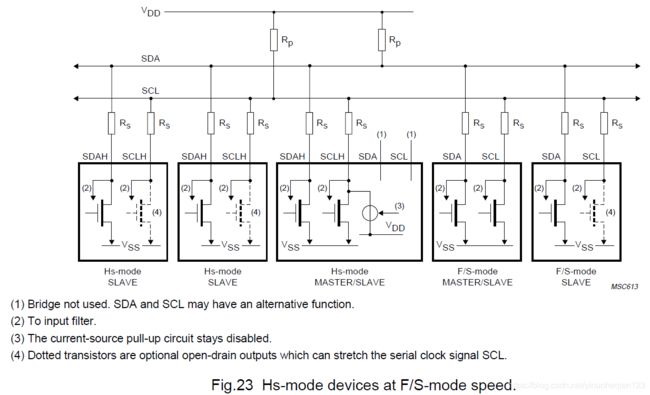

11.4 低速模式下的高速模式设备:Hs-mode devices at lower speed modes

高速模式的设备全部向下兼容,并且可以连接到F/S模式的I2C总线系统中。这样的配置下,任何主机码不能传输,所有Hs模式主机均保持F / S模式,并且在禁用电流源的情况下以F / S模式速度进行通信。SDAH和SCLH引脚用来连接到F/S模式的总线系统上,允许高速模式主机设备上的SDA和SCL引脚用于其他功能。

11.5 一条串行总线系统中的混合速度模式:Mixed speed modes on one serial bus system

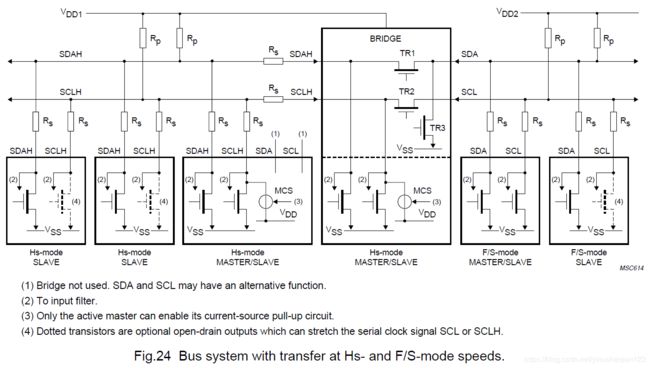

如果一个系统中集合了高速、快速和标准模式的设备,利用内部连接桥(interconnection bridge)使得不同的设备之间有不同的比特率是有可能的。

其中一个桥需要在合适的时间连接或者断开高速模式部分和F/S模式部分,该桥具有电平转换功能,可连接具有不同供电电压的设备。例如,如果SDA和SCL引脚允许5 V的电压,VDD2为5V的F/S模式设备可以和VDD1为3V或更少的Hs模式设备进行连接。该桥集成在Hs模式主机设备里,并且由串行信号SDAH、SCLH、SDA和SCL完全控制。这样的桥可以在任何IC中实现为自主电路。

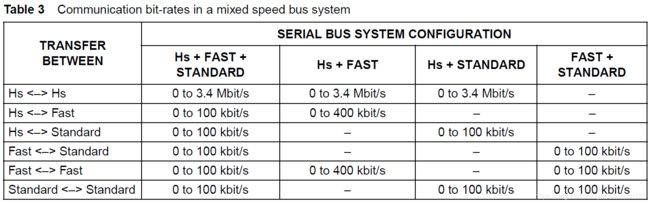

TR1/TR2/TR3是N通道晶体管。TR1和TR2有一个传输门功能,TR3是一个开漏下拉阶段。如果TR1或TR2导通,则它们在两个方向上都传递低电平,否则,当漏极和源极都升高到高电平时,每个导通的晶体管的漏极和源极之间将具有高阻抗。后一种情况,在F / S模式速度下,由于SDAH和SCLH将被上拉至VDD1,而SDA和SCL将被上拉至VDD2,这些晶体管将用作电平转换器。Hs模式主机之一上的桥将SDAH和SCLH线连接到相应的SDA和SCL线,从而允许Hs模式设备以较低的速度与F / S模式设备通信。如第8节所述,在所有连接的设备之间进行总F / S模式传输期间,可以进行仲裁和同步。但是,在Hs模式传输期间,桥接器打开以分隔两个总线部分,并允许Hs模式设备以3.4 Mbit / s的速度相互通信。Hs模式设备和F / S模式设备之间的仲裁仅在主代码(00001XXX)期间执行,并且通常由一个Hs模式主设备赢得,因为没有从机地址具有四个leading zero。其他主机只有发送保留的8位代码(00000XXX)才能赢得仲裁。 在这种情况下,桥保持关闭状态,并且传输以F / S模式进行。 表3给出了这种系统中可能的通信速度。

11.5.1 F/S-MODE TRANSFER IN A MIXED-SPEED BUS SYSTEM

图24所示的桥将对应的串行总线线路互连,从而形成一个串行总线系统。 由于未发送主代码(00001XXX),因此电流源上拉电路保持禁用状态,所有输出级均为漏极开路。 所有设备(包括Hs模式设备)均根据F / S模式I2C总线规范的协议,格式和速度相互通信。

11.5.2 HS-MODE TRANSFER IN A MIXED-SPEED BUS SYSTEM

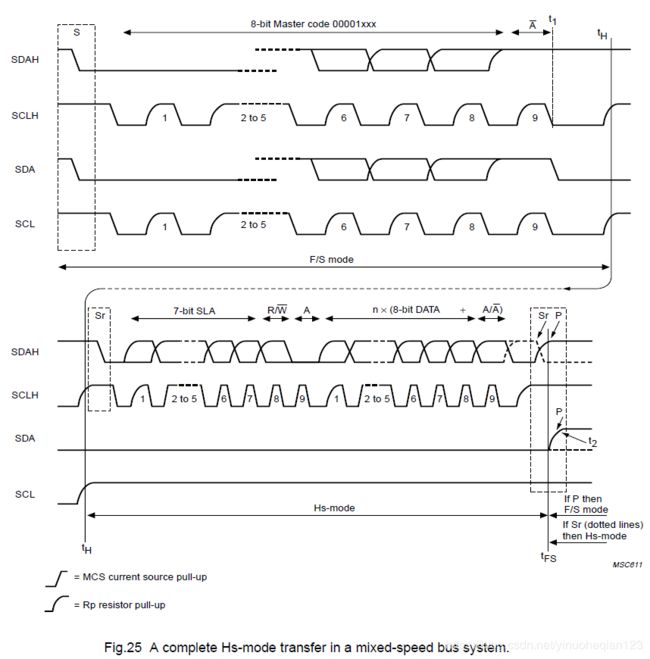

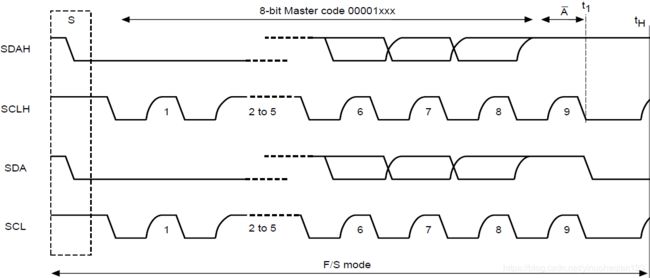

图25显示了完整的Hs模式传输的时序图,该模式由START条件,主机码和非确认A(以F / S模式速度)调用。 尽管该时序图分为两部分,但应将其视为一个时序图,时间点tH是这两部分的共同点。

主机码被活跃或非活跃主机里的桥识别(图24),桥扮执行了如下动作:

1)在t1和tH之间(图25),在晶体管TR3关闭来下拉SDA线到VSS后,TR1晶体管开启来分离SDAH和SDA线。

2)SCLH和SCL全为高电平后(tH时刻在图25中),晶体管TR2开启来分离SCLH和SCL线。开始条件后SCLH变为低电平之前,TR2必须开启。

伴随着一个重复的START起始条件,在tH 之后开始高速模式传输。在高速模式传输期间,SCL线保持高电平,SDA线保持在稳态低电平,就是说已经准备好传输的停止条件了。

在每个响应或非响应位后,活跃主机disable电流源上拉电路。这就使能了其他的设备通过延长SCLH信号的低电平周期来延迟串行传输。当所有器件都被释放并且SCLH信号达到HIGH电平时,活跃主机再次重新启用其电流源上拉电路,从而加快了SCLH信号上升时间的最后一部分。非常规情况下,任何时间F/S模式设备可以通过拉低SCL线至少1微秒来关闭这个桥(TR1和TR2关闭,TR3开启)to recover from a bus hang-up。

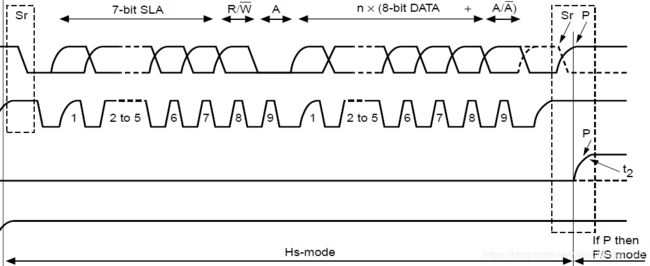

高速模式以停止条件结束,并将总线系统带回F/S模式。在SDAH上检测到停止条件(tFS在图25中)后,活跃主机disable电流源MCS。桥同时识别到停止条件并进行如下动作:

1)在tFS后关闭晶体管TR2来通过SCL连接SCLH;此刻SCL和SCLH都为高电平。tFS后晶体管TR3开启,释放SDA线并允许其被上拉电阻Rp拉高。这就是F/S模式设备的停止条件。TR3必须开启足够快,以保证停止条件和最早的下一个开始条件之间的空闲时间满足快速模式规范。

2)SDA到达高电平(图25中的t2),晶体管TR1关闭来通过SDA连接SDAH。(note:当所有线路为高电平时进行互连,从而防止总线线路出现尖峰)根据快速模式规范,TR1和TR2必须在最短总线空闲时间内关闭(详见表5中的tBUF)。

11.5.3 TIMING REQUIREMENTS FOR THE BRIDGE IN A MIXED-SPEED BUS SYSTEM

从图25可以看出,电桥在t1,tH和tFS处的动作必须非常快,以至于不影响SDAH和SCLH线。此外,电桥必须满足SDA和SCL线路的快速模式规范的相关时序要求。