EDA笔记(9)--基本逻辑电路

目录

一.译码器和编码器的设计

1.电路设计思路

2.VHDL程序设计--3线-8线译码器(高电平有效)

3.设计总结扩展

1.译码器

2.编码器

二.选择器和驱动电路的设计

1.选择器--电路设计思路

2.选择器--VHDL程序设计

3.选择器--设计总结拓展

1.驱动电路--电路设计思路

2.驱动电路--VHDL程序设计

3.驱动电路--设计总结扩展

三.触发器和寄存器的设计

1.电路设计思路

2.VHDL程序设计

3.设计总结与扩展

四.计数器电路的设计

1.电路设计思路

2.VHDL程序设计

3.设计总结与扩展

五.分频电路的设计

1.电路设计思路

1.分频电路的含义

2.分频电路的本质

3.分配电路的设计

2.VHDL程序的设计

3.设计总结与扩展

六.FIFO存储器电路设计

1.电路设计思路

2.VHDL程序设计

3.设计总结与扩展

一.译码器和编码器的设计

1.电路设计思路

1.译码器和编码器,都是用来将一种信息代码转换成另一种信息代码的电路,只是功能恰好相反。

译码器,是把输入的特定数码的含义“翻译”出来,给出对应的一系列输出信号的电路。

编码器,将选定的一系列二值代码,赋予每个代码以固定的含义的电路。对于二进制编码器,就是将2N个分离的信息代码,以N个二进制码来表示。

2.译码器和编码器的设计,我们可根据给定的条件,使用IF条件语句或CASE选择语句等顺序语句进行转换,也可使用条件信号赋值语句或选择信号赋值语句等并行语句进行转换。还可使用预先给定一个初始的信息,再进行各种变换。

2.VHDL程序设计--3线-8线译码器(高电平有效)

跳转链接:

3.设计总结扩展

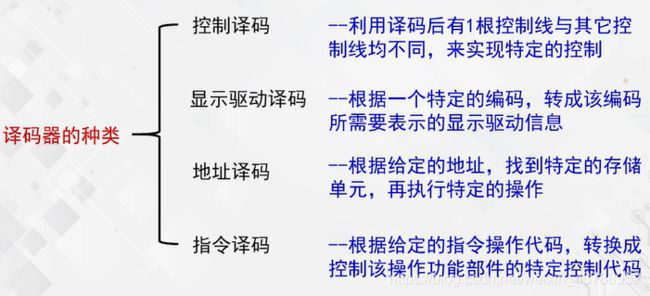

1.译码器

2.编码器

编码器,需先根据输入信号的位数,确定编码器的输出位数,然后,根据需要进行相应的编码。

对于优先编码器,主要用于控制,只要出现了某个优先级高的信号,不管其它信号是否出现,这时就要输出一个特定的编码,也就是根据该编码信号还原译码后,要执行1个特定的操作。

3.其实编码器也可看成是压缩电路,译码器也可看成解压缩电路。传送数据前,先用编码器压缩数据后再传送出去,接受端则由译码器将数据解压缩,还原原来的内容。

二.选择器和驱动电路的设计

1.选择器--电路设计思路

选择器常用于多路信号的切换或多路数据的选择。因此选择器的设计,主要是根据选择控制信号的不同,在多路信号或多路数据中,选择其中的1路信号或1路数据输出。

具体使用的VHDL语句,常用的有IF条件语句和CASE选择语句等。

2.选择器--VHDL程序设计

跳转链接:

3.选择器--设计总结拓展

1.选择器常用于多路信号的切换或多路数据的选择。其中用于多路信号的切换的选择器,其输入和输出均是1位,而用于多路数据切换的选择器,其输入和输出都是N位。

2.选择器的设计,其控制信号的位数,决定于输入信号的多少,如果输入信号为N位,控制信号为M根,则2^M=N。

1.驱动电路--电路设计思路

1.三态门和总线缓冲器是驱动电路经常用到的器件。三态门电路的输出,包括高电平、低电平、高阻态三种。

在微型计算机的总线驱动中经常要用单向总线缓冲器,它通常由多个三态门组成,用来驱动地址总线和控制总线。双向总线缓冲器用于数据总线的驱动和缓冲,典型的双向总线缓冲器有两个数据输入/输出端A和B、一个方向控制端DIR和一个选通端EN。EN=0时双向缓冲器选通。若DIR=0,则A=B;反之则B=A。

2.对于三态门和总线缓冲器的设计,主要是根据控制信号的不同,输出对应的值。因此可使用IF条件语句和CASE选择语句描述。

2.驱动电路--VHDL程序设计

跳转链接:

3.驱动电路--设计总结扩展

1.总线缓冲器,具有多功能,通过增加控制信号,利用不同的值实现多功能。

2.对于多功能硬件电路的设计,在电路内部,每一个功能具有一个相应的硬件与其对应,只是封装后对外而言具有多功能。

三.触发器和寄存器的设计

1.电路设计思路

1.触发器,就是能够存储1位二值信号的基本单元电路。触发器的基本操作,就是每当时钟信号上升沿或下降沿到来时,将保存在输入端的1位数据输出到输出端。它包括基本R-S触发器、D触发器、JK触发器、T触发器等。

2.寄存器用于寄存一组二值代码,可用N个触发器组成的寄存器能储存一组N位的二值代码。寄存器的基本操作,就是每当时钟信号上升沿或下降沿到来时,将寄存在输入端的N位数据输出到输出端。

3.移位寄存器除了具有存储代码的功能以外,还具有移位功能。因此,移位寄存器不但可以用来寄存代码,还可用来实现数据的串/并转换、数值的运算以及数据处理等。

4.触发器与寄存器(锁存器)的区别,就是数据的位数不一样。在实际的触发器和寄存器的设计中,根据需要,可能需要加上复位、置位、初始输入等功能。

2.VHDL程序设计

跳转链接:

3.设计总结与扩展

1.触发器和寄存器(锁存器),都是具有存储功能的电路,设计的基本方法是相同的。触发器与寄存器(锁存器)的区别,就是数据的位数不一样,触发器是1位,寄存器是N位。

2.在触发器和寄存器(锁存器)的实际设计中,除了具备基本的寄存功能外,根据需要,可能需要加上复位、置位、初始输入、数据传输、移位等功能。

3.触发器和寄存器(锁存器)的设计的基本功能,就是使用进程来描述,在进程内部,主要是使用IF条件语句和CASE选择语句来描述。如果满足某个条件,则执行相应的操作。

四.计数器电路的设计

1.电路设计思路

1.计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于定时、分频、产生节拍脉冲和脉冲序列以及进行数字运算等。

2.计数器的设计,其基本操作包括2个:一个是计数操作;一个是进位控制。

根据需要可增加复位、置位、赋初值等操作。

3.计数操作和进位控制,都可以使用进程来实现。其中计数又分为正常计数和边界处理,正常计数是进行加1操作或加N操作;边界处理则进行清零。

2.VHDL程序设计

跳转链接:

3.设计总结与扩展

1.对于计数范围超过4位2进制的计数器,为了简化设计和便于显示译码,一般可分解为一系列10以内进制的计数器级联而成。

2.对于进位输出的控制,有时会产生毛刺,这时可增加1个同步控制时钟信号条件去毛刺。

3.对于具有多功能的计数器,就是在原有计数控制条件的基础上,增加相应的控制条件,控制条件的位数,需要根据功能的多少来决定。假若位数为N,功能为M,则2^N=M.

五.分频电路的设计

1.电路设计思路

1.分频电路的含义

在基于EDA技术的数字电路系统设计中,分频电路应用得十分广泛,常常使用分频电路来得到数字系统中各种不同频率的控制信号。所谓分频电路,就是将一个给定的频率较高的数字输入信号,经过适当的处理后,产生一个或数个频率较低的数字输出信号。

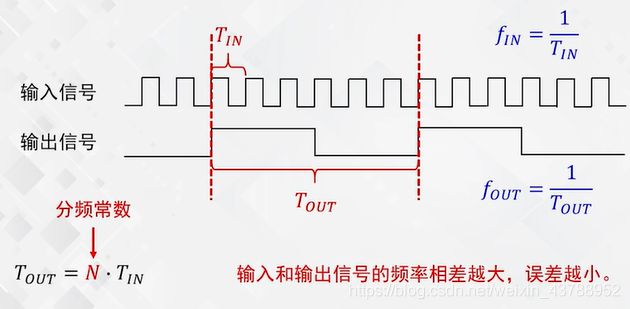

2.分频电路的本质

计算出分频常数N后,分频电路本质上是计数器的变种,其计数值由分频常数N=Fin/Fout 决定,其输出不是一般计数器的计数结果,而是根据分频常数对输出信号的高、低电平进行控制的。

3.分配电路的设计

如果已知分频电路分频前后的频率,则可计算出分频常数N。

如果分频信号对占空比有要求,那么根据占空比RATE我们可算出Nh。

分频电路的设计方法:

(1)如果分频信号对占空比没要求,则分频器可按如下方法设计:

控制信号的产生:输入信号的每个上升沿到来时,进行加1操作,一直计数到N-1为止。

输出的控制:根据控制信号的产生结果,输出低电平或高电平。

2.VHDL程序的设计

跳转链接:

3.设计总结与扩展

六.FIFO存储器电路设计

1.电路设计思路

半导体存储器的种类很多,从功能上可以分为只读存储器(简称ROM)和随机存储器(简称RAM)两大类。具有先进先出存储规则的读写存储器,又称为先进先出栈(FIFO)。

FIFO是先进先出栈,作为数据缓冲器,通常其数据存放结构完全与RAM一致,只是存取方式有所不同,也就是相当于1个数据通道,先存进的数据,先读出去。

作为FIFO的设计,它包括数据的写操作、数据的写地址修改、数据写满控制,数据的读操作、数据的读地址修改、数据读空控制,因此可用6个进程来描述对应的操作。

2.VHDL程序设计

跳转链接:

3.设计总结与扩展

1.存储器的设计,首先应确定存储单元的数据位数(N)、存储单元的个数/深度(D)、存储器寻址的地址根数(M)。其中D=2^M。

2.存储器的数据类型,本质上就是一个二维数组,可理解成一个具有N位数据,有D个单元的二维数组。

3.存储器的存储操作,实际上就是根据给定的地址,找到对应的存储单元,再将外部端口的有关数据存入指定的存储单元,或将指定单元的数据送到外部端口。

4.存储器进行存取操作时,需要给出存取地址。存取地址可能每一次操作进行加减1操作,也可能是根据特定的存取操作规律进行加减N操作。

5.可读可写存储器,要注意读空或写满的问题,这时可设定控制标志进行区分。