UVM概述及uvm_component和uvm_object(一)

UVM:Universal Verification Methodology(通用验证方法学)

UVM:是建立在systemverilog平台上的一个库,提供了一系列的接口,让我们能够更方便的进行验证。

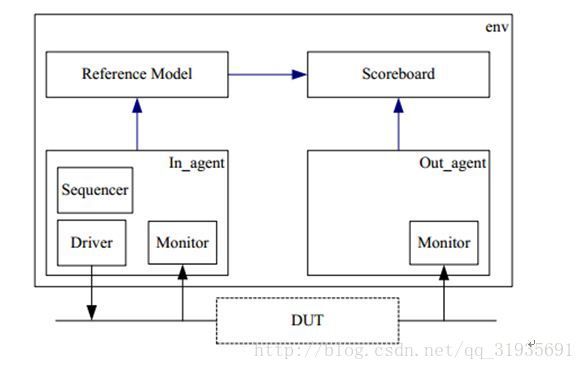

验证平台组成:

Driver:用来把不同的激励施加给DUT;

Monitor:用来检测DUT的输出;

Scoreboard:专门用来比较期望值与monitor检测到的DUT输出;

Reference model:输入跟DUT完全一样,它的输出送给scoreboard。用于和DUT的输出比较。

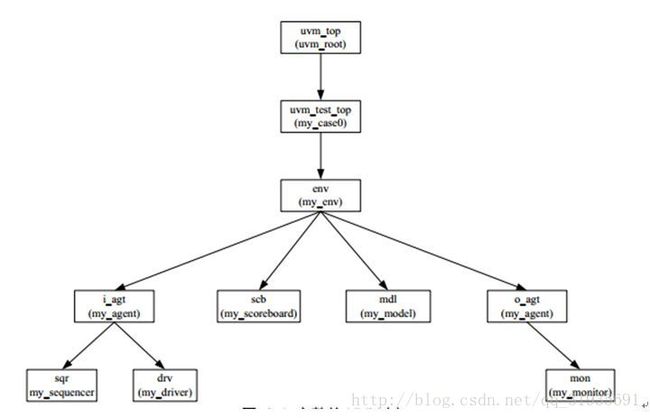

UVM验证平台的树形结构:

Driver负责给DUT发送数据,sequencer用于产生这些数据,一个sequencer通过启动一个sequence,从sequence获取数据,并把这些数据转交给driver。

Agent只是简单的吧driver、monitor、sequencer封装在一起。Agent对应的是物理接口协议,不同的接口协议对应不同的agent。在一个验证平台中通常会存在多个agent。

Env相当于一个特大容器,把所有的uvm_component都包含在其内部作为其成员变量。

实际验证平台:

类的定义与实例化:

类的定义:及编辑器写的:class A;……………….endclass

类的实例化:及A a_inst;a_inst = new();

类的定义相当于通知systemverilog仿真器,可能要用到这样一个类,类的实例化在于通过new(),来通知systemverilog仿真器开辟空间。一个类,只定义而不实例化,是没有任何意义。

Uvm_component和uvm_object::

Uvm_component特点:在new的时候,需要指定一个类型为uvm_component,名字是parent的变量:

Function new(string name,uvm_component parent);

在一般使用的时候,若在类A 中有uvm_component B,则在A中定义如下:

B=new(“B”,this);

完整UVM树:

uvm树根是uvm_top。

Uvm_component的另外一个特点是它具有phase自动执行的特性。

Uvm_component的两大特性:

1、 通过在new的时候指定parent来形成一种树形的组织结构

2、 有phase的自动执行特点

UVM中常用类的继承关系:

除了driver、monitor、agent、model、scoreboard、env之外全部用uvm_object。

常用的uvm_component:

Uvm_driver:所有driver都要派生uvm_driver。Driver的功能主要就是向sequencer索要sequence_item(transaction),并把sequence_item里的信息驱动到DUT的接口上。相当于完成了transaction级别到DUT能够接受的pin级别信息的转变。

Uvm_monior:所有monitor都要派生子uvm_monitor。Monitor从DUT的pin上接收数据,并且把接收到的数据转换成transaction级别的sequence_item,并把转换后的数据发送给scoreboard,供scoreboard比较。

Uvm_sequencer:所以的sequencer都要派生自uvm_sequencer。其功能1就是组织管理sequence,当driver要求数据时,他就把sequence生成sequence_item转发给driver。

Uvm_scoreboard:一般的scoreboard都要派生自uvm_scoreboard。其功能就是比较reference model和monitor分别发送来的数据,根据比较结果判断DUT是否正确。

Reference model:reference model直接派生自uvm_component。其作用就是模仿DUT,完成与DUT相同的功能,可以直接使用systemverilog的特性,或者可以通过DPI等接口调用其它语言来完成与DUT相同功能。

Uvm_agent:所以agent都要派生自uvm_agent。只是把driver和monitor封装在一起,根据参数来决定是只实例化monitor还是要实例化driver和monitor。

Uvm_env:所有env都要派生自uvm_env。把验证平台固定不变的component封装在一起。这样在要跑不同case时,只要在case中实例化一个env就可以。

Uvm_test:所有的case都要派生自uvm_test。Case之间差异很大,所以从uvm_test派生出来的类各不同。任何一个派生的case都要实例化env,只有这样才能正常传数。

常用uvm_object:

Uvm_sequence_item:所有的transaction要从uvm_sequence_item派生。

Uvm_sequence:所有的sequence要从uvm_sequenc派生一个。Sequence就是sequence_item的组合。Sequence和sequencer直接打交道。当driver向sequencer索要数据时,sequencer会转而向sequence要数据,当sequence发现有sequence_item时,则将数据传输过来。

Config:所有config一般直接从uvm_object派生。Config的主要功能就是规范验证平台的行为方式。

Uvm_phase:派生自uvm_object,其作用是控制uvm_component的行为方式。