spi实验:接收电路与发送电路的自环测试

SPI简介:

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线。

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制次设备 (Slave). 一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选 (Slave Select) 来控制多个 Slave 设备, SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本身不能产生或控制 Clock, 没有 Clock 则 Slave 设备不能正常工作。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU与各种外围器件进行全双工、同步串行通讯。

SPI相关的缩写或说法:

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

(2) CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

(3) SCK=SCLK=SPI的时钟

(4) Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)

对于一个时钟周期内,有两个edge,分别称为:

Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

Trailing edge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

本实验默认设置CPOL=0,CPHA=0。

实验要求:

按照SPI原理设计一个接收电路与一个发送电路,并作为从机进行自环测试。

实验过程:

SPI的特点即外部从机串行输入输出数据,而主机可以并行读取写入数据。一个SPI从机必需四个输入信号:sck——串行同步时钟;ncs——片选信号;mosi——主机输出从机输入信号;miso——主机输入从机输出信号。同时还需要一个clk时钟信号和一个rst复位信号。

本实验共分为三个部分:myspi从机模块,bcd2led输出数据显示模块,sck_counter串行同步脉冲生成模块。

1.从机模块:

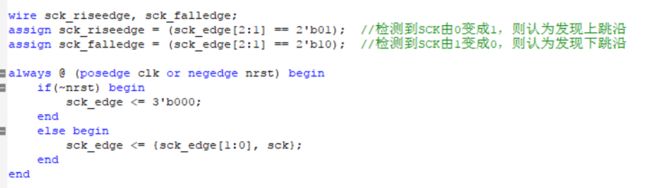

从机模块又分为三个部分:sck跳变沿检测部分,spi接收部分,spi发送部分。

sck跳变沿检测部分:使用寄存器记录SCK状态,由状态判断SCK是否出现跳变沿。代码截图如下:

spi接收电路部分:当复位信号无效、片选信号有效且出现SCK上跳沿时,接收电路进入状态一,接收寄存器(8位)通过左移方式存入mosi数据,存满8位后进入状态二,将接收标志信号置为1,等待4个时钟周期后进入状态三,将接收标志信号清零并返回状态一。具体代码截图如下:

spi接收电路部分:当复位信号无效、片选信号有效且出现SCK上跳沿时,接收电路进入状态一,接收寄存器(8位)通过左移方式存入mosi数据,存满8位后进入状态二,将接收标志信号置为1,等待4个时钟周期后进入状态三,将接收标志信号清零并返回状态一。具体代码截图如下:

spi发送电路部分:当接收标志信号置1时发送标志信号也置为1。当复位信号无效、片选信号有效且发送标志信号为1时,发送电路进入状态一,发送寄存器从数据缓存区中读出8位数据进入状态二,如果出现出现SCK上跳沿则从发送寄存器中取出最高位作为miso发送,进入状态三,如果出现出现SCK下跳沿则将发送寄存器左移一位,最低位写入0,直至发送寄存器中8位数据全部发送完毕,进入状态四,将发送标志信号和miso信号都置为0,返回状态一。具体代码截图如下:

2. 输出数据显示模块:

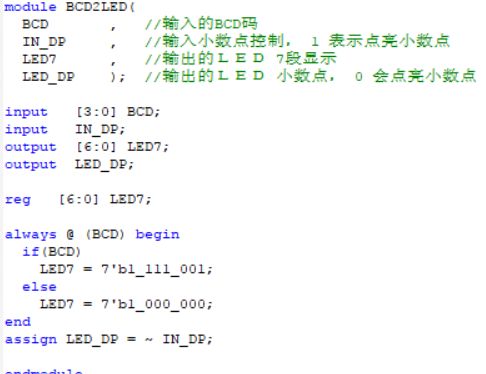

将从机模块输出的miso信号传入数据显示模块中,若miso为1则时七段液晶显示管显示数字1,若miso为0则显示数字0,。具体代码截图如下:

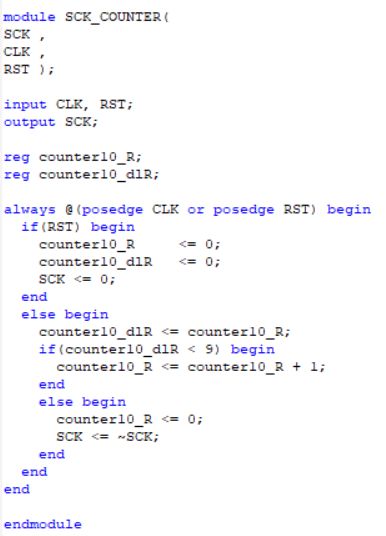

3.sck脉冲生成模块:

每10次clk时钟周期使SCK信号跳反一次,该sck信号作为从机模块的sck输入信号。具体实现代码截图如下:

代码编写完成后管脚分配截图如下:

把代码下载DE0开发板后置SW0高电平,SW1低电平,SW2控制输入数据,手动按BUTTON28次后存入对应8位数据,再手动按8次对应显示上次输入的8位数据。