SDRAM时序分析-基于signalTapII

SDRAM时序分析-基于signalTapII

背景:利用FPGA驱动SDRAM,本篇是时序仿真部分,理论理解详见上传文件;

修改部分:

1、刷新周期:改为64ms/(2^13)=7.8125us

2、读命令的启动条件:sdram初始化完成后启动

3、SDRAM读出的数据写入到FIFO中的写入请求信号提前一个时钟使能;

4、初始化阶段的预充电指令指令对所有bank充电,即此时的A[10]改为1;

测试条件:

à突发读写,每次的突发长度为256,其中数据的取值为1~640;

àSDRAM的行地址为13位,列地址为9位,4个bank,数据宽度为16位;

àSDRAM控制器时钟为100MHz,相位为0;SDRAM芯片时钟为100MHz,时钟相角为-90°,à但由于signaltapII的采样始终只有200MHz,所以采回来的时钟信号相位差没有体现出来,具体表现在下面的时序图中,时钟的下降沿为SDRAM控制器有效边沿(原对应100MHz,相位为0),上升沿为SDRAM芯片的时钟有效沿(100MHz,时钟相角为-90°),分析时序图时这点需要注意一下;

à每次突发传输结束后没有使用突发终止命令而使用了预充电指令;

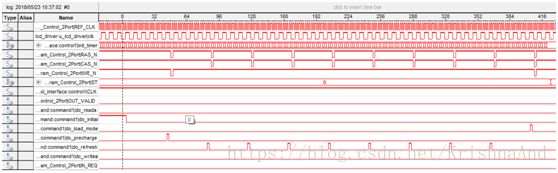

初始化阶段:

200us稳定期à1个预充电à8个刷新周期à模式寄存器设置

写数据阶段:

绿色画线部分为第一个写入的数据1,第二幅中绿色画线部分为写入的最后一个数据256;

紫色为预充电指令,关闭了正在操作的行;

将数据写入SDRAM时,必须提前一个时钟将数据从FIFO里面读出来,然后在写入命令触发的同时写入第一个数据到SDRAM,需要注意的是SDRAM控制器的时钟有效沿为下降沿,SDRAM芯片的输入时钟为上升沿,数据的写入和读出都是在SDRAM芯片的输入时钟的上升沿;(原本SDRAM控制器的时钟为上升沿有效,SDRAM芯片的输入时钟为-90度,可能由于采样时钟只有200MHz的缘故,所以显示的时钟有效沿为上述所示)

上图出现了一个问题,暂时没有想明白,sdram_data和q为wire连接关系,理论上sdram_data应该随q随时变化,但是我们可以看出他们之间慢了一个周期,暂时没找到原因,后续;

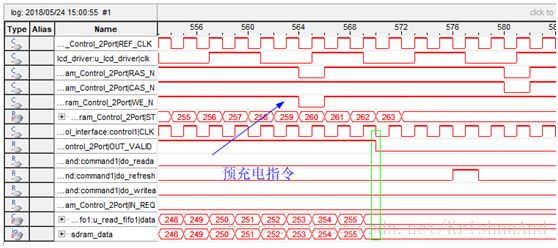

读数据阶段:

先看一个错误的例子:

由于写入FIFO的写数据请求信号晚一个周期,所以当ST=8时的下降沿才会写入第一个数据258,结果导致sdram读出的第一个数据257没有被写入FIFO,将写入FIFO中的数据写请求信号提前一个时钟周期后的时序图如下;

改正后的时序图分析:ST=7的上升沿SDRAM芯片输出第一个数据257,之后的下降沿将数据写入FIFO(read端)中,ST=7+256-1=262的上升沿SDRAM芯片输出最后一个数据256,之后的下降沿将数据写入FIFO(read端)中,符合预期要求;

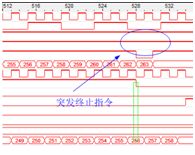

将突发传输中末尾的预充电指令换成突发终止指令:

写时序图:

读时序图:

突发终止指令均在256个数据传输完成后第一个时钟有效,符合sdram的突发传输时序要求,从sdram里面读出来的数据正常,则说明写入数据到SDRAM中的操作过程正常,但是vga显示出来的图像有少许随机横向窄条纹干扰,不知道是啥原因,下一步测试应该将从SDRAM读出的所有数据都通过串口打印出来进行分析,后续;