Cyclone IV 外接ddr2(一)

本文主要介绍cyclone iv与DDR2相连接时,各个物理管脚的连接方式及注意事项。

1、cyclone iv handbook上指明 该器件可以与 DDR2 SDRAM,DDR SDRAM,QDR II SRAM 这三类外部存储芯片相连接。cyclone iv不能连接DDR 3存储器。

2、下图是你在工程里调用DDR的IP核时,根据你外部接的DDR类型 选择对应的IP核,比如外部存储器件是DDR2 ,那你就选择“DDR2 SDRAM Controller with ALTMEMPHY”IP核, cyclone iv系列只能用ALTMEMPHY IP核控制器,UniPHY IP核在 cyclone iv里不能用,所以是灰色的(在cyclone v里就可以用UniPHY IP核)。

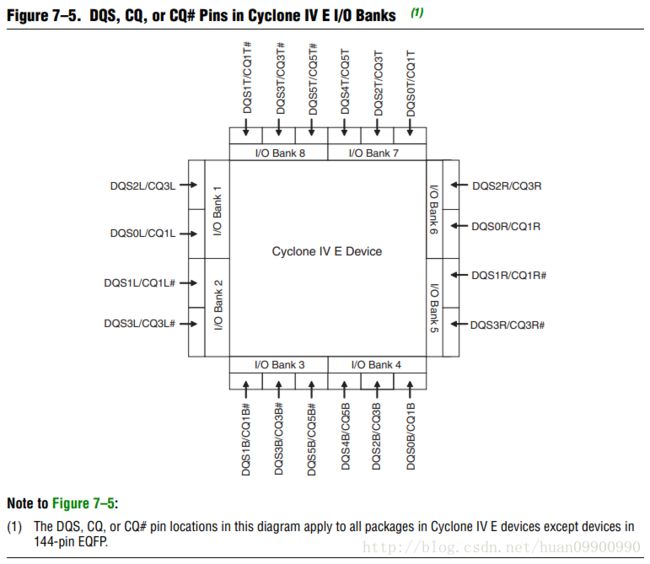

3、cyclone iv E芯片的chip planner中,每边包含的DQ 总线组数如下图所示。

下图列出了DQS的数量以及在芯片上的分布位置。

4、 DQ和DQS信号的方向是根据你外部所接的存储器类型决定的。

DDR2 SDRAM 和 DDR SDRAM:DQ,DQS是双向接口

QDR II SRAM :DQ,DQS是单向接口

5、对于cyclone iv,当外部存储器件是DDR2 SDRAM 和 DDR SDRAM时,DQS 数据选通信号只有在写DDR时才有效。在读数据时该信号是被忽略的,因为在DDR IP核内部会产生读数据的捕获时钟信号。

注意:必须把fpga的DQS管脚与外部存储器DDR2的DQS管脚相连;如果外部存储器是QDR II SRAM 那就把fpga的DQS管脚与QDR II SRAM 的CQ管脚相连。

6、cyclone iv 不支持差分探测信号(即DQS,DQS#差分对),只能用单个的DQS信号。在DDR2 SDRAM存储器里,探测信号用不用成差分还是单端的是可以配置的。比如在镁光的DDR2 MT47H6416HR-3E中,设置下面相应的寄存器位就行。

7、 cyclone iv 系列芯片的所有bank(除cyclone iv GX左边的bank以外)都支持x8,x9,x16,x32以及x36的DQ数据总线。 DDR2 SDRAM和DDR SDRAM的DQ总线接口 必须要用x8 mode 的数据总线,如果你的外部存储器接口数据总线比x8宽(比如要是外部存储器数据线DQ是16位宽的,那你就用同一个bank里的两个x8 组),则需要用多个x8组 去连接;x9,x16,x32 用于 QDR II SRAM存储器。

8、每一个DQ组,都有与其相对应的DQS管脚。两者是互相匹配的,如果一个DQ组没有与其相对应DQS匹配,那你在QUARTUS II里编译的时候,就会报错。下图列举了任一DQ和DQS的匹配关系。

9、 cyclone iv里,x9模式用的DQ,DQS管脚跟x8模式是一样的。x9模式比x8模式多了一个DQ管脚,当x9模式只用8个DQ管脚时(即跟x8模式用法一样时),多余的一个DQ管脚可以用作普通IO;x18模式用的DQ,DQS管脚跟x16模式是一样的。x18模式比x16模式多了两个DQ管脚,当x18模式只用16个DQ管脚时(即跟x16模式用法一样时),多余的两个DQ管脚可以用作普通IO;同理 ,x36模式用的DQ,DQS管脚跟x32模式是一样的。x36模式比x132模式多了四个DQ管脚,当x36模式只用32个DQ管脚时(即跟x32模式用法一样时),多余的四个DQ管脚可以用作普通IO。

当fpga里的这些DQ,DQS管脚没有接存储器管脚时,可以当做普通IO口使用。

10、对于cyclone iv与ddr相连的地址信号,控制,命令信号都是单沿发送的,你可以用fpga的任意bank的任意用户 IO口用于与外部存储器的地址,控制,命令管脚相连。

11、外部存储器的时钟信号连接,差分时钟信号CK,CK#必须被分配到fpga的差分管脚上,且必须与数据DQ管脚在同一个bank 或者是同一边。 对于DDR2 和DDR SDRAM,存储器的差分时钟信号(CK,CK#)用来捕获地址信号,控制和命令信号。同样,QDR II SRAM用写时钟(K,K#)去捕获地址,命令信号。

12、DDR2运行时钟频率范围

从下表可以看出,Cyclone iv C8L支持的最高memroy时钟频率是 167Mhz(Half-rate),150Mhz(Full-Rate)