VGA接口是一种最常见的显示屏接口,其时序与控制都比较简单。

1.VGA接口

VGA只需要三个接口:

R:红色深度值

G:绿色深度值

B:黄色深度值

HS:行同步

VS:场同步

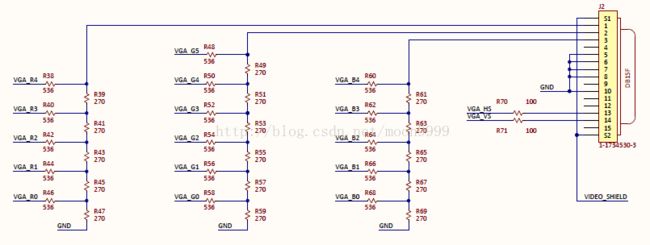

下图是zynq7000开发板上的VGA接口原理图。

2.VGA时序

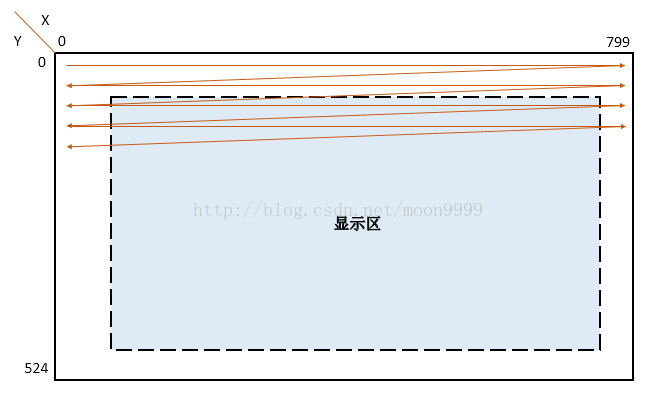

显示器的逐行扫描方式如下图所示,由屏幕左上方出发逐行向右下方扫描。扫描一行的频率为行频率,扫完一帧的频率为场频率。屏幕的自我刷新频率即场频率,常见为60Hz,行频为31.5KHz。

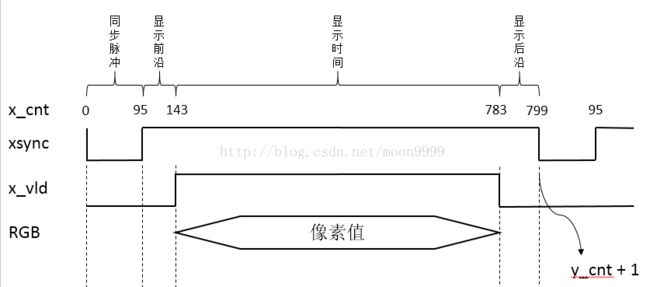

不过并非所有的扫描点都会发射电子到屏幕上,每一行扫描完是都要回到行首进行下一行的扫描,这期间不会有电子束打出到屏幕上,这就是行(场)消隐。通常来说,行扫描或场扫描的扫描计数均可分为四个阶段。其中显示阶段大小为真实屏幕分辨率大小。

在这四个阶段中,只有在显示阶段是的行输出x_vld有效,此时传出相应的像素值完场行同步,即可在该行相应位置显示相应颜色。每计满一行后,列计数器数值+1,显示方式与行同步一样。

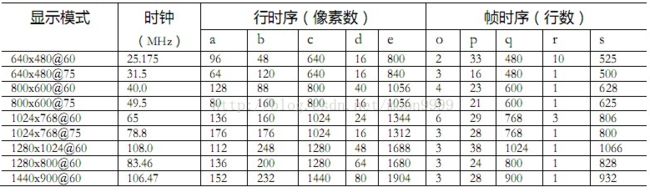

对于不同刷新速度的屏幕以及不同的分辨率,行同步与场同步的数值如下,其中C与Q为实际分辨率值。所需时钟频率计算方式以640*480@60Hz为例:

clk = 800 * 525 *60 = 25'200'000 = 25MHz

3.VGA接口模块

一个简单的在屏幕上显示一个色块的代码如下,输入时钟为25MHz。

module vga(

output [4:0] vga_r,

output [5:0] vga_g,

output [4:0] vga_b,

output reg vga_hs,

output reg vga_vs,

input clk,

input rst,

);

reg[9:0]xsync,ysync;

always @(posedge clk or posedge rst) begin

if (rst) begin

xsync <= 10'd0;

end

else if (xsync == 10'd799) begin

xsync <= 10'd0;

end

else begin

xsync <= xsync + 1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

ysync <= 10'd0;

end

else if (ysync == 10'd524) begin

ysync <= 10'd0;

end

else if (xsync == 10'd799) begin

ysync <= ysync + 1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

vga_hs <= 1'b0;

end

else if (xsync == 799) begin

vga_hs <=1'b0;

end

else if (xsync == 95) begin

vga_hs <= 1'b1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

vga_vs <= 1'b0;

end

else if (ysync == 0) begin

vga_vs <=1'b0;

end

else if (ysync == 1) begin

vga_vs <= 1'b1;

end

end

wire valid;

assign valid = (xsync > 143) && (xsync < 784) && (ysync > 34) && (ysync < 515);

assign x_pos = xsync - 143;

assign y_pos = ysync -34;

wire block_vld;

assign block_vld = (x_pos >= 50) && (x_pos < 100) && (y_pos >= 50) && (y_pos < 100);

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

RGB <= 16'b0;

end

else if (block_vld && valid) begin

RGB <= 16'b11111_000000_11111;

end

else if (valid) begin

RGB <= 16'b00000_000000_11111;

end

else begin

RGB <= 16'b0;

end

end

endmodule