iic协议以及个人总结的设计流程

目录

I2C 设计流程

简介

特性

功能描述

设计模块描述

常见的I2C操作顺序

Verilog HDL仿真与验证

结构图总结

I2C 设计流程

简介

I2C (Inter-IC)总线是一种简单、低带宽、短距离的协议。它通常出现在具有间歇访问的外围设备的系统中。这也是一个常见的通信解决方案,在一个封闭的系统,其中最小的痕迹是板上所希望的。许多半导体供应商在嵌入式系统中支持i2c兼容设备,包括EEPROM、温度传感器、电流传感器和时钟。2线接口允许串行传输8位字节的数据和7位地址与控制位。在I2C总线上发起传输的设备通常称为主设备,而被寻址的设备称为从设备。

本设计在FPGA或CPLD上实现了一个I2C从模块。它遵循I2C规范来提供设备寻址、读/写操作和确认机制。它为系统中的任何组件添加了一个即时的I2C兼容接口。FPGA和CPLD设备的可编程性为用户提供了将I2C从设备配置为任何合法从地址的灵活性。这避免了I2C总线上多个从设备上潜在的从地址冲突。

特性

I2C从模块是基于I2C规范的。用户应该对I2C规范和协议有基本的了解。

1、与I2C总线规范版本2.1兼容

2、软件可编程的从地址

3、支持随机读/写

4、支持顺序读/写

5、使用ACK /NACK与I2C主机进行通信

6、支持时钟拉伸作为握手

7、启动/停止/重复启动检测

8、支持7位寻址模式

功能描述

I2C从模块支持I2C规范中列出的主要特性。它响应I2C主机发出的命令。在正常情况下,I2C从机通过在ACK阶段下拉sda线来确认地址或数据的成功接收。当一个从机不能足够快地处理信息时,它使用两种方法中的一种来通知主机。从进程在ACK阶段不响应,这只发生在写操作中,从进程可以选择确认或不确认。这将导致主服务器发出停止命令并重试。从机也可以使用时钟拉伸技术,只要它需要,就可以向下拉scl线。主服务器将等待scl被释放,并继续完成之前的传输。

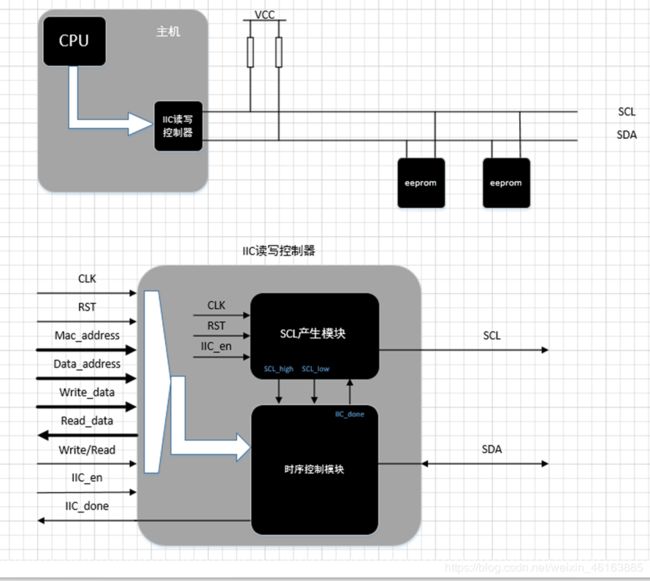

图1所示。I2C从程序框图

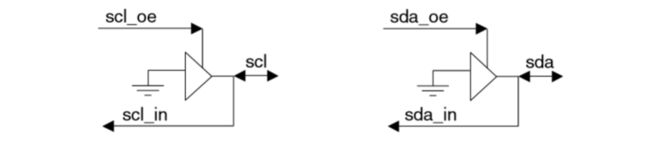

表1列出了I2C从模块的信号。将scl和sda信号分为数据信号和输出使能信号。用户可以手动绑定信号来创建一个bidi sda信号,如图2所示,并在测试台上进行了演示。

图2.用于I2C通道的scl和sda信号

表1.引脚排列

| 信号 |

方向 |

描述 |

| I2C接口 |

||

| Slc_in |

Input |

I2C时钟信号 |

| Scl_oe |

Output |

I2C时钟输出使能控制 |

| Sda_in |

Input |

I2C数据输入信号 |

| Sda_oe |

Output |

I2C数据输出使能控制 |

| 外围接口 |

||

| Xreset |

Input |

全局重置信号 |

| Ready |

Input |

准备好从从机侧发出信号 |

| Data_in[7:0] |

Input |

通过I2C总线传输的并行输入数据 |

| Data_out[7:0] |

Output |

从I2C总线接收的并行输出数据 |

| Start |

Output |

状态信号——表示I2C传输开始 |

| Stop |

Output |

状态信号——表示I2C传输停止 |

| Data_vld |

Output |

状态信号——表示数据准备好了 |

| R_w |

Output |

状态信号——表明主机是读或写入从机 |

设计模块描述

I2C从机设计(i2c_slave.v)由一个通过I2C操作机制的状态机组成。状态机的顶级表示如图3所示。启动和停止条件将被异步检测,以启动或终止I2C操作。当从地址与从设备的地址匹配时,以及当成功接收到一个字节的数据时,将生成ACK。状态机通过返回ACK状态来支持顺序/连续的读和写。未激活的“ready”信号表明从机需要时间来处理来自主机的数据。这个信号在ACK状态下拉下scl行,并将scl保持在那里,直到slave准备好再次处理数据。由于scl不可用,状态机将保持在ACK状态,并在scl发布后继续运行。这种“时钟拉伸”功能除了使用ACK或NACK位之外,还允许在从机和主机之间握手。“data_vld”信号表示成功接收或传输了一个字节的数据。

图3.顶层I2C从机状态图

接收数据的实际解释是在测试台上处理的。这提供了一个示例,说明如何解释从I2C通道接收的数据,同时允许用户灵活地添加自己的外围接口。

常见的I2C操作顺序

本设计支持常见的I2C操作。本节将描述每个操作的顺序。

发送从地址后的突发读或顺序读(方向不变):

1. 主机发出一个启动条件

2. 主机发送I2C从地址+ 1 H(1)位(读)

3.如果地址匹配,从机发出ACK到主机

4. 主机接收读数据,并为每个接收到的字节发出ACK

5. 主进程在最后一次读取字节后发出NACK,然后发出STOP条件,从而停止操作

突发写或顺序写(方向不变):

1. 主机发出一个启动条件

2. 主机发送I2C从地址+ 1 L(0)位(写)

3.如果地址匹配,从机发出ACK到主机

4. 主机发送要写入的地址

5. 从机发送ACK到主机

6. 主机将数据发送到指定的地址,而从机对每个字节的写数据发出ACK

7. 主机在接收到从机的ACK之后发出一个STOP条件来停止操作

随机读取(改变方向):

1. 主机发出一个启动条件

2. 主机发送I2C从地址+ 1 L(0)位(写)

3.如果地址匹配,从机发送ACK到主机

4. 主机发送要读取的地址

5. 从机发送ACK到主机

6主机发出重复启动条件

7. 主机发送I2C从地址+ 1 H(1)位(读)

8. 如果地址匹配,从机发送ACK给主机

9. 主机接收数据,并为每个接收到的字节发出ACK

10.主机在发出最后一个字节后发送一个NACK来停止操作,然后是一个STOP条件

随机写(方向不变):

1. 主机发出一个启动条件

2. 主机发送I2C从地址+ 1 L(0)位(写)

3.如果地址匹配,从机发送ACK到主机

4. 主机发送要写入的数据的地址

5. 从机ACK收到地址后

6. 主机发送一个字节的数据给从机,从机对写入的每个字节发出ACK

7. 主机接收到从机的ACK之后发出一个STOP条件来停止操作

Verilog HDL仿真与验证

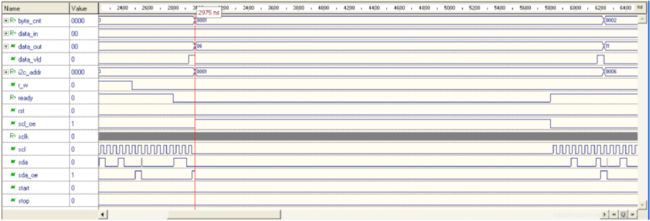

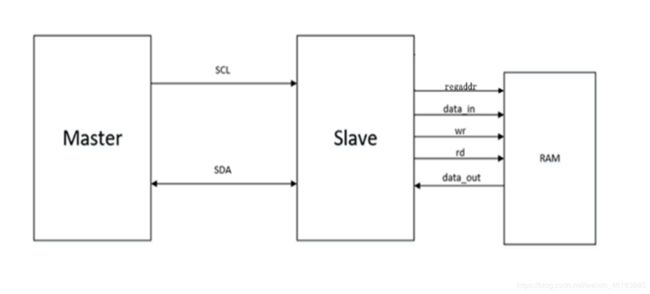

使用I2C主模块(i2c_ms .v)和顶层测试平台(i2c_peri_tf.v)模拟I2C从模块。图4显示了测试平台的结构。主模块生成从地址和读/写命令。从模块对应于命令,通过I2C通道接收数据或提供数据。顶层testbench提供一个模块来确定接收到的信息是否是后端内存地址或数据。然后,这些信息被用于从模拟的内存条(i2c.mem)进行读写。下图显示了该模块的仿真结果。

图4.I2C仿真结构

图5.顺序读,从地址=h52,数据读为hC0, h35, h11

图6.随机写入内存地址h0A,数据h55

图7.随机写入内存地址h0A,数据h55