在ASIC中异步复位信号的处理——滤毛刺和异步复位/同步撤离

前言

在毕业面试的时候遇到了这个问题,当时回答的不太好一直扎在心里,最近培训又讲了这块的知识因此在这里稍微记录总结一下。

异步复位

由于同步复位会被综合为触发器等元件的输入而增加功耗面积等,ASIC设计中异步复位使用越发广泛,当然这都不是重点,重点是在ASIC设计中应该对异步复位信号进行怎样的预处理以防止电路出现亚稳态等各种问题。简单来说,复位信号在使用前一般需要进行滤毛刺处理和异步复位/同步撤离处理。在这里我们假定输入的复位信号rst_n为低有效,即低电平复位有效,高电平复位撤销。

滤毛刺

滤复位信号的毛刺就是将低于设定阈值的复位信号认定为毛刺而加以忽略的过程。这里说两种方法,第一种是通过滤毛刺时钟+触发器完成,第二种通过延时器件完成。我们假定滤毛刺时钟clk_fit=100M,即T=10ns。

滤毛刺时钟+触发器

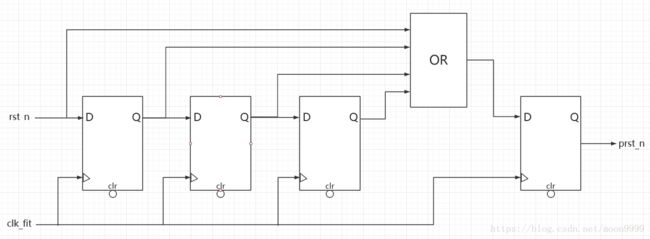

第一种方式的电路图如下所示,图中花了3个用于延时的D触发器,那么可以滤去30ns(3*10ns)一下的毛刺复位信号。

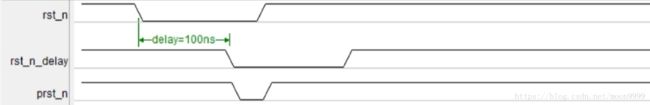

对应关系是如何得到的呢?假设我只有一个延时D触发器,那么复位信号必须维持L电平在一个clk_fit时钟周期以上OR(或门)才能在时钟沿出打出一个L信号出来,如下面的波形图所示,在红标出时钟会采到(rst_n | rst_n_ff1)==0,顺利触发prst_n为L电平。如果rst_n时间宽度小于一个clk_fit时钟周期,则根本无法触发prst_n为L电平。

同理,如果有两个延时D触发器,那么复位信号必须维持L电平在两个 clk_fit时钟周期以上,OR(或门)才能在时钟沿出打出一个L信号出来;如果有三个延时D触发器,那么复位信号必须维持L电平在三个 clk_fit时钟周期以上,OR(或门)才能在时钟沿出打出一个L信号出来,如下面两个波形如图。

因此,在OR前放置了N个延时D触发器,就可以滤除N*T时长一下的复位毛刺信号。

不过这样做有一个巨大的隐患,clk_fit时钟信号是不受时钟控制的,一旦clk_fit时钟信号失灵了或是出了什么问题,我们的复位信号将永远无法传出去,所以感觉实际工程共一般不会这么做吧?或者有其他的解决方法,暂时不得而知。

延时器件

如果不要依靠这个时钟的话,那么我们就引入一个延时元器件来滤毛刺,不过我没有实践过就说下大体方式吧。如果我要滤去100ns以下毛刺,那么就引入100ns延时器件,组成如下电路。

如此一来,我们就会得到如下的波形。通过波形可以看出,如果复位时长不够100ns,prst_n根-本不会被触发。不过这么做还有有一个隐患,就是如何保证延时器件在不同环境温度下的延时准确性,估计。。。还是有解决办法吧。

异步复位/同步撤离

这个词在各种说明异步复位的文章说了很多了,只不过作为新手一般不会关注到这一步。这两个词的含义我理解就是说,对于异步复位信号,复位模块/系统(1->0)时可以不与时钟对其,但是在复位撤销(0->1)时,必须是与时钟出发沿对其的。为什么要这么做呢?

1.位于复位这个行为而言,异步操作时完全可以的,因为所有的元器件都会最终回到初始值,那么有没有出现亚稳态、谁先谁后其实都没有关系,就像电视剧里说的”反正早晚都是si,早si晚si又有什么区别“,就是这个道理,对功能完全不会有影响。

2.但是对于撤销不行啊,一旦复位撤销了各个元器件就会开始工作了,如果复位撤销点到达各个元器件的时间有差别,或者正好打在了时钟的亚稳态窗(即在Tsetup+Thold内跳变了)上了,就会造成有的器件当前周期开始工作,而有的器件在下一周期开始工作,那整个系统就崩盘了这是绝对不允许的,因此复位的撤销一定要是同步的。

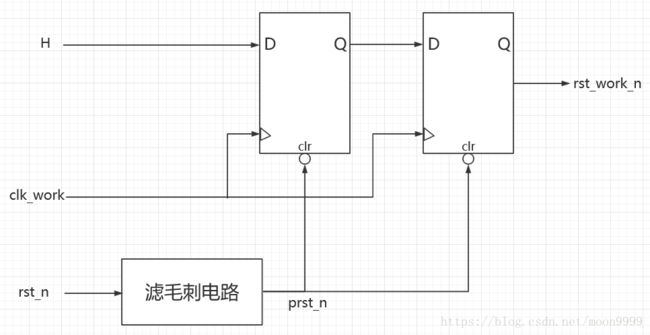

那么如何做到异步复位/同步撤离呢?采用如下这个电路即可。

rst_n经过滤波后得到prst_n,因此我们只需要分析prst_n的行为影响即可。

正常工作状态下,prst_n==1;

当prst_n起复位时(1->0),两个D触发器立刻被复位(clr),也就是说rst_work_n会立即下拉值L电平复位系统,这个下拉显然时候不受时钟控制的,因此实现了"异步复位";

当prst_n撤销复位时(0->1),两个D触发器的复位被撤销了,但是左上方的高电平H需要两个周期才会到达rst_work_n段,这两个周期一般足以消除亚稳态并且保证系统感知的复位时在时钟沿上的,于是这样实现了”同步撤销“。

不过当年我问了面试我的大佬一个问题:这样的话系统就延时了2个周期才复位的啊,会不会有问题?!

大佬回答:系统真的在乎这一两个周期的事么?早跑几周期晚跑几周期有啥关系,只要不跑错了就行。