【FPGA】clocking wizard配置(PLL/MMC内核配置)

明天准备更vivado的iserdes内核,ISE可能不怎么更了,由于毕设要开始搞了,准备直接转vivado,其实都差不多。今天先把ISE的始终管理内核说一下吧。

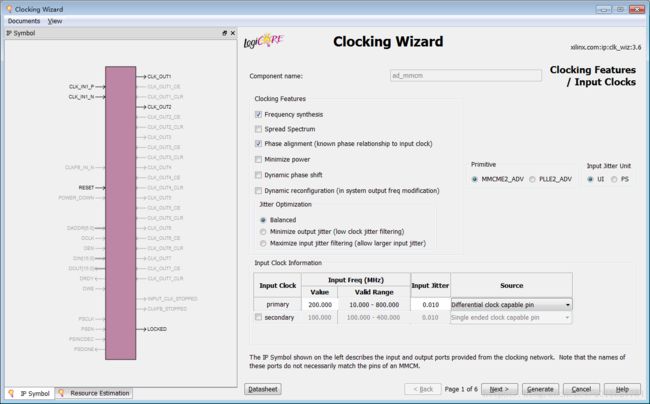

第一页,clocking features选项框中的

1.Frequency synthesis选项是允许输出与输入时钟不同频率的时钟。

2.Spread Spectrum选项是提供调制时钟输出,用来降低电子设备产生的电磁干扰的频谱密度。(没用过这个选项,不是很清楚这个东西)(直接序列展频技术 (Direct Sequence Spread Spectrum; DSSS)是将原来的讯号「1」或「0」,利用10个以上的chips来代表「1」或「0」位,使得原来较高功率、较窄的频率变成具有较宽频的低功率频率。而每个bit使用多少个chips称做Spreading chips,一个较高的Spreading chips可以增加抗噪声干扰,而一个较低Spreading Ration可以增加用户的使用人数。--摘自 百度百科)该选项应该是提高时钟质量降低噪声干扰的一个选项。

3.Phase alignment选项是相位锁定,也就是将输出始终的相位和一个参考时钟同步,大多是和输入时钟同步。(同步指的是相差一样而不是相位一样)

4.Minimize power选项为降低功耗,也就是资源,取而代之的是相位、频率的偏差,对于对时钟要求不高、资源有限的情况下可以使用,一般不推荐选此选项。

5.Dynamic Phase Shift该选项为提供动态相移功能,选上此选项之后,可以在输入端控制相移,并有相移完成之后的反馈,相移步进长度为固定的几个值。

6.Dynamic Reconfiguration该选项为打开动态配置端口,通过添加的输入输出引脚对MMC进行重新配置。(这个没用到过,也看的不是很明白,不是太懂,希望以后不要用到,哈哈哈哈)

右边的两个选项就是选择MMC还是PLL。这里加上DLL一起说一下区别:

1、DCM实际上就是一个DLL,可以对输入时钟进行相位移动,补偿,产生倍频和分频时钟,但是5以及以后的产品不用了,其倍频、分频能力较弱。

2、PLL相对于DCM,除了不能相移时钟,其它的都一样,但是PLL产生时钟的频率比DCM更加精准,而且时钟的jitter也更好。

3、MMCM实际上就是PLL+DCM相移功能的结合体。7系列的FPGA还会在临近I/O部分放置一些PLL,专门给MIG来产生DDR时钟。

可以根据自己的实际应用来选择。----------摘自某博客(https://blog.csdn.net/skyplain1984/article/details/53924111)

jitter option选项中:

1.balanced就是在抖动优化时选择比较均衡的正确带宽。(一般我都选这个,应该是对于下面两个选项的均衡)

2.minimize output jitter:使输出时钟抖动最小,但是可能会增加功耗或资源,可能导致输出相位错误。

3.maximize input jitter filtering:该选项表示可使输入时钟抖动变大,但是可能会导致输出时钟抖动变大。

以上三个选项只能选一个。

input clock information:

1.primary:就是主参考时钟输入,可在value中填写输入时钟频率单位为M,input jitter 一般根据实际时钟质量选择,如果为正常内部时钟,可选0.010。最后面source选项根据输入时钟的实际情况选择。

2.secondry:就是副参考时钟输入,其他同上。只有secondry时钟工作时,会导致输出始终质量变差(频率、相位、抖动)

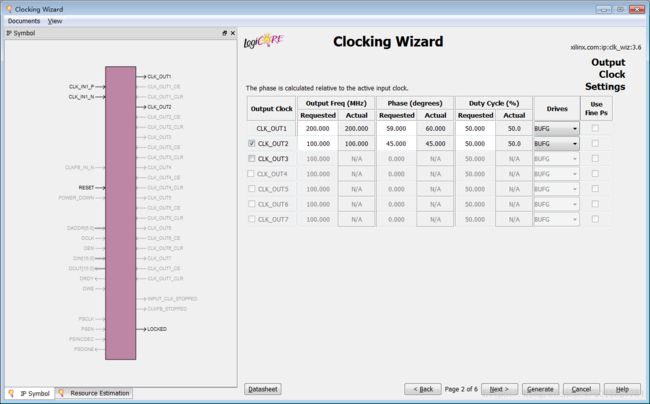

第二页

只有输出选项,request为输出信号需求频率,actual为实际输出信号频率,相位为相位偏差可正可负,对输出始终进行相移,dutycycle就是占空比。最后drives就是输出信号的时钟类型(根据实际情况选择,如果资源允许,也不知道选那个的话可选BUFG)。

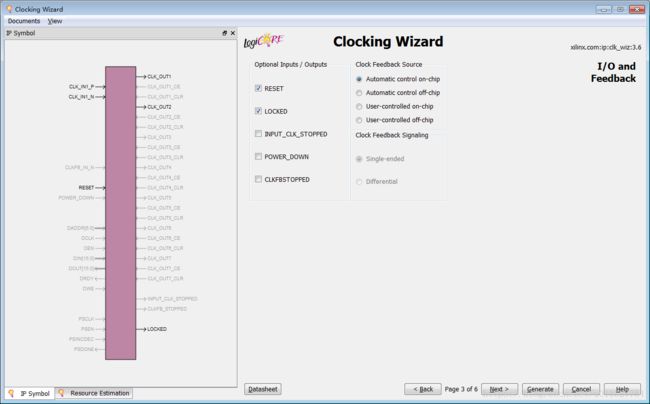

第三页

1.option inputs/outputs 为可选端口,可根据实际应用选择,一般情况下reset,locked选上,其他根据自身情况。

2.feedback source 选项如果之前有选相位校准之后,该选项框为相位校准是的反馈控制,一般情况下选择automatic control on-chip,在反馈信号为我们自己控制的时候可以选择user-controlled feedback。其中on-chip和off-chip为反馈路径是否在片内,一般情况下选automatic control on-chip就可以。(相位校准就用过反馈机制实现的输入输出时钟相位的校准)

3.feedback signals 该选项选择反馈信号的类型是单端还是差分,如果选择antomatic on-chip就会默认,其他选择想根据用户实际反馈信号的类型选择。

第四页

该页我没动过,因为这些参数都是内核自动根据用户前面选择最优配置的,选上allow override mode 之后就可以手一动配置(该选项一般不建议勾选,除非对MMC有较深理解同时又有特殊要求)

第五页

该页无关键参数修改,只有输入输出端口名字的重命名,可根据用户需求对端口名称重新命名。

--------------------------------昨天就该写完的,今天早上又补了一下才搞完,坚持啊!------------------------------------