原语,即primitive.

不同的厂商,原语不同;

同一家的FPGA,不同型号的芯片,可以也不一样;

原语类似最底层的描述方法.

使用原语的好处,

可以直接例化使用,不用定制IP;

即可通过复制原语的语句,然后例化IP,就可使用;

题外话, Altera和Xilinx在例化IP使用时,所用方法不同.

Altera是通过原语例化后,在通过defparam来重新定义参数,再使用;

Xilinx是通过直接修改原语中的参数再例化IP来使用;

最近用到xilinx的芯片,

看到它原语的介绍,摘录如下.以后用在Altera的再补充.

X公司的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,

处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB组件,G-tranceiver.

以最常用的时钟组件举例.

其中,以上的DCM_,在某些器件里都可以换成PLL_.

BUFG

具有高扇出的全局时钟缓冲器.通过它可接入到全局时钟网络中.

也常接复位,时钟使能信号等.

Eg. BUFG bufg_inst( .O(clk_o), .I( clk_i));

BUFMUX

全局时钟利用器,选择两个输入时钟I0或I1中的一个作为输出;S为选择信号,

S=0时,输出I0, S=1时,输出I1;

Eg. BUFGMUX bufgmux_inst(.O(clk_o),

.I0(clk1_i),

.I1(clk2_i),

.S(s)

);

BUFIO

本地IO时钟缓冲器.使用独立于全局时钟网络的专用时钟网络来驱动纵向IO管脚.

非常适合同步数据采集;BUFIO要求时钟和相应的IO必须在同一时钟区域,而不同的时钟网络的驱动需要BUFR原语来实现.由于BUFIO引出的时钟只到达了IO列,所以不能来驱动逻辑资源,比如CLB和BRAM.

Eg. BUFIO bufio_inst( .O(clk_o), .I(clk_i0));

BUFR

本地IO时钟逻辑缓冲器.与BUFIO一样是将驱动时钟引入某一时钟区域的专用时钟网络,而独立于全局时钟网络;不同的是,BUFR不仅可以跨越不同的时钟区域(最多3个),还能够驱动IO逻辑以及自身或邻近时钟区域的逻辑资源.BUFIO的输出和本地内部互联都能驱动BUFR组件.此外,BUFR能完成输入时钟1—8的整数分频.因些BUFR是同步设计中实现跨时钟域以及串并转换的最佳方案.

Eg. BUFR #(

.BUFR_DIVEDE(“BYPASS”),//分频比,可选择BYPASS,1—8

.SIM_DEVICE(“VIRTEX4”)

)BUFR_inst(

.O(clk_o),

.CE(CE),

.CLR(clr),

.I(clk_i)

);

DCM_BASE

基本数字时钟管理模块的缩写,是相伴和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理.如需要频率和相位动态生配置,则可以选用DCM_ADV原语,如果需要相位动态偏移,可使用DCM_PS原语.

Eg. DCM_BASE#(….)

DCM_BASE #(

.CLKDV_DIVIDE(2.0),

// CLKDV 分频比可以设置为: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

// 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0

.CLKFX_DIVIDE(1), // Can be any integer from 1 to 32

// CLKFX 信号的分频比,可为1 到32 之间的任意整数

.CLKFX_MULTIPLY(4),

// CLKFX 信号的倍频比,可为2 到32 之间的任意整数

.CLKIN_DIVIDE_BY_2("FALSE"),

// 输入信号2 分频的使能信号,可设置为TRUE/FALSE

.CLKIN_PERIOD(10.0),

// 指定输入时钟的周期,单位为ns,数值范围为1.25~1000.00。

.CLKOUT_PHASE_SHIFT("NONE"),

// 指定移相模式,可设置为NONE 或FIXED

.CLK_FEEDBACK("1X"),

// 指定反馈时钟的频率,可设置为NONE、1X 或2X。相应的频率关系都是

针对CLK0 而言的。

.DCM_PERFORMANCE_MODE("MAX_SPEED"),

// DCM 模块性能模式,可设置为MAX_SPEED 或MAX_RANGE

.DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"),

// 抖动调整,可设置为源同步、系统同步或0~15 之间的任意整数

.DFS_FREQUENCY_MODE("LOW"),

// 数字频率合成模式,可设置为LOW 或HIGH 两种频率模式

.DLL_FREQUENCY_MODE("LOW"),

// DLL 的频率模式,可设置为LOW、HIGH 或HIGH_SER

.DUTY_CYCLE_CORRECTION("TRUE"),

// 设置是否采用双周期校正,可设为TRUE 或FALSE

.FACTORY_JF(16'hf0f0),

// 16 比特的JF 因子参数

.PHASE_SHIFT(0),

// 固定相移的数值,可设置为-255 ~ 1023 之间的任意整数

.STARTUP_WAIT("FALSE")

// 等DCM 锁相后再延迟配置DONE 管脚,可设置为TRUE/FALSE

) DCM_BASE_inst (

.CLK0(CLK0), // 0 度移相的DCM 时钟输出

.CLK180(CLK180), // 180 度移相的DCM 时钟输出

.CLK270(CLK270), // 270 度移相的DCM 时钟输出

.CLK2X(CLK2X), // DCM 模块的2 倍频输出

.CLK2X180(CLK2X180), // 经过180 度相移的DCM 模块2 倍频输出

.CLK90(CLK90), // 90 度移相的DCM 时钟输出

.CLKDV(CLKDV), // DCM 模块的分频输出,分频比为CLKDV_DIVIDE

.CLKFX(CLKFX), // DCM 合成时钟输出,分频比为(M/D)

.CLKFX180(CLKFX180), // 180 度移相的DCM 合成时钟输出

.LOCKED(LOCKED), // DCM 锁相状态输出信号

.CLKFB(CLKFB), // DCM 模块的反馈时钟信号

.CLKIN(CLKIN), // DCM 模块的时钟输入信号

.RST(RST) // DCM 模块的异步复位信号

);

PLL_BASE

Xilinx的低端的FPGA中都用DCM,高级一点的都用PLL.

这个再多说一句,使用PLL时,输出时钟

Clk_out = Clkin*Mult / DIVCLK_DIVIDE /CLKOUTx_DIVIDE;

Eg.

PLL_BASE #(

.BANDWIDTH("OPTIMIZED"), // "HIGH", "LOW" or "OPTIMIZED"

.CLKFBOUT_MULT(2), // Multiplication factor for all output clocks

.CLKFBOUT_PHASE(0.0), // Phase shift (degrees) of all output clocks

.CLKIN_PERIOD(0.000), // Clock period (ns) of input clock on CLKIN

.CLKOUT0_DIVIDE(5), // Division factor for CLKOUT0 (1 to 128)

.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0 (0.01 to 0.99)

.CLKOUT0_PHASE(0.0), // Phase shift (degrees) for CLKOUT0 (0.0 to 360.0)

.CLKOUT1_DIVIDE(1), // Division factor for CLKOUT1 (1 to 128)

.CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT1 (0.01 to 0.99)

.CLKOUT1_PHASE(0.0), // Phase shift (degrees) for CLKOUT1 (0.0 to 360.0)

.CLKOUT2_DIVIDE(1), // Division factor for CLKOUT2 (1 to 128)

.CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT2 (0.01 to 0.99)

.CLKOUT2_PHASE(90), // Phase shift (degrees) for CLKOUT2 (0.0 to 360.0)

.CLKOUT3_DIVIDE(2), // Division factor for CLKOUT3 (1 to 128)

.CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT3 (0.01 to 0.99)

.CLKOUT3_PHASE(0.0), // Phase shift (degrees) for CLKOUT3 (0.0 to 360.0)

.CLKOUT4_DIVIDE(1), // Division factor for CLKOUT4 (1 to 128)

.CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT4 (0.01 to 0.99)

.CLKOUT4_PHASE(0.0), // Phase shift (degrees) for CLKOUT4 (0.0 to 360.0)

.CLKOUT5_DIVIDE(1), // Division factor for CLKOUT5 (1 to 128)

.CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT5 (0.01 to 0.99)

.CLKOUT5_PHASE(0.0), // Phase shift (degrees) for CLKOUT5 (0.0 to 360.0)

.COMPENSATION("SYSTEM_SYNCHRONOUS"), // "SYSTEM_SYNCHRONOUS",

// "SOURCE_SYNCHRONOUS", "INTERNAL", "EXTERNAL",

// "DCM2PLL", "PLL2DCM"

.DIVCLK_DIVIDE(1), // Division factor for all clocks (1 to 52)

.REF_JITTER(0.100) // Input reference jitter (0.000 to 0.999 UI%)

) pll2 (

.CLKFBOUT(CLKFBIN), // General output feedback signal

.CLKOUT0(clk_100M), // 80M 0d

.CLKOUT1(), // 10M 0d

.CLKOUT2(), //80M 90d

.CLKOUT3(), // One of six general clock output signals

.CLKOUT4(), // One of six general clock output signals

.CLKOUT5(), // One of six general clock output signals

.LOCKED(), // Active high PLL lock signal

.CLKFBIN(CLKFBIN), // Clock feedback input

.CLKIN(clk), // Clock input

.RST(~rst_n) // Asynchronous PLL reset

);

再举IO组件为例,

I/O 组件提供了本地时钟缓存、标准单端I/O 缓存、差分I/O 信号缓存、DDR

专用I/O 信号缓存、可变抽头延迟链、上拉、下拉以及单端信号和差分信号

之间的相互转换,具体包括了21 个原语.

BUFIO

上文讲过

IBUFDS

用于将差分输入信号转为标准单端信号,且可加入可选延迟.

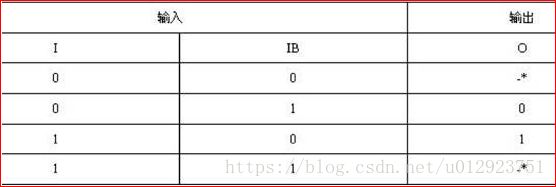

输入信号为I,IB,一个为主,一个为从,二者相伴相反.真值表如下:

其中-*, 表示维持原输出值.

Eg. IBUFDS refclk_ibuf (.O(sys_clk_c), .I(sys_clk_p), .IB(sys_clk_n)); //差分时钟进来

IDELAY

用户IO管脚的输入通路都有一个IDELAY模块,可用于数据信号或时钟信号,使二者同步,实现准确采集输入数据.IDELAY具有可控的64抽头延迟线,每个抽头的延迟都是经过精密校准的78ps(这个不同的芯片应该不同),且与进程,电压和温度特性无关.可弥补PCB的布线长度不一致带来的延时不同的问题.

信号说明:

I:单比特输入信号,来自于IOB 的串行输入数据;

C:单比特输入信号,时钟输入信号;

INC:单比特输入信号,用于增加或减少延迟抽头数;

CE:单比特输入信号,使能延迟抽头数增加或减少的功能;

RST:单比特输入信号,复位延迟链的延迟抽头数,如果没有编程输入则为0;

O:单比特输出信号。

Eg. IDELAY#(

.IOBDELAY_TYPE(“DEFAULT”),

.IOBDELAY_VALUE(0) //输入延迟周期,可设置0—63

) IDELAY_inst(

.O(data_o),

.C(c),

.CE(ce),

.I(data_i),

.INC(inc),

.RST(rst)

);

OBUFDS

将标准单端信号转换成差分信号,输出端口需要直接对应到顶层模块的输出信号.与IBUFDS为一对互逆操作.

Eg. OBUFDS #(

.IOSTANDARD("DEFAULT")

// 指名输出端口的电平标准

) OBUFDS_inst (

.O(O), // 差分正端输出,直接连接到顶层模块端口

.OB(OB), // 差分负端输出,直接连接到顶层模块端口

.I(I) // 缓冲器输入

);

IOBUF

单端双向缓冲器,其IO接口必须和指定的电平标准相对应,支持LVTTL,LVCOMS12, LVCMOS18, LVCMOS25以及33等信号标准.同时还可通过DRIVE, FAST以及SLOW等约束来满足不同驱动和抖动速率的需求.默认的驱动能力是12mA,低抖动. IOBUF由IBUF和OBUFT两个基本组件构成,当IO端口为高阻时,其输出口O为不定态.

Eg. // Xilinx HDL 库向导版本,ISE 9.1

IOBUF #(

.DRIVE(12),

// 指定输出驱动的强度

.IOSTANDARD("DEFAULT"),

// 指定I/O 电平的标准,不同的芯片支持的接口电平可能会有所不同

.SLEW("SLOW")

// 制定输出抖动速率

) IOBUF_inst (

.O(O), // 缓冲器的单元输出

.IO(IO), // 缓冲器的双向输出

.I(I), // 缓冲器的输人

.T(T) // 3 态使能输入信号

);

PULLDOWN / PULLUP

IO口内部上位或下位.上位是为了解决总线驱动能力不足时提供电流的,下拉电阻是用来吸引电流的.

Eg. PULLDOWN pulldown_inst( .O(data_o) );

PULLUP pullup_inst( .O(data_o) );