沧小海深入剖析xilinx的GTP/GTX核,掌握高速串行收发机制——第七章 GTP的IP核配置

总目录在这哦~

https://blog.csdn.net/z123canghai/article/details/107700878

第七章 GTP的IP核配置

目录

7.1 选项卡1——GT Selection

7.2 选项卡2——Line Rate, Transceiver Selection, and Clocking

7.3 Encoding and Optional Ports (编码和可选端口)

7.4 Alignment, Termination, and Equalization(对齐,终止和均衡)

7.5 选项卡_5 PCIE等

这部分基本上是《PG168 November 30, 2016》的上翻译解释的,由于涉及内容很多,要了解具体意义还得看前6章节。

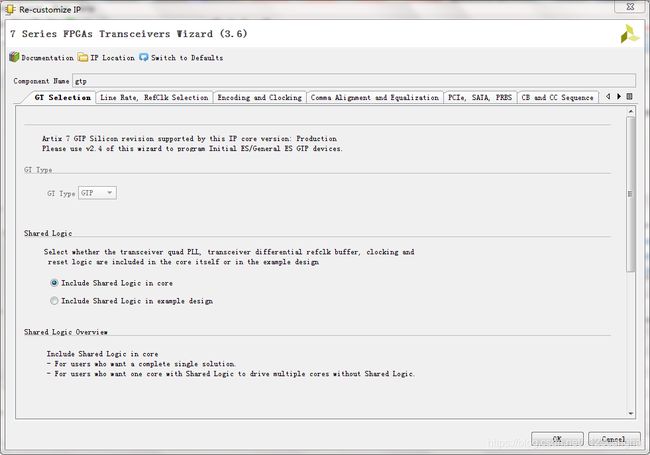

7.1 选项卡1——GT Selection

向导的第1页(图2-1)允许选择组件名称并确定线路速率和参考时钟频率。此外,此页面指定在核心或示例设计中包含共享逻辑的选项。

图7-1 选项卡1

- 在“组件名称”字段中,输入向导实例的名称。此示例使用名称gtp。

- 在GT_Type字段中,选择GTX,GTH或GTP。收发器的类型取决于“项目选项”中选择的设备,A7系列只支持GTP。

- 包括共享逻辑选项可帮助向导用户在核心级别或示例设计中选择共享逻辑资源。

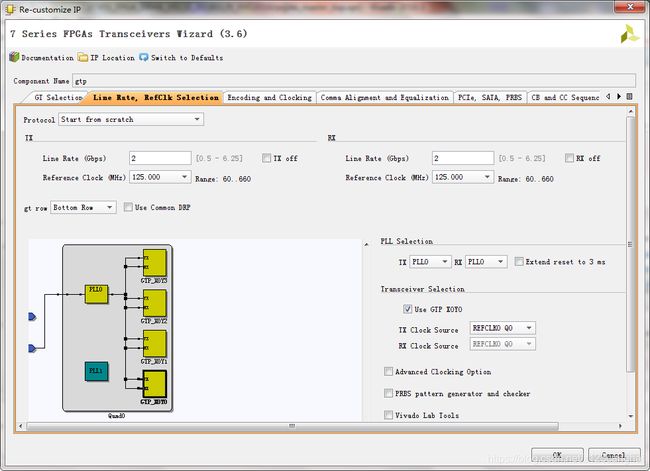

7.2 选项卡2——Line Rate, Transceiver Selection, and Clocking

向导的第2页(图2-2)允许您选择收发器位置、时钟及数量。

图7-2 选项卡1

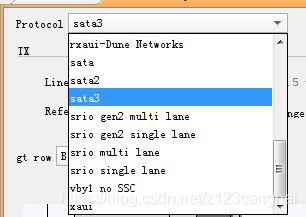

Protocol是选择协议,下拉菜单里面有各种各样的协议,在这里选择不同的协议只是为确定线速率及参考时钟提供便利,因为不同协议的速率是固定的,比如sata3是6Gbps,并不会产生其他的影响,从这也可以看出,依靠该核可以实现很多种协议。我们一般选择“start from scratch”,翻译为“白手起家”,我们可以理解为不构建任何协议,从最原始本初开始。

使用表4-7和表4-8确定线路速率和参考时钟设置。

| 选项 |

描述 |

| Line Rate |

设置为Gb/s的所需目标线路速率。可以独立于接收线路速率。 |

| Reference Clock |

从列表中选择应用程序提供的最佳参考时钟频率。 |

| Txoff |

选择此选项可禁用收发器的TX路径。收发器仅用作接收器。 |

表4-8:RX设置

| 选项 |

描述 |

| Line Rate |

设置为Gb/s的所需目标线路速率。可以独立于接收线路速率。 |

| Reference Clock |

从列表中选择应用程序提供的最佳参考时钟频率。 |

| Rxoff |

选择此选项可禁用收发器的RX路径。 |

使用表4-9到4-12确定此页面上提供的可选端口设置。

| 选项 |

描述 |

| Use Common DRP |

选择此选项可使应用程序可以使用COMMON块的动态重配置端口信号 |

| Advanced Clocking Option |

使用此复选框可将所有可能的参考时钟端口显示给生成的包装器。用于动态时钟切换。 |

| PRBS pattern generator and check |

PRBS模式产生和检测功能经常用来验证链路质量金额抖动容忍测试。 |

| Vivado Design Suite Debug Feature |

使用此复选框可以显示IP中的ILA和VIO内核,以进行硬件调试和控制。有关使用硬件中的ILA和VIO内核进行调试的更多详细信息,请参阅KC705评估板上的7系列GT向导硬件验证,第127页。 |

表4-10:选择收发器和参考时钟

| 选项 |

描述 |

| GT |

按位置选择要在目标设计中使用的各个收发器。 |

| TX时钟源 |

确定提供给每个所选收发器的参考时钟信号的来源(参见表4-12)。每四个收发器提供两个差分时钟信号输入引脚,标记为REFCLK0和REFCLK1。这些组从收发器列的底部开始标记为Q0到Q4。每个收发器可以根据收发器位置访问本地信号组和一个或两个相邻组。 |

| RX时钟源 |

表4-11:PLL选择、

| 选项 |

描述 |

| QPLL |

GTX和GTH收发器:当Quad的所有四个收发器用于节省功率时,使用Quad PLL。四路PLL在四路收发器之间共享。 |

| CPLL |

GTX和GTH收发器: 根据所选收发器支持的线路速率使用通道PLL。 GTP收发器无该组件 |

| PLL0 |

仅限GTP收发器:PLL0在四个四通道收发器之间共享 |

| PLL1 |

仅限GTP收发器:PLL1在四个四通道收发器之间共享。 |

| REFCLK0/1Q0 |

收发器Y0-Y3的本地参考时钟 |

| REFCLK0/1Q1 |

收发器Y4-Y7的本地参考时钟 |

| REFCLK0/1Q2 |

收发器Y8-Y11的本地参考时钟 |

| REFCLK0/1Q3 |

收发器Y12-Y15的本地参考时钟 |

| REFCLK0/1Q4 |

收发器Y16-Y19的本地参考时钟 |

| REFCLK0/1Q5 |

收发器Y20-Y23的本地参考时钟 |

| REFCLK0/1Q6 |

收发器Y24-Y27的本地参考时钟 |

| REFCLK0/1Q7 |

收发器Y28-Y31的本地参考时钟 |

| REFCLK0/1Q8 |

收发器Y32-Y35的本地参考时钟 |

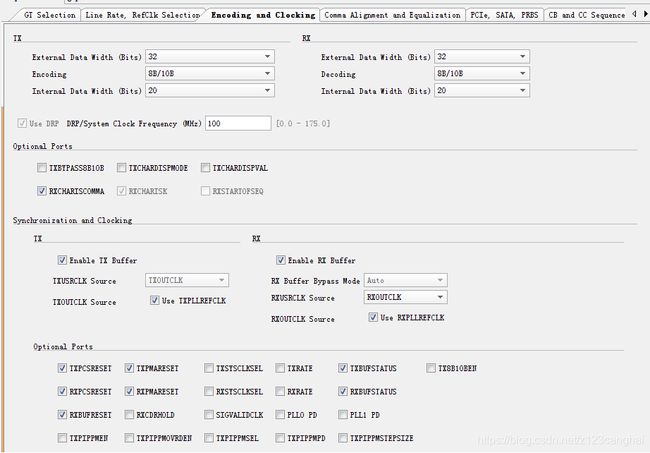

7.3 Encoding and Optional Ports (编码和可选端口)

向导的第3页(图4-12)允许您选择编码和8B/10B可选端口。表4-13至4-20列出了可用选项。

表4-13:发送设置

| 选项 |

描述 |

|

| 对外数据宽度 |

16 |

将发送器应用程序接口数据宽度设置为两个8比特字节。 |

| 20 |

发送器应用程序接口数据路径宽度设置为20位。 |

|

| 32 |

将发送器应用程序接口数据宽度设置为四个8位字节 |

|

| 40 |

发送器应用程序接口数据路径宽度设置为40位。 |

|

| 64 |

将发送器应用程序接口数据路径宽度设置为8个8位字节(64位)。 |

|

| 80 |

将发送器应用程序接口数据宽度设置为80位。 |

|

| 编码

|

8B/10B |

在传输之前,数据流被传递到内部8B / 10B编码器。 |

| 64B/66B_with_Ext_Seq_Ctr |

数据流通过64B / 66B变速箱和扰码器。 变速箱的顺序计数器在示例设计中实现。 |

|

| 64B/66B_with_Int_Seq_Ctr |

数据流通过64B / 66B变速箱和扰码器。 变速箱的顺序计数器在示例设计中实现。 |

|

| 64B/67B_with_Ext_Seq_Ctr |

数据流通过64B / 67B变速箱和扰码器。 变速箱的顺序计数器在示例设计中实现。 |

|

| 64B/67B_with_Int_Seq_Ctr |

仅限GTX收发器:数据流通过64B / 67B变速箱和扰码器。 变速箱的顺序计数器在收发器内实现。 |

|

| 内部数据宽度 |

16 |

选择内部数据宽度为16。 |

| 20 |

选择内部数据宽度为20。 |

|

| 32 |

选择内部数据宽度为32。 |

|

| 40 |

选择内部数据宽度为40。 |

|

| 选项 |

描述 |

|

| 对外数据宽度 |

16 |

将发送器应用程序接口数据宽度设置为两个8比特字节。 |

| 20 |

发送器应用程序接口数据路径宽度设置为20位。 |

|

| 32 |

将发送器应用程序接口数据宽度设置为四个8位字节 |

|

| 40 |

发送器应用程序接口数据路径宽度设置为40位。 |

|

| 64 |

将发送器应用程序接口数据路径宽度设置为8个8位字节(64位)。 |

|

| 80 |

将发送器应用程序接口数据宽度设置为80位。 |

|

| 编码

|

8B/10B |

数据流被传递到内部8B / 10B解码器。 |

| 64B/66B |

数据流通过64B / 66B变速箱和解扰器。 |

|

| 64B/66B |

数据流通过64B / 67B变速箱和解扰器。 |

|

| 内部数据宽度 |

16 |

选择内部数据宽度为16。 |

| 20 |

选择内部数据宽度为20。 |

|

| 32 |

选择内部数据宽度为32。 |

|

| 40 |

选择内部数据宽度为40。 |

|

注意: RX设置应与TX设置相同。

Table 4-15: DRP

| 选项 |

描述 |

| Use DRP |

选择此选项可使应用程序可以使用CHANNEL块的动态重配置端口信号 |

X PCS / PMA相位对齐设置控制TX缓冲区是启用还是旁路。有关此设置的详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 RX PCS / PMA对齐设置控制是否启用RX相位对齐电路。

Table 4-16 shows the optional ports for 8B/10B

| 选项 |

描述 |

|

| TX |

TXBYPASS8B10B |

此高电平有效端口允许字节交错数据以每字节为基础旁路8B / 10B。 TX8B10BEN必须为高才能使用此每字节旁路模式。 TX8B10BBYPASS [3]对应TXDATA [31:24] TX8B10BBYPASS [2]对应TXDATA [23:16] TX8B10BBYPASS [1]对应TXDATA [15:8] TX8B10BBYPASS [0]对应TXDATA [7:0] TX8B10BBYPASS [ x] = 1,绕过字节x的编码器。 TX8B10BBYPASS [x] = 0,使用字节x的编码器。 |

| TXCHARDISPMODE |

设置为“高”以使用TXCHARDISPVAL在编码TXDATA时强制运行差异为负或正。设置为低以使用正常运行差异。有关详细定义,请参阅表3-6。若不启用编码则可补位作为数据 TXCHARDISPMODE [3]对应TXDATA [31:24] TXCHARDISPMODE [2]对应TXDATA [23:16] TXCHARDISPMODE [1]对应TXDATA [15:8] TXCHARDISPMODE [0]对应TXDATA [7:0] |

|

| TXCHARDISPVAL |

使用TXCHARDISPMODE提供运行差异控制。若不启用编码则可补位作为数据 有关详细信息,请参阅表3-6。 TXCHARDISPVAL [3]对应TXDATA [31:24] TXCHARDISPVAL [2]对应TXDATA [23:16] TXCHARDISPVAL [1]对应TXDATA [15:8] TXCHARDISPVAL [0]对应TXDATA [7:0] |

|

| RX |

RXCHARISCOMMA |

高电平有效表示RXDATA上显示的相应字节是K码。 RXCHARISCOMMA [3]对应RXDATA [31:24] RXCHARISCOMMA [2]对应RXDATA [23:16] RXCHARISCOMMA [1]对应RXDATA [15:8] RXCHARISCOMMA [0]对应RXDATA [7:0] |

| RXCHARISK |

高电平有效表示当启用8B / 10B解码时,RXDATA上显示的相应字节为K字符。 RXCHARISK [3]对应RXDATA [31:24] RXCHARISK [2]对应RXDATA [23:16] RXCHARISK [1]对应RXDATA [15:8] RXCHARISK [0]对应RXDATA [7:0] 这是 如果绕过8B / 10B解码器或者RXNOTINTABLE的相应位为高,则非编码数据的第8位。 |

|

表4-17:TX和RX缓冲器旁路选项

| 选项 |

描述 |

|

| TX |

Enable TX Buffer |

如果选中Enable TX Buffer复选框,则启用收发器中的TX缓冲区。可以绕过该缓冲区以获得低确定性延迟。 在发送端的PCS子层里面有两个并行时钟域,分别是PMA相连的并行时钟(XCLK)和TXUSRCLK时钟。为了保证数据传输速率一致,XCLK必须和TXUSERCLK时钟的速率匹配,并且要解决2个时钟域之间的相位差异。利用TX BUFFER介于XCLK和TXUSERCLK俩时钟域之间,用于匹配两者的速率和相位偏差。 |

| TX |

TX Buffer Bypass Mode |

仅当旁路TX缓冲区时才使用此选项。必须使用手动模式。如果不使能缓冲,可以采用相位对齐的方式,有关详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 |

| RX |

Enable RX Buffer |

如果选中Enable RX Buffer复选框,则启用收发器中的RX弹性缓冲区。可以绕过该缓冲区以获得低确定性延迟 |

| RX |

RX Buffer Bypass Mode |

仅当绕过RX缓冲区时,此选项才可见。建议使用自动模式。要使用手动模式,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 |

表4-18:TXUSRCLK和RXUSRCLK源

| 选项 |

描述 |

|

| TX |

TXOUTCLK |

TXUSRCLK由TXOUTCLK驱动 |

| RX |

TXOUTCLK |

RXUSRCLK由TXOUTCLK驱动。如果绕过RX缓冲区,则此选项不可用。 对于RX缓冲旁路模式,RXOUTCLK用于源RXUSRCLK。 |

表4-19:TXOUTCLK和RXOUTCLK源

| 选项 |

描述 |

|

| TX |

Use TXPLLREFCLK |

如果选中复选框Use TXPLLREFCLK,则从输入参考时钟生成TXOUTCLK(1);否则,向导会为TXOUTCLK选择合适的源。 |

| RX |

Use RXPLLREFCLK |

如果选中复选框Use RXPLLREFCLK,则从输入参考时钟生成RXOUTCLK(1); 否则,向导会为RXOUTCLK选择合适的源。 |

注意:1.有关TXOUTCLK和RXOUTCLK控制的更多信息,请参见7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。

Table 4-20: 可选端口

| 选项 |

描述 |

|

| TXPCSRESET |

发送器PCS逻辑的高电平有效复位信号。 |

|

| TXBUFSTATUS |

TX缓冲状态(output)。 TXBUFSTATUS [1]:TX缓冲区溢出或下溢状态。当TXBUFSTATUS [1]设置为高电平时,它将保持高电平,直到TX缓冲区复位。 1:TX FIFO发生上溢或下溢。 0:无TX FIFO溢出或下溢错误。 TXBUFSTATUS [0]:TX缓冲区充满度。 1:TX FIFO至少半满。 0:TX FIFO小于半满。 |

|

| TXRATE |

传输速率变化端口。该端口动态控制TX串行时钟分频器D的设置(见表3-23),并与TXOUT_DIV属性一起使用。 要在固定线路速率应用中使用D分频器,必须将TXOUT_DIV属性设置为适当的值,并且TXRATE端口需要连接到3'b000。 要在多个线速应用中使用D分频器,TXRATE端口用于动态选择D分频器值。TXOUT_DIV属性和TXRATE端口必须在器件配置时选择相同的D分频器值。器件配置后,TXRATE用于动态更改D分频器值。 有关详细信息,请参阅表3-23中的“通过端口动态控制”一栏。 有关详细信息,请参阅表3-23中的“通过属性进行静态设置”列。 3'b000:使用TXOUT_DIV分频器值 3'b001:将D分频器设置为1 3'b010:将D分频器设置为2 3'b011:将D分频器设置为4 3'b100:将D分频器设置为8 |

|

| RXPCSRESET |

接收器PCS逻辑的高电平有效复位信号。 |

|

| RXBUFSTATUS |

指示RX弹性缓冲区的状态: 000:在标称操作范围内,缓冲区占用率在CLK_COR_MIN_LAT和CLK_COR_MAX_LAT范围内 001:RX弹性缓冲区占用率小于CLK_COR_MIN_LAT 010:RX弹性缓冲区占用率大于CLK_COR_MAX_LAT 101:RX弹性缓冲下溢 110:RX弹性缓冲区溢出 |

|

| RXBUFRESET |

RX弹性缓冲逻辑的高电平有效复位信号。绕过RX缓冲区时,此选项不可用。 |

|

| RXRATE |

接收速率更改端口。类似于发送时钟 |

|

| QPLLPD |

仅在选择GTX或GTH收发器时可见。 QPLL的断电端口。 |

为了省电,降低功耗,可以对PLL、RX、TX进行断电,带有_PD的就是断电信号, |

| CPLLPD |

仅在选择GTX或GTH收发器时可见。 CPLL的断电端口。 |

|

| PLL0PD |

仅在选择GTP收发器时可见。 PLL0的掉电端口。 |

|

| PLL1PD |

仅在选择GTP收发器时可见。 PLL1的掉电端口。 |

|

| TXSYSCLKSEL |

选择参考时钟源以驱动TX数据路径。 选择PLL时钟源驱动TX数据通路: TXSYSCLKSEL [0] = 1'b0(PLL0) TXSYSCLKSEL [0] = 1'b1(PLL1) 选择参考时钟源驱动TXOUTCLK: TXSYSCLKSEL [1] = 1'b0(来自PLL0的参考时钟) TXSYSCLKSEL [1] = 1'b1(参考时钟形式PLL1) |

|

| RXSYSCLKSEL |

选择PLL时钟源驱动RX数据通路: RXSYSCLKSEL [0] = 1'b0(PLL0) RXSYSCLKSEL [0] = 1'b1(PLL1) 选择参考时钟源驱动RXOUTCLK: RXSYSCLKSEL [1] = 1'b0(来自PLL0的参考时钟) RXSYSCLKSEL [1] = 1'b1(来自PLL1的参考时钟) |

|

| TXPMARESET |

发送器PMA逻辑的高电平有效复位信号。 该端口用于重置TX PMA。它被驱动为高电平然后置为无效以启动TX PMA复位过程。在顺序模式下,激活此端口会重置TX PMA和TX PCS。 |

|

| RXPMARESET |

接收器PMA逻辑的高电平有效复位信号。 此端口被驱动为高电平然后置为无效以启动RX PMA复位过程。 在单模式下,激活RXPMARESET仅重置不包括CDR和LPM的RX PMA块。 在顺序模式下,激活RXPMARESET从RXPMARESET开始RX复位过程,如图ug482_2-18所示,然后是RXCDRPHASERESET,RXCDRFREQRESET,RXLPMRESET,EYESCANRESET,RXPCSRESET和RXBUFRESET。表ug482_2-20列出了顺序模式的详细介绍。 |

|

| TX8B10BEN |

TX8B10BEN设置为高电平以启用8B / 10B编码器。 |

|

| RXCDRHOLD |

保持CDR控制循环冻结。 |

|

| SIGVALIDCLK |

可见GTH或GTP收发器。 OOB电路的时钟。备用时钟源,一般也不用 |

|

| CLKRSVD |

可见GTX收发器。 OOB电路的时钟。 |

|

| TXPIPPMEN |

1'b0:禁用TX相位内插器PPM控制器块。TX PI未使用PI代码更新,并保留以前的PI代码。 1'b1:使能TX相位内插器PPM控制器模块。每个TXPI_SYNFREQ_PPM [2:0]周期使用PI代码更新TX PI。 |

TX相位插值器百万分之一(TXPIPPM)控制器模块支持动态控制TX相位插值器(TX PI)。它位于TX PCS,其输入来自FPGA TX接口,并输出到TX PMA。存在需要对TX PMA中的数据进行微调控制的应用。通过TX PI实现对来自PLL的输出时钟的控制,TX PI又可以由TX相位内插器PPM控制器模块控制。FPGA逻辑可以通过使用PCS中的TX相位内插器PPM控制器模块来控制TX PMA中的TX PI。 |

| TXPIPPMOVRDEN |

1'b0:正常运行。 1'b1:允许直接控制PI码输出到TX PMA中的TX PI。 与TXPPMOVRD_VALUE [6:0]一起使用以编程PI代码的值。 |

|

| TXPIPPMPD |

1'b0:不对TX相位插值器PPM控制器模块断电。 1'b1:关闭TX相位插值器PPM控制器模块。 |

|

| TXPIPPMSTEPSIZE |

TXPIPPMSTEPSIZE [4]:1'b1:递增PI代码1'b0:递减PI代码 TXPIPPMSTEPSIZE [3:0]是增加或减少PI代码的数量。其值范围为0到15。 |

|

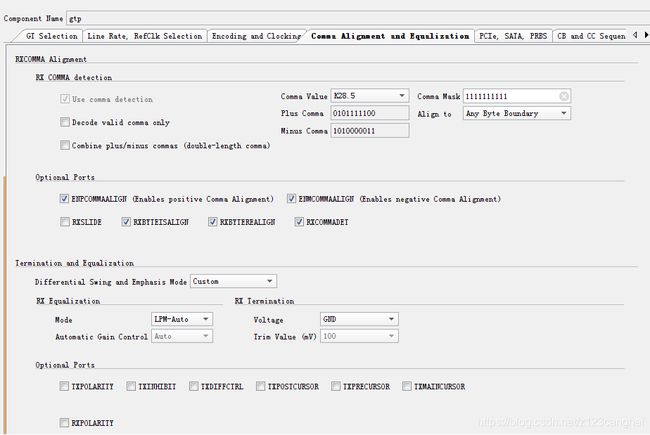

7.4 Alignment, Termination, and Equalization(对齐,终止和均衡)

向导的第4页(图4-13)允许您设置逗号字符并控制接收均衡和终端电压。

Table 4-21: Comma Detection

| 选项 |

描述 |

|

| Use Comma Detection |

启用接收K码检测。 用于标识数据流中的K码字符和SONET框架字符。 |

|

| Decode Valid Comma Only |

启用接收K码检测后,将检测限制为特定的K码。 |

|

| Comma Value |

选择标准逗号模式之一或“用户定义”以输入自定义模式。 |

|

| Plus Comma |

表示要匹配的正差异K码的10位二进制模式(RD+)。 模式的最右边位是串行到达的第一位.XAUI示例使用0101111100(K28.5)。 |

|

| Minus Comma |

表示要匹配的负视差K码的10位二进制模式。 模式的最右边位是串行到达的第一位。XAUI示例使用1010000011(K28.5)。 |

|

| Comma Mask |

10位二进制模式,表示逗号匹配模式的掩码。 1位表示要匹配逗号模式中的相应位。 0位表示不关心逗号模式中的相应位。XAUI示例匹配低7位(K28.5)。 |

|

| Align to... |

Any Byte Boundary |

检测到逗号时,使用逗号模式将数据流与最近的字节边界对齐 |

| Two Byte Boundary |

检测到逗号时,使用逗号模式将数据流与2字节边界对齐 |

|

| FourByte Boundary |

检测到逗号时,使用逗号模式将数据流与4字节边界对齐 |

|

| Optional Ports |

ENPCOMMAALIGN |

高电平有效信号,当检测到K码(RD+)模式时,启用字节边界对齐过程。 |

| ENMCOMMAALIGN |

Active-High信号,当检测到K码(RD-)模式时,启用字节边界对齐过程 |

|

| RXSLIDE |

是用于手动对齐的,高电平有效信号,导致每个断言将字节对齐调整一位。 优先于正常的K码对齐。 |

|

| RXBYTEISALIGNED |

高电平有效信号,表示并行数据流与字节边界对齐。RXBYTEISALIGNED是状态信号,为高电平表示边界已经对齐。这时可以将ENPCOMMALIGN和ENMCOMMALIGN两个信号拉低,关闭K码对齐功能。 |

|

| RXBYTEREALIGN |

RXBYTEREALIGN是状态信号,用来表示对齐的K码是否发生变化或者说现在是否在对齐状态,=1表示字节对齐边界没有改变,=0表示字节对齐边界改变了。所以当RXBYTEREALIGN为0时我们可以重新使能字节对齐。 |

|

| RXCOMMADET |

指示K码对齐逻辑的高电平有效信号已检测到数据流中的K码模式。RXCOMMADET是个状态信号,当K码对齐模块检测到K码时该信号置一,该信号有效几个周期。 |

|

Table 4-22: Pre-emphasis and Differential Swing

| 选项 |

描述 |

| Differential Swing and Emphasis Mode |

指定发射器前置光标预加重模式设置。 选择自定义模式可启用差异摆动和预加重级别的用户驱动设置。XAUI示例使用自定义模式动态设置预加重级别。有关详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 |

| Table 4-23: RX Equalization |

|

| 选项 |

描述 |

| Equalization Mode |

设置接收器中的均衡模式。 有关判决反馈均衡器的详细信息,请参见7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 XAUI示例使用DFE-Auto模式。 |

| Automatic Gain Control |

设置接收器的自动增益控制。 该值可以设置为“自动”或“手动”。 |

| Use RX Equalizer CTLE3 Adaptation Logic (DFE mode only) |

仅适用于GTX收发器。 如果选中,则在示例设计中实例化CTLE3自适应逻辑。 有关更多信息,请参见第5章,示例设计。 |

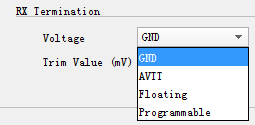

Table 4-24: RX Termination

| 选项 |

描述 |

|

| Termination Voltage |

选择GND会使内部终端网络接地。 选择Floating可隔离网络。 选择AVTT会将内部参考电压源应用于终端网络。 选择终端电压的可编程选项,从下拉菜单中选择RX终端电压。 XAUI示例使用GND设置 |

|

Table 4-25: Optional Ports 主要是GTP收发器TX驱动器的配置

| 选项 |

描述 |

| TXPOLARITY |

TXPOLARITY端口用于反转输出数据的极性。 0:未倒置。TXP为正,TXN为负。 1:倒置。TXP为负,TXN为正。 |

| TXINHIBIT |

高 - 高信号迫使变送器输出到稳定状态。 高电平时,此信号阻止TXDATA的传输,并强制GTPTXP为0,GTPTXN为1。 |

| RXPOLARITY |

RXPOLARITY端口可以反转输入数据的极性: 0:未反转。RXP为正,RXN为负。 1:倒置。RXP为负且RXN为正。 |

| TXMAINCURSOR |

高电平有效信号可启用QPI偏置。 如果TX_MAINCURSOR_SEL属性设置为1'b1,则允许直接设置主光标系数。 51 - TXPOSTCURSOR系数单位 - TXPRECURSOR系数单位 |

| TXPOSTCURSOR |

发射器后置光标TX预加重控制。默认值是用户指定的。Ug482_T3-28续可见所有列出的值(dB)都是典型值。 |

| TXPRECURSOR |

发射器前置TX预加重控制。默认值是用户指定的。所有列出的值(dB)都是典型值。 |

| TXDIFFCTRL |

传输驱动器摆动控制。Ug482_T3-28续可见 |

7.5 选项卡_5 PCIE等

向导的第5页(图4-14)允许您配置PCI Express和串行ATA(SATA)功能的接收器。 此外,还提供了RX带外(OOB)信号,伪随机比特流序列(PRBS)检测器以及通道绑定和时钟校正设置的配置选项。

| 选项 |

描述 |

|

| Transition Time |

To P2 |

整数值介于0到65,535之间。设置计数器以确定PCI Express的P2电源状态的转换时间。有关确定每个计数的时间值的详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。XAUI示例不需要此功能,并使用默认设置100。 |

| From P2 |

整数值介于0到65,535之间。设置计数器以确定PCI Express的P2电源状态的转换时间。有关确定每个计数的时间值的详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 XAUI示例不需要此功能,并使用默认设置60。 |

|

| To/From non-P2 |

整数值介于0到65,535之间。设置计数器以确定与PCI Express以外的电源状态之间的转换时间。 有关确定每个计数的时间值的详细信息,请参阅7系列FPGA GTX / GTH收发器用户指南(UG476)[参考7]。 XAUI示例不需要此功能,并使用默认设置25。 |

|

| Optional Ports |

LOOPBACK |

3位信号使各种数据环回模式能够进行测试。 |

| RXSTATUS |

3位接收器状态信号。该信号的编码取决于RXSTATUS编码格式的设置。 |

|

| RXVALID |

高电平有效PCI Express RX OOB /信标信号。表示RXDATA和RXCHARISK [3:0]上的符号锁定和有效数据。 |

|

| COMINITDET |

Active-High初始化检测信号。 |

|

| COMSASDET |

SATA的高电平有效检测信号。 |

|

| COMWAKEDET |

高 - 高唤醒检测信号。 |

|

| TXCOMINIT |

传输初始化端口。 |

|

| TXCOMSAS |

OOB信号。 |

|

| TXCOMWAKE |

OOB信号。 |

|

| COMFINISH |

完成OOB。 |

|

| TXDETECTRX |

PIPE接口,用于符合PCI Express规范的控制信号。激活PCI Express接收器检测功能。功能取决于TXPOWERDOWN,RXPOWERDOWN,TXELECIDLE,TXCHARDISPMODE和TXCHARDISPVAL的状态。如果RXSTATUS编码格式设置为SATA,则此端口不可用。 |

|

| TXELECIDLE |

将变送器驱动至电气空闲状态(无差分电压)。在PCI Express模式下,此选项用于电气空闲模式。功能取决于TXPOWERDOWN,RXPOWERDOWN,TXELECIDLE,TXCHARDISPMODE和TXCHARDISPVAL的状态。 |

|

| PHYSTATUS |

PCI Express接收检测支持信号。表示完成了几个PHY功能。 |

|

| TXPOWERDOWN |

变送器的断电端口。 |

|

| RXPOWERDOWN |

接收器的断电端口。 |

|

| LOOPBACK |

3位信号使各种数据环回模式能够进行测试。 |

|

| RXSTATUS |

3位接收器状态信号。该信号的编码取决于RXSTATUS编码格式的设置。 |

|

Table 4-28: OOB Signal Detection

| 选项 |

描述 |

| Use RX OOB Signal Detection |

启用内部OOB信号检测器。 OOB信号检测用于PCIe和SATA。 |

Table 4-29: OOB Signal Detection

| 选项 |

描述 |

| Use PRBS Detector |

启用内部PRBS检测器。 应用程序可以使用此功能来实现内置自测试。 |

| Use Port TXPRBSSEL |

选择PRBS传输控制端口。 |

| UsePort TXPRBSFORCEERR |

启用PRBS强制错误控制端口。 该端口控制将错误插入比特流。 |

| RXPRBSERR_LOOPBACK |

选择此选项可将RXPRBSERR位环回到同一收发器的TXPRBSFORCEERR。 |

Table 4-30: Channel Bonding Setup

| 选项 |

描述 |

| Use Channel Bonding |

使用唯一字符序列启用接收器通道绑定逻辑。 识别后,这些序列允许在接收缓冲区中添加或删除字符,以对多个数据收发器进行字节对齐。 |

| Sequence Length |

从下拉列表中选择唯一通道绑定序列中的字符数。 XAUI示例使用1。 |

| Sequence Max Skew |

从下拉列表中选择可以通过通道绑定处理的字符的最大偏斜。 必须始终小于通道绑定序列之间最小距离的一半。 XAUI示例使用7。 |

| Use Two Channel |

激活可选的第二通道绑定序列。 检测任一序列都会触发通道绑定。 |

Table 4-31: Clock Correction Setup

| 选项 |

描述 |

| Use Clock Correction |

使用唯一字符序列启用接收器时钟校正逻辑。 识别后,这些序列允许在接收缓冲区中添加或删除字符,以防止由于发送/接收时钟频率的微小差异导致的缓冲区下溢/溢出。 |

| Sequence Length |

从下拉列表中选择唯一时钟校正序列中的字符数(子序列)。 XAUI示例使用1。 |

| PPM Offset |

表示发送和接收时钟之间的PPM偏移。 |

| Periodicity of the CC Sequence |

指示CC序列在数据流中插入的时间间隔 |

| Use Two Clock Correction Sequences |

激活可选的第二时钟校正序列。 检测任一序列都会触发时钟校正。 |

通道绑定和时钟校正序列

向导的第6页(图4-15)允许您定义通道绑定序列。

表4-32说明了序列定义设置,表4-31,第64页介绍了时钟设置设置。

| 选项 |

描述 |

| Byte (Symbol) |

设置每个符号以匹配协议所需的模式。XAUI序列长度为8位。01111100用于通道绑定。00011100用于时钟校正。其他符号被禁用,因为序列长度设置为1。 |

| K Character |

选择8B / 10B解码时,此选项可用。选中时,与XAUI的情况一样,符号为8B / 10B K字符。 |

| Inverted Disparity |

一些具有8B / 10B解码的协议使用具有故意反转差异的符号。 在序列中预期出现此类符号时,应检查此选项。 |

| Don’t Care |

通过选中此选项,多字节序列可以具有通配符。序列中未使用的字节会自动设置此选项。 |