如何理解negative timing check

最近也是遇到了这个问题,通过周末的研究,感觉自己搞明白了,现在总结一下吧!整体的感受:没事多看看各种manual吧,上面讲的真的比网上说的好太多了,网上各种观点都有,难以确定谁对谁错。当然本文也是基于自己的理解,如有错误欢迎指正。

目录

positive setup hold timing check

$setuphold函数

示例

Negative setup timing check

补充

对于vcs编译选项的解释

和negative timing check相关的编译选项

positive setup hold timing check

$setuphold函数

在工艺厂商提供的工艺库模型中定义了工艺库中用到的所有cell的verilog仿真模型,该模型定义了各种std cell的基本功能以及cell内部的timing check。其中主要以setuphold函数为例说明。该函数可以看做是setup函数和hold函数的组合。同时在SDF3.0版本中,setuphold函数支持negative timing check而单独的setup or hold 函数是不支持negative timing check的。同时在后仿的时候要注意verilog model和SDF在timing cehck的地方要对应,否则就会出现错误。对于recovery 和removal同样,只是简写为$recrem.

verilog 文档对于setuphold函数的定义如下

posedge clock表示referenc_event

data表示data_event

notifer表示notifer寄存器,当出现timing volition时,用户可以选择使用使用某些命令是的notifer的值为X态,即std cell出现X态。

下面四个option都是可选option,当timing check出现负值是才会使用这些option使得timing check更加的准确。

stamptime_condition表示当出现负值的timing check是标记的条件

checktime_condition表示当出现负值的timing check是检查的条件

delayed_reaference 表示delay reference signal for negative timing check

delayed_data表示delay reference data for negative timing check

PS:delayed_reference_signal和delayed_data可以作为正常的singal信号作为某些module的输入。

示例

$setuphold (posedge clock, data, 10, 11, notifyreg)

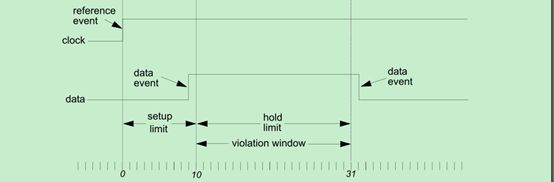

表示在reference event也就是时钟clk上升沿是,data event也就是data的timing要满足的条件,data要在时钟上升沿10ns保持稳定(假设时间单位是ns),在clk上升沿之后11ns内保持稳定。即如下图所示,注意这里的setup和hold的timing检查都是正值。

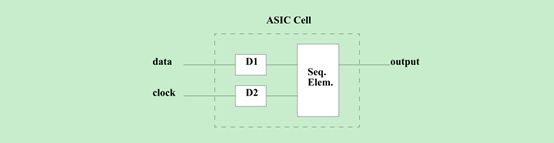

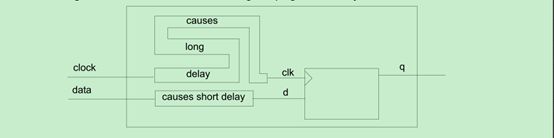

setup或者hold的timing检查也有可能出现负值的情况,在讨论这个问题之前我们先要弄明白我们现在所说的setup hold timing check是针对std cell的,在实际的std cell中不仅仅有DFF还有一些buffer之类的cell,一个典型的std cell的简化结构如下图所示,D1和D2表示两个delay cell。而实际上我们要保证的是DFF的setup 和hold timing check是正值,由于D1和D2两个cell的delay不同就导致了在对std cell做timing check时出现了负值的timing check。再次强调,这里的负值的timing check是针对std cell的并不是针对DFF的。

Negative setup timing check

当clock delay比较大时,即D1 >D2时,对于std cell的setup check就会出现负值。即如下所示。此时,实际到达DFF的clock也就是delayed_reference,实际到达DFF的data就是delayed_data

例如

$setuphold (posedge clock, data, -10, 31, notifyreg);

其timing check如下图所示。

相反在,如果D2>D1, 也就是data delay大于clock delay就会出现negative hold timing check,例如,$setuphold (posedge clock, data, 31, -10, notifyreg);其对于std cell的timing check如下所示。

这就好像是在std cell边界处实现设置了一些余量,从而满足在DFF处timing check。需要注意的是不论setup 或者hold出现负值,但setup和hold的和必须是正值。这是因为setup必然要发生在hold的前面。

补充

对于vcs编译选项的解释

+no_notifier 表示notifer寄存器不进行翻转,X态不会传播,但是vcs还是会报告timing violation

+no_tchk_msg 表示不报告timing violation

+notimingcheck 表示在vcs编译过程中不进行 $setuphold $recrem 等函数的编译,vcs产生delayed_reference_signal 和delayed_reference_data但是不会去标记这些delay的值,从不进行任何的timing检查。

+transport_path_delays 表示vcs能够让pulse宽度小于module内部delay的脉冲进行传播,例如一个脉冲宽度是2ns,但是一个cell内部的delay是7ns,如果使用该选项那么该脉冲是可以穿过module进行传递的。该选项默认是关闭的。如果使用该选项必须配合下面两个选项使用。同样+transport_int_delay解释类似。

+pluse_e/num 表示在脉冲小于或者等于num百分比的时报错,并且传播X态。+pulse_int_e是同样的意思只是针对的是 interconnect delay

+pulse_r/number 表示脉冲宽度小于或者等于num百分比时,vcs会拒绝该脉冲,也就是脉冲无法传递。+pulse_int_r同样的意思。PS error number要大于等于reject number。

PS实际上vcs 将所有delay分为两种 transport delay和 inertial delay(惯性延时)。transport delay上面已经解释了,inertial delay就是指脉冲宽度小于deley 时,脉冲无法传递。默认情况下,Gates, switches, MIPDs, and continuous assignments都是惯性延时。

例如

./leon/iu_verilog2.sdf

line 1804: (INTERCONNECT rst U9846/A (0.000:0.000:0.000))

./leon/iu_verilog2.v

assign \iuo[DEBUG][RST] = rst;

上面的连续赋值语句,对应SDF的反标信息delay是0,但是实际上默认是惯性延时,也就是说net肯定有延时,如果不加transport delay那么SDF就会报告warning,延时信息还是会反标上。

Warning-[SDFCOM_IWSBA] INTERCONNECT will still be annotated ./leon/iu_verilog2.sdf, 1804 module: iu_verilog2, "instance: TBLEON.TB.P0.LEON0.MCORE0.PROC0.IU0.IU1.iu2" SDF Warning: INTERCONNECT from rst to U9846.A has Continuous Assignment at leon/iu_verilog2.v:2736, delay will still be annotated.

和negative timing check相关的编译选项

-negdelay 表示使能SDF文件中的所有的负值。但是要保证setup和hold(rec rem)的和为正值,否则vcs会忽略负值同时给出warning

+neg_tchk 表示当进行negative timing check时必须包含该option,否则vcs会把所有负值变为0,此时上图所有的negative check的violation window都会变大,这会使得timing check很悲观。

+old_ntc 表示vcs不是用delayed referenc signal and delayed reference data去做timing check。这样X态有可能出现在std cell的边界,如果stdcell 内部delay很大,就会出现X在std cell内部被掩盖了,从而无法传播到std cell外边。所以一般情况下vcs手册不建议使用该选项

+NTC2 表示在setuphold 或者recrem检查中使用original signal和data作为timing stamp condition和 timing checking condition,而不是用delay reference singal and data。

+overlap 表示vcs不要改变violation window,如果不加该选项在某些情况vcs会把violation window变大同时使得timing 检查不够准确。如下图所示。如果不加该选项工具会把hold limit都变成0。