HDLBits刷题合集—15 Finite State Machines-1

HDLBits刷题合集—15 Finite State Machines-1

HDLBits-120 Fsm1

Problem Statement

这是一个Moore型状态机,有两个状态,一个输入,一个输出。实现此状态机。注意重置状态是B。

这个练习与下一题fsm1s相同,但是使用异步重置。

module top_module (

input clk,

input in,

input areset,

output out

);

parameter A=0, B=1;

reg state;

reg next;

always@(*) begin

case (state)

A: next = in ? A : B;

B: next = in ? B : A;

endcase

end

always @(posedge clk, posedge areset) begin

if (areset) state <= B; // Reset to state B

else state <= next; // Otherwise, cause the state to transition

end

assign out = (state == B);

endmodule

HDLBits-121 Fsm1s

Problem Statement

这是一个Moore型状态机,有两个状态,一个输入,一个输出。实现此状态机。注意重置状态是B。

这个练习与上一题fsm1相同,但是使用了同步重置。

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

parameter A = 0, B = 1;

reg present_state, next_state;

always @(posedge clk) begin

if (reset)

// Fill in reset logic

present_state <= B;

else

// State flip-flops

present_state <= next_state;

end

always @(*) begin

case (present_state)

A: next_state <= in ? A : B;

B: next_state <= in ? B : A;

endcase

end

assign out = (present_state == B);

endmodule

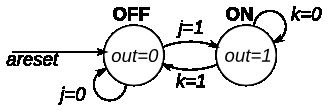

HDLBits-122 Fsm2

Problem Statement

这是一个Moore型状态机,有两个状态,两个输入,一个输出。实现此状态机。

这个练习与下一题fsm2s相同,但是使用异步重置。

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

ON : next_state <= k ? OFF : ON;

OFF: next_state <= j ? ON : OFF;

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if (areset)

state <= OFF;

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON);

endmodule

HDLBits-123 Fsm2s

Problem Statement

这是一个Moore型状态机,有两个状态,两个输入,一个输出。实现此状态机。

这个练习与上一题fsm2相同,但是使用同步重置。

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

ON : next_state <= k ? OFF : ON;

OFF : next_state <= j ? ON : OFF;

endcase

end

always @(posedge clk) begin

// State flip-flops with synchronous reset

if (reset)

state <= OFF;

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON);

endmodule

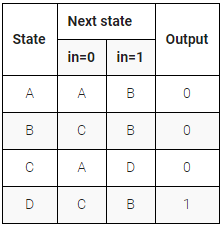

HDLBits-124 Fsm3comb

Problem Statement

下面是Moore型状态机的状态转换表,它有一个输入、一个输出和四个状态。使用以下状态编码:A=2’b00, B=2’b01,C=2’b10, D=2’b11。

仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。给定当前状态(state),根据状态转换表计算next_state和output (out)。

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: next_state = f(state, in)

always @(*) begin

case (state)

A : next_state <= in ? B : A;

B : next_state <= in ? B : C;

C : next_state <= in ? D : A;

D : next_state <= in ? B : C;

endcase

end

// Output logic: out = f(state) for a Moore state machine

assign out = (state == D);

endmodule

HDLBits-125 Fsm3onehot

Problem Statement

以下是具有一个输入,一个输出和四个状态的Moore状态机的状态转换表。 使用以下独热状态编码:A = 4’b0001,B = 4’b0010,C = 4’b0100,D = 4’b1000。

通过假设独热码编码的检查得出状态转换和输出逻辑方程式。 为此状态机仅实现状态转换逻辑和输出逻辑(组合逻辑部分)。(测试台将使用非独热输入进行测试,以确保你没有尝试做更复杂的事情)。

“通过检验推导方程”是什么意思?

独热状态机编码可确保一个状态位恰好为1。这意味着可以通过仅检查一个状态位而不检查所有状态位来确定状态机是否处于特定状态。通过检查状态转换图中每个状态的输入边缘,可以得出用于状态转换的简单逻辑方程式。

例如,在上述状态机中,状态机如何达到状态A?它必须使用两个输入边缘之一:“当前处于状态A,in = 0”或“当前处于状态C,in = 0”。由于采用独热编码,因此测试“当前处于状态A”的逻辑方程只是状态A的状态位。这导致了状态位A的下一个状态的最终逻辑方程:next_state [0] =state[0]&(〜in) | state[2]&(〜in)。独热编码可确保一次最多有一个子句(乘积项)处于“active”状态,因此可以将这些子句进行“或”运算。

当练习“通过检查”要求状态转换方程式时,请使用此特定方法。评判系统将使用非独热输入进行测试,以确保你的逻辑方程式遵循此方法,而不是对状态位的非法(非独热编码)组合进行其他操作(例如,重置FSM)。

尽管知道此算法对于RTL级设计不是必需的(逻辑合成器可以解决这个问题),但它说明了为什么独热FSM常常具有更简单的逻辑(以增加状态位存储为代价),并且该主题经常出现数字逻辑课程的考试中。

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = state[A]&(~in) | state[C]&(~in);

assign next_state[B] = state[A]&(in) | state[B]&in | state[D]∈

assign next_state[C] = state[B]&(~in) | state[D]&(~in);

assign next_state[D] = state[C]∈

// Output logic:

assign out = (state[D] == 1);

endmodule

HDLBits-126 Fsm3

Problem Statement

以下是具有一个输入,一个输出和四个状态的Moore型状态机的状态转换表。 实现此状态机。 包括一个异步重置,将FSM重置为状态A。

module top_module(

input clk,

input in,

input areset,

output out); //

parameter A=0, B=1, C=2, D=3;

reg[2:0] state,state_next;

// State transition logic

always @(*) begin

case (state)

A : state_next <= in ? B : A;

B : state_next <= in ? B : C;

C : state_next <= in ? D : A;

D : state_next <= in ? B : C;

endcase

end

// State flip-flops with asynchronous reset

always @(posedge clk, posedge areset) begin

if (areset)

state <= A;

else

state <= state_next;

end

// Output logic

assign out = (state == D);

endmodule

HDLBits-127 Fsm3s

Problem Statement

以下是具有一个输入,一个输出和四个状态的Moore型状态机的状态转换表。 实现此状态机。 包括一个将FSM重置为状态A的同步重置(这与上一题Fsm3是相同的问题,但是具有同步重置)。

module top_module(

input clk,

input in,

input reset,

output out); //

reg[2:0] state,state_next;

parameter A=1, B=2, C=3, D=4;

// State transition logic

always @(*) begin

case (state)

A : state_next <= in ? B : A;

B : state_next <= in ? B : C;

C : state_next <= in ? D : A;

D : state_next <= in ? B : C;

endcase

end

// State flip-flops with synchronous reset

always @(posedge clk) begin

if (reset)

state <= A;

else

state <= state_next;

end

// Output logic

assign out = (state == D);

endmodule

HDLBits-128 Exams/ece241 2013 q4

Problem Statement

大型水库可为多个用户提供服务。为了使水位足够高,三个传感器以5英寸的间隔垂直放置。当水位高于最高传感器(S3)时,输入流量应为零。当液位低于最低传感器(S1)时,流量应最大(标称流量阀和辅助流量阀均打开)。当水位在上下传感器之间时,流量由两个因素决定:水位和最后一个传感器之前的水位发生变化。每种水位都有一个与之相关的标称流速,如下表所示。如果传感器变化表明先前的液位低于当前的液位,则应进行标称流速。如果先前的水位高于当前的水位,则应通过打开辅助流量阀(由AFR控制)来增加流量。绘制水库控制器的Moore型状态图。清楚指出每个状态的所有状态转换和输出。 FSM的输入为S,S2和S3。输出为FR1,FR2,FR3和AFR。

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

parameter BS1 = 0, BS2 = 1,BS3 = 2,HS3 = 3;

reg [1:0] state;

wire [1:0] state_next;

always @(posedge clk)begin

if (reset)

state <= BS1;

else

state <= state_next;

end

reg state_lower;

always @(posedge clk)begin

if (reset || state < state_next)

state_lower <= 1'b0;

else if (state > state_next)

state_lower <= 1'b1;

end

always @(*)begin

case(state)

BS1:begin

if(s[1])

state_next = BS2;

else

state_next = BS1;

end

BS2:begin

if(s[2])

state_next = BS3;

else if (!s[1])

state_next = BS1;

else

state_next = BS2;

end

BS3:begin

if(s[3])

state_next = HS3;

else if (!s[2])

state_next = BS2;

else

state_next = BS3;

end

HS3:begin

if(!s[3])

state_next = BS3;

else

state_next = HS3;

end

default:

state_next = BS1;

endcase

end

assign fr3 = (state <= BS1) ? 1'b1 : 1'b0;

assign fr2 = (state <= BS2) ? 1'b1 : 1'b0;

assign fr1 = (state <= BS3) ? 1'b1 : 1'b0;

assign dfr = (state == BS1) || state_lower;

endmodule

Note

新手一枚,主要分享博客,记录学习过程,后期参考大佬代码或思想会一一列出。欢迎大家批评指正!