组成原理

1. 8421码:

|

2. 原码—>补码: 正数不变,负数符号位不变,数值位取反加1

补码—>补码的相反数: 连同符号位一起取反加1

3. 原码、反码、补码相互转换:

|

4. 移码: 等于补码的符号(第一位数字)位取反。

移码和补码的关系: 同一数值的移码与补码符号位相反,其它各位相同。

5. 定点数移位规则:

|

6. 十进制负数转换成二进制:

例:-32转成二进制

1.(十进制)32=(二进制)00100000

2.(二进制)00100000逐位取反为:11011111

3. 二进制数+1得:11100000

7. 溢出判断:

|

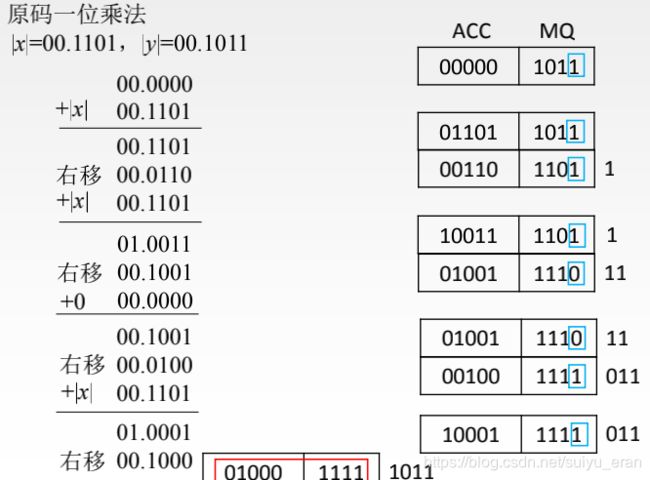

8. 原码一位乘法:

|

9. RAM: 随机存取存储器,通常用作内存

ROM: 只读存储器,通常用作硬盘

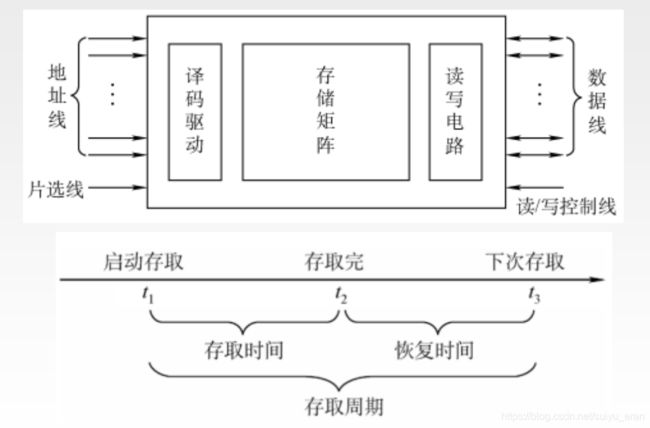

10. 半导体存储芯片的基本结构及存取周期:

|

n位地址 → 2 n \rightarrow 2^n →2n个存储单元 总容量 = 存储单元个数 × \times × 存储字长 = 2 n × 2^n \times 2n× mByte

n对应地址线数目,m对应数据线数目

读写控制线:低电平写,高电平读

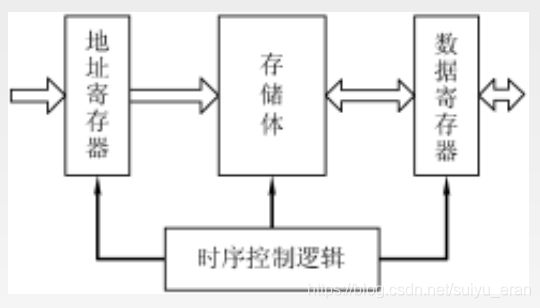

11. 主存储器:

|

12. 大端方式和小端方式:

例:数据为 12345678H

大端方式:12 34 56 78

小端方式:78 56 34 12

13. 半导体随机存储器:

|

14. DRAM的异步刷新: 是集中刷新和分散刷新的结合,一般刷新周期为2ms,在2ms内产生128次刷新请求,所以每隔15.6us内有0.5us的“死时间”

15. 存储器的存取周期是指: 存储器进行连续读或写操作所允许的最短时间间隔

16. Cache/主存系统命中率、平均访问时间问题:

若 t c 表 示 命 中 时 的 c a c h e 访 问 时 间 , t m 表 示 未 命 中 时 的 主 存 访 问 时 间 , 1 − h 表 示 未 命 中 率 , 则 c a c h e / 主 存 系 统 的 平 均 访 问 时 间 t a 为 : 若t_c表示命中时的cache访问时间,t_m表示未命中时的主存访问时间,1-h表示未命中率,则cache/主存系统的平均访问时间t_a为: 若tc表示命中时的cache访问时间,tm表示未命中时的主存访问时间,1−h表示未命中率,则cache/主存系统的平均访问时间ta为:

t a = h t c + ( 1 − h ) t m t_a = ht_c + (1-h)t_m ta=htc+(1−h)tm

设 r = t m / t c 表 示 主 存 慢 于 c a c h e 的 倍 率 , e 表 示 访 问 效 率 , 则 有 : 设r = t_m / t_c表示主存慢于cache的倍率,e表示访问效率,则有: 设r=tm/tc表示主存慢于cache的倍率,e表示访问效率,则有:

e = t c h t c = 1 h + ( 1 − h ) r e = \frac{t_c}{ht_c} = \frac{1}{h+(1-h)r} e=htctc=h+(1−h)r1

17. 主存储器

|

18. MAR与MDR

MAR:主存数据寄存器

MDR:主存地址寄存器

|

19. 寻址方式

|

20. CISC和RISC

CISC :

设计思路:一条指令完成一个复杂的基本功能

代表:×86架构,主要用于笔记本、台式机等

RISC:

设计思路:一条指令完成一个基本的“动作”,多条指令组合完成一个复杂的基本功能

代表:ARM架构,主要用于手机、平板

21. CPU的基本结构

|

22. 指令周期的数据流

(1)取指周期

|

(2)间址周期

|

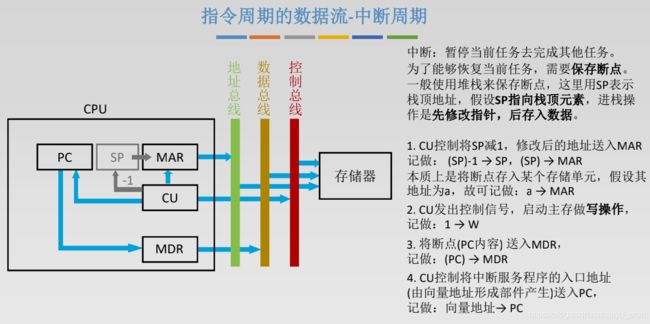

(3)中断周期

|

23. 流水线的性能指标

|

(1)吞吐率: 单位时间内流水线所完成的任务数量,或是输出结果的数量

实 际 吞 吐 率 = n ( k + n − 1 ) Δ t 最 大 吞 吐 率 = 1 Δ t 实际吞吐率=\frac{n}{(k+n-1)\Delta t} 最大吞吐率=\frac{1}{\Delta t} 实际吞吐率=(k+n−1)Δtn 最大吞吐率=Δt1

(2)加速比: 完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比。

设 T 0 T_0 T0表示不使用流水线时的执行时间,即顺序执行所用的时间,则 T 0 = n k Δ t T_0=nk\Delta t T0=nkΔt

T k T_k Tk表示使用流水线时的执行时间,则 T k = ( k + n − 1 ) Δ t T_k=(k+n-1)\Delta t Tk=(k+n−1)Δt

实 际 加 速 比 = k n k + n − 1 最 大 加 速 比 = k 实际加速比 = \frac{kn}{k+n-1} 最大加速比=k 实际加速比=k+n−1kn 最大加速比=k

(3)效率: 流水线的设备利用率称为流水线的效率

效 率 = n k + n − 1 效率=\frac{n}{k+n-1} 效率=k+n−1n

24. 影响流水线的因素

(1)结构相关(资源冲突): 由于多条指令在同一时刻争用同一资源而形成的冲突称为结构相关。

解决办法:

1. 后一相关指令暂停一周期

2. 资源重复配置:数据存储器和指令存储器分开

(2)数据相关(数据冲突): 在一个程序中,存在必须等前一条指令执行完才能执行后一条指令的情况,则这两条指令即为数据相关。

解决办法:

1. 后推法

2. 数据旁路技术

3. 编译优化

数据的基本操作:读(R)、写(W)

冲突的基本类型:写后读(RAW)、读后写(WAR)、写后写(WAW)

(3)控制相关(控制冲突): 当流水线遇到转移指令和其他改变PC值的指令而造成断流时,会引起控制相关。

解决办法:

1. 尽早判断转移,尽早生成转移目标

2. 预取两个方向的目标指令

3. 加快和提前形成条件码

4. 提高转移方向的猜准率

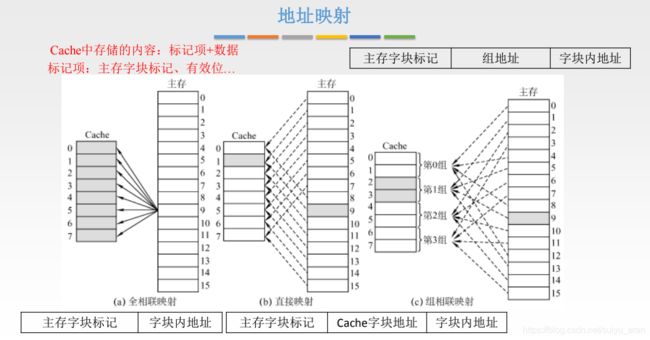

24. 地址映射的三种方式

|

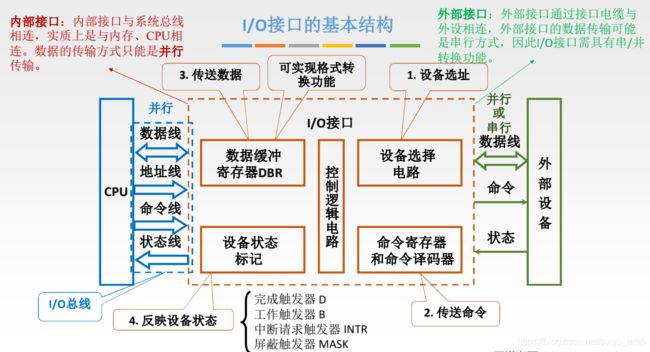

25. I/O接口的基本结构

|

26. 接口与端口

接 口 I n t e r f a c e { 端 口 P o r t { 数 据 端 口 读 & 写 控 制 端 口 读 状 态 端 口 写 逻 辑 控 制 接口Interface \begin{cases}端口Port \begin{cases} 数据端口 读\&写 \\ 控制端口 读 \\ 状态端口 写 \\ \end{cases} \\ 逻辑控制 \\ \end{cases} 接口Interface⎩⎪⎪⎪⎨⎪⎪⎪⎧端口Port⎩⎪⎨⎪⎧数据端口 读&写控制端口 读状态端口 写逻辑控制

I/O端口是指接口电路中可以被CPU直接访问的寄存器。

- I/O方式简介

|

28. 中断服务程序

中断服务程序的流程:

(1)保护现场:保存寄存器的内容,可以使用堆栈,也可以使用特定存储单元来进行保存

(2)中断服务(设备服务):对不同的I/O设备进行不同内容的设备服务

(3)恢复现场:通过出栈指令或取数指令把之前保存的信息送回寄存器中

(4)开中断

(5)中断返回:通过中断返回指令回到原程序断点处

单重中断:执行中断服务程序时不响应新的中断请求。

多重中断:又称中断嵌套,执行中断服务程序时可响应新的中断请求。

中断隐指令:

(1)关中断

(2)保存断点(PC)

(3)引出中断服务程序