TIMING_03 时序分析原理

由于该系列文章阅读有顺序性,所以请跳转至该系列文章第一篇从头开始阅读,并按照文章末尾指示按顺序阅读,否则会云里雾里,传送门在此: https://blog.csdn.net/qq_33486907/article/details/89380368 《TIMING_01 时序约束与时序分析引导篇》

目录

1 时序分析原理

1.1 发射沿和捕获沿

1.2 4类时序路径(FPGA系统)

1.3 时序路径解析

1.4 数据到达时间(Data Arrival Time)

1.5 时钟到达时间(Clock Arrival Time)

1.6 建立时间情况下的数据需求时间分析(Data Required Time – Set up)

1.7 保持时间情况下的数据需求时间分析(Data Required Time – Hold)

1.8 建立时间和保持时间余量

1.9 余量公式

1.10 为什么会余量为负?

1.11 总结

1 时序分析原理

在学习如何在FPGA中进行时序约束和时序分析之前,首先要先学习时序分析的原理,这一章使用最经典的时序模型开始分析并学习时序分析原理;

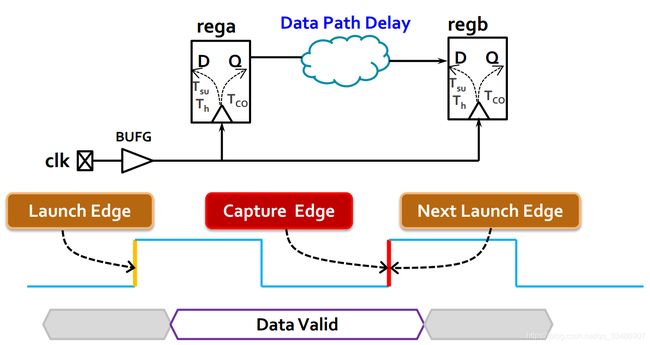

1.1 发射沿和捕获沿

(经典时序分析模型)

发射沿(Launch Edge):源端寄存器发送数据的边沿;

捕获沿(Capture Edge):目的端寄存器捕获数据的边沿;

通常情况下捕获沿和发射沿有一个时钟周期的延迟,同时目的端寄存器的捕获沿也是源端寄存器向下一级发送数据的发射沿,这样就构成了一个经典的时序模型,同时源端寄存器和目的端寄存器不用区分是否位于不同的芯片中,分析模型都是一样的;

1.2 4类时序路径(FPGA系统)

| 时序路径描述 |

名称 |

路径起始点 |

路径终点 |

| (1)输入端口到内部时序原件的路径 |

Input Delay |

DeviceA/clk |

rega/D |

| (2)内部时序原件之间的路径 |

Data path Delay |

rega/clk |

regb/D |

| (3)内部时序原件到输出端口的路径 |

Output Delay |

regb/clk |

DeviceB/D |

| (4)端口到端口的时序路径 |

Data path Delay |

Input/dinb c |

Output/doub c |

实际上前3类路径可以视为同一种路径,分析原理是一样的;

1.3 时序路径解析

| Path |

Start Point |

End Point |

| Source Clock Path |

Clk input port |

Clk pin of launch reg |

| Data Path |

Clk pin of launch reg |

Data input pin of capture reg |

| Destination Clock Path |

Clk input port |

Clk pin of capture reg |

1.4 数据到达时间(Data Arrival Time)

数据到达时间描述的是:数据发送沿发起之后,数据经过多长时间达到目的寄存器的数据捕获端口; 这里将发送沿作为0时刻基准点。

1.5 时钟到达时间(Clock Arrival Time)

时钟达到时间描述的是:时钟到达目标寄存器时钟输入引脚的时间;

1.6 建立时间情况下的数据需求时间分析(Data Required Time – Set up)

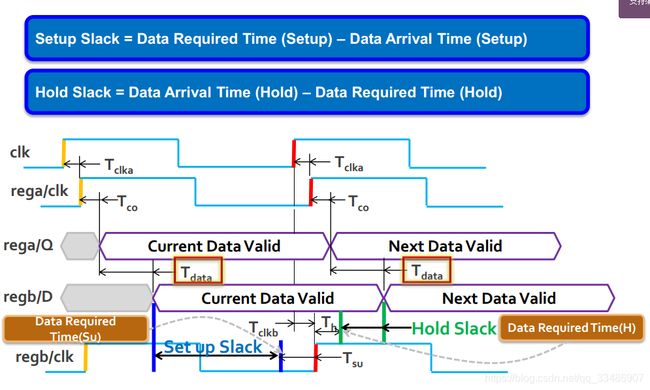

Data Required Time – Set up:目标寄存器捕获数据所需的最短时间;

1.7 保持时间情况下的数据需求时间分析(Data Required Time – Hold)

Data Required Time – Hold:目标寄存器捕获数据后保持稳定所需的最小时间;

1.8 建立时间和保持时间余量

满足建立时间要求的余量:它确保启动的数据及时到达,以满足捕获需求;

满足保持时间要求:它确保捕获数据不会被来自另一个启动边缘的数据损坏。它还可以防止“双时钟”;

1.9 余量公式

余量值为正,则满足时序要求; 余量为负,则不满足时序要求;适用于所有的时序路径:内部、I/O和异步控制;

Data Arrival Time(Hlold) = Data Arrival Time(Setup) + Tclk

1.10 为什么会余量为负?

(1)建立时间余量为负?(建立时间违规)

Setup Slack = Data Required Time( Setup) – Data Arrival Time(Setup)

= ( Clock Arrival Time – Tsu – Set up Uncertainty) - ( Launch Edge + Tclka + Tco + Tdata )

设定Launch Edge = 0 取Launch Edge为0时刻:

上式 = Ts + Tclkb - Set up Uncertainty – Tsu – Tclka – Tco – Tdata

一般 Set up Uncertainty Tsu Tco是寄存器的固有属性(和工艺相关),很难改变; Tdata 过大则成为建立时间违规的最大原因,Tdata 可理解为组合逻辑延迟、线延迟等的综合结果。设计中也往往通过分解组合逻辑的大小来解决建立时间违规的问题。Tclka和Tclkb则是和布局布线相关的参数,在FPGA内部使用全局时钟网络来讲相差是很小的。

注:Ts = 一个时钟周期的时间长度

(2)保持时间为负?(保持时间为例)

Hold Slack = Data Arrival Time ( Hold) – Data Required Time (Hold)

= (Launch Edge + Tclka + Tco + Tdata + Tclk)- (Clock Arrival Time + Th + Hold Uncertainty)

= Launch Edge + Tclka + Tco + Tdata + Ts - Ts - Tclkb – Th - Hold Uncertainty

设定Launch Edge = 0 取Launch Edge为0时刻:

上式 = Tclka + Tco + Tdata - Tclkb – Th - Hold Uncertainty

一般 Hold Uncertainty Th Tco是寄存器的固有属性(和工艺相关),很难改变;但这里并不能理解为Tdata 太小导致了保持时间余量为负,而是Tclkb太大,也就是时钟歪斜(skew)过大导致的。

1.11 总结

Setup Slack = Data Required Time( Setup) – Data Arrival Time(Setup) > 0 ;即 Ts + Tclkb - Set up Uncertainty – Tsu – Tclka – Tco – Tdata > 0 ;假如在FPGA内部忽略时钟歪斜和Set up Uncertainty等因素,可以获得一个基本的建立时间分析模型: Ts > Tco + Tdata + Tsu

不要急着跑,干货在后面,下一篇文章传送门在此:

https://blog.csdn.net/qq_33486907/article/details/89393829

《时序约束的一般步骤》