英伟达 Jetson TX2 新增USB3.0

英伟达Jetson TX2 默认只打开了一个USB3.0接口,而我们项目需要两个USB3.0接口,同时保留2lane PCIE 接三星 SSD M.2固态硬盘。需要更改默认配置

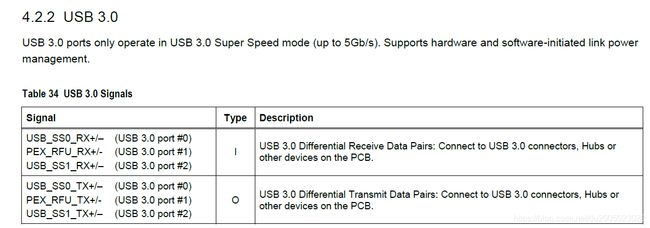

7.1 USB3.0 引脚定义

Jetson_TX2_TX2i_Module_DataSheet_v01.pdf 文件中定义的USB3.0 引脚定义

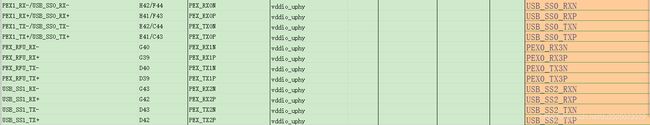

Jetson-TX2-Generic-Customer-Pinmux-Template.xlsm 文件中定义了引脚定义

引脚名可参考Jetson_TX2_TX2i_Pin_and_Function_Names_Guide_Application_Note.pdf

Table 8. Chip, Module, and Carrier Board Pinout

新C2 载板定义了USB引脚连接,只使用了USB3.0_0 USB3.0_1 两个USB3.0接口

而系统默认只开启了USB3.0_1,

参见Tegra_Linux_Driver_Package_TX2_Adaptation_Guide.pdf 中

7.2 修改tegra186-quill-power-tree-p3310-1000-a00-00.dtsi

hardware/nvidia/platform/t18x/common/kernel-dts/t18x-common-platforms/tegra186-quill-power-tree-p3310-1000-a00-00.dtsi 更改

vbus-2-supply = <&vdd_usb2_5v>; 改为 vbus-2-supply = <&battery_reg >;

pinctrl@3520000 {

vbus-0-supply = <&vdd_usb0_5v>;

vbus-1-supply = <&vdd_usb1_5v>;

vbus-2-supply = <&battery_reg>;

vbus-3-supply = <&battery_reg>;

vddio-hsic-supply = <&battery_reg>;

avdd_usb-supply = <&spmic_sd3>;

vclamp_usb-supply = <&spmic_sd2>;

avdd_pll_erefeut-supply = <&spmic_sd2>;

};

7.3 修改ODMDATA值

修改jetpack/64_TX2/Linux_for_Tegra/p2771-0000.conf.common ODMDATA的值修改为0x3090000, 改成了配置6,2个USB3.0

process_board_version()

{

local kerndtbfab="-c03"; # default = C03

ODMDATA=0x3090000; # default = C0X

7.4 修改USB-Lane Mapping

USB lane mapping information is in TX2 adaptation guide. To change the configuration correctly, you need to notice if plugin-manager is working or not.(以下内核打印信息 dmesg 查看)

[ 0.142498] node /plugin-manager/fragment-500-pcie-config match with board >=3310-1000-500

[ 0.142936] node /plugin-manager/fragment-500-xusb-config match with board >=3310-1000-500

[ 0.143213] node /plugin-manager/fragment-500-e3325-pcie match with board >=3310-1000-500

修改

hardware/nvidia/platform/t18x/common/kernel-dts/t18x-common-plugin-manager/tegra186-quill-p3310-1000-a00-plugin-manager.dtsi关于上面的片段

fragment-500-pcie-config {

ids = ">=3310-1000-500";

override@0 {

target = <&tegra_pcie>;

_overlay_ {

pci@1,0 {

nvidia,num-lanes = <2>;

};

pci@2,0 {

nvidia,num-lanes = <1>;

};

pci@3,0 {

nvidia,num-lanes = <1>;

};

};

};

};

/***************************************************************

fragment-500-xusb-config {

ids = ">=3310-1000-500";

override@0 {

target = <&{/xhci@3530000}>;

_overlay_ {

phys = <&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(0)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(1)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(2)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_USB3_P(0)>;

phy-names = "utmi-0", "utmi-1", "utmi-2", "usb3-0";

};

};

override@1 {

target = <&tegra_xusb_padctl_pinmux_default>;

_overlay_ {

usb3-std-A-port2 {

nvidia,lanes = "usb3-0";

};

e3325-usb3-std-A-HS {

status = "okay";

};

};

};

};

************************************************************/

/*****************************************

fragment-500-e3325-pcie {

enable-override-on-all-matches;

ids = ">=3310-1000-500";

odm-data = "enable-pcie-on-uphy-lane0";

override@0 {

target = <&{/xhci@3530000}>;

_overlay_ {

phys = <&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(0)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(1)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(2)>;

phy-names = "utmi-0", "utmi-1", "utmi-2";

};

};

override@1 {

target = <&tegra_xusb_padctl_pinmux_default>;

_overlay_ {

usb3-std-A-port2 {

status = "disabled";

};

};

};

override@2 {

target = <&tegra_main_gpio>;

_overlay_ {

pcie0_lane2_mux {

status = "okay";

};

};

};

};

*********************************************************/

7.5 将修改tegra186-quill-p3310-1000-c03-00-base.dts

hardware/nvidia/platform/t18x/quill/kernel-dts/tegra186-quill-p3310-1000-c03-00-base.dts

gpio@2200000 {

sdmmc-wake-support-input {

status = "okay";

};

sdmmc-wake-support-output {

status = "okay";

};

pcie0_lane2_mux {

status = "disabled";

};

};

pcie-controller@10003000 {

pci@1,0 {

nvidia,num-lanes = <2>;

nvidia,disable-clock-request;

status = "okay";

};

pci@2,0 {

nvidia,num-lanes = <1>;

status = "okay";

};

pci@3,0 {

nvidia,num-lanes = <1>;

status = "disabled";

};

};

xhci@3530000 {

phys = <&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(0)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(1)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_UTMI_P(2)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_USB3_P(0)>,

<&tegra_xusb_padctl TEGRA_PADCTL_PHY_USB3_P(1)>;

phy-names = "utmi-0", "utmi-1", "utmi-2", "usb3-0", "usb3-1";

};

pinctrl@3520000 {

pinmux {

usb3-std-A-port2 {

nvidia,lanes = "usb3-0";

nvidia,port-cap =

status = "okay";

};

usb3-std-A-port3 {

nvidia,lanes = "usb3-1";

nvidia,port-cap =

status = "okay";

};

e3325-usb3-std-A-HS {

status = "okay"; //This is usb2.0 port on M.2

};

};

};

7.5 将修改tegra186-quill-p3310-1000-a00-00-base.dts

hardware/nvidia/platform/t18x/quill/kernel-dts/tegra186-quill-p3310-1000-a00-00-base.dts

chosen {

bootargs = "root=/dev/mmcblk0p1 rw rootwait fbcon=map:0 net.ifnames=0 console=tty0 OS=l4t console=ttyS0,115200n8 ";

board-has-eeprom;

stdout-path = "/serial@3100000";

plugin-manager {

odm-data {

l4t;

};

};

};

7.6 编译内核模块

export CROSS_COMPILE=aarch64-linux-gnu-

export TEGRA_KERNEL_OUT=./kernel_out

export ARCH=arm64

mkdir $TEGRA_KERNEL_OUT

make O=$TEGRA_KERNEL_OUT modules

make O=$TEGRA_KERNEL_OUT modules_install

编译完成后 内核模块位于 ubuntu /lib/modules/目录下

注意:编译完成的内核模块 4.4.38 需要拷贝至 TX2 /lib/modules目录下,否则固态硬盘无法使用

注意: /lib/modules/4.4.38 目录下的build目录指向kernel_out目录,需要删除链接文件 并且创建build目录

在kernel_out 执行make clean 后,将该目录下所有的文件拷贝至 /lib/modules/4.4.38/build目录下