【梳理】计算机组成与设计 第4章 处理器 第1节 数据通路(内附文档高清截图)

配套教材:

Computer Organization and Design: The Hardware / Software Interface (5th Edition)

建议先修课程:数字逻辑电路、C / C++、汇编语言。

这是专业必修课《计算机组成原理》的复习指引。建议将本复习指导与博客中的《简明操作系统原理》配合复习。

在本文的最后附有复习指导的高清截图。需要掌握的概念在文档截图中以蓝色标识,并用可读性更好的字体显示 Linux 命令和代码。代码部分语法高亮。

计算机组成原理不是语言课,本复习指导对用到的编程语言的语法的讲解也不会很细致。如果不知道代码中的一些关键字、指令或函数的具体用法,你应该自行查找相关资料。

第四章 处理器

第一节 数据通路

1、回忆在数字逻辑电路课程中学习到的内容:集成触发器作为计算机的各种芯片中的基本部件,常采用边沿触发(edge-trigger)方式进行工作:由专门的时钟(clock)信号来控制数字电路的动作。只有时钟在上升沿(正沿)或下降沿(负沿)时,读写等动作才被允许进行。这保证了在数字电路的动作期间,输出结果不因输入的波动而引起变化,大大提高了计算机的稳定性和抗干扰能力。

2、寄存器堆(register file)指的是多个寄存器组成的阵列通常由快速的静态随机读写存储器(SRAM)实现。 这种RAM具有专门的读端口与写端口,可以多路并发访问不同的寄存器。每个寄存器用寄存器号(register number)来唯一标识。

3、数据通路(datapath),指的是指令执行过程中,数据所经过的路径,包括路径中的部件。

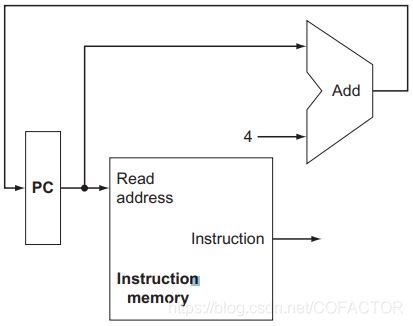

下图是一个数据通路的一部分。这部分用于实现程序计数器的自增(增加4)和取指令。取到的指令被数据通路的其它部分使用。

本节的图和表格的内容不用背下来,能看着图表流利说出不同的指令怎样通过数据通路即可。

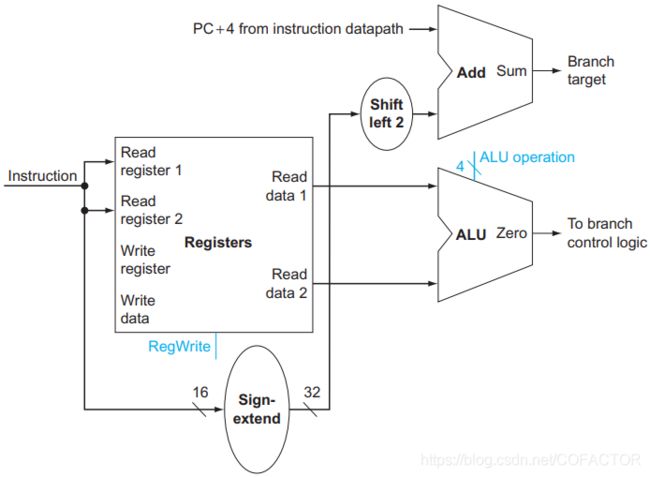

4、基于MIPS指令集架构的处理器中的一个处理分支指令beq的数据通路示例如下:

取指令后,指令中刻画偏移的立即数进行带符号扩展。由于MIPS的所有指令都按4字节对齐,所以刻画偏移的立即数要左两位。这不需要用到一整个功能完全的位移单元,因为位移方向和位数都是固定的,所以可以只用高度简化的硬件。加法器用于根据基址(取指令后为PC的值+4)和偏移地址来计算出条件分支的目标地址。指令被按照指令格式分成若干部分,传入相应的端口。Read Register端输入的是寄存器号(5个bit),Read Data端用于输出读取到的数据。一个专门的ALU用于比较beq中的两个数(从寄存器传入)是否相等。比较的实现方式是相减,当两数相等时输出0。条件判定的结果会被输出到分支控制逻辑,后者决定是否跳至分支目标。ALU Operation端用于输入控制信号,ALU根据输入的不同来执行不同的运算。出于简便的考虑,ALU的端口并未全部画出。

5、MIPS指令集允许延迟分支,也就是说无论分支的条件是否成立,有一些指令总是在顺序执行或跳至分支之前先执行。

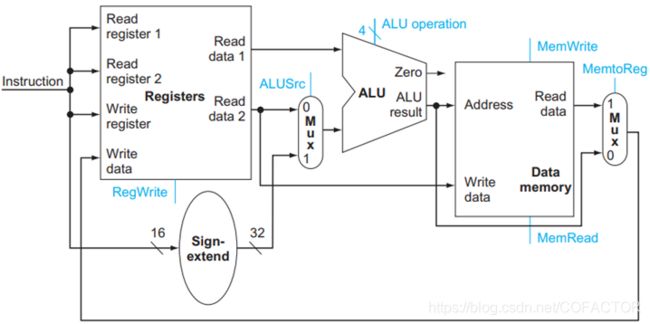

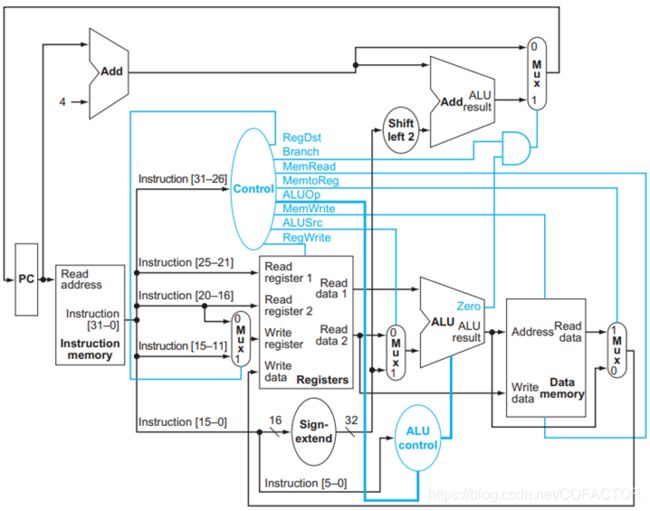

6、以下是基于MIPS的CPU的一条数据通路:

指令根据指令格式拆分成若干部分进入不同端口。R型指令的目标寄存器号和源寄存器号分别进入Write register和Read register端。虽然指令中的一部分也会一同输入Sign-extend端(当指令格式不包含16位偏移时,输入的是不正确的内容),但是接下来的MUX会根据控制信号(随指令的不同而不同)决定输出哪一路给ALU。ALU的运算结果同时输入到内存的Address端和Write data端。之后的MUX也会根据指令的类型选择正确的一路(地址或算术、逻辑等表达式的值)输出。有的指令要求将内存中的数据输出到寄存器(例如load指令),那么MentoReg和RegWrite信号输入有效,相应数据被写入寄存器。有的指令只要求将结果写入寄存器,那么MemtoReg无效,RegWrite有效,运算结果经过最右侧的MUX后被写入寄存器。

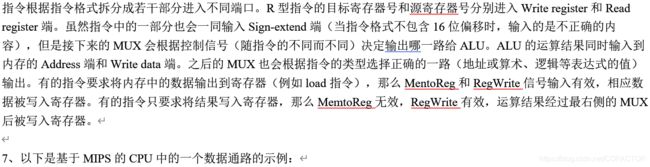

7、以下是基于MIPS的CPU中的一个数据通路的示例:

取指令的时候,指令地址由PC给出,传入指令内存的Read address端。PC的值和常数4被送入一个单独的ALU中进行PC的自增。取得的指令从指令内存送入寄存器和负责符号扩展的专用电路。如果指令包含偏移地址,那么16位的偏移地址在符号扩展后左移2位,通过专门的ALU计算新的地址。由PCSrc端输入控制信号的MUX会根据指令的类型输出新的PC值:对非跳转指令,PC正常+4;如果要求跳转,就输出跳转的目标地址。剩下的部分和上一个图相同。也就是说这个数据通路比上一个数据通路多了一个功能:处理分支。

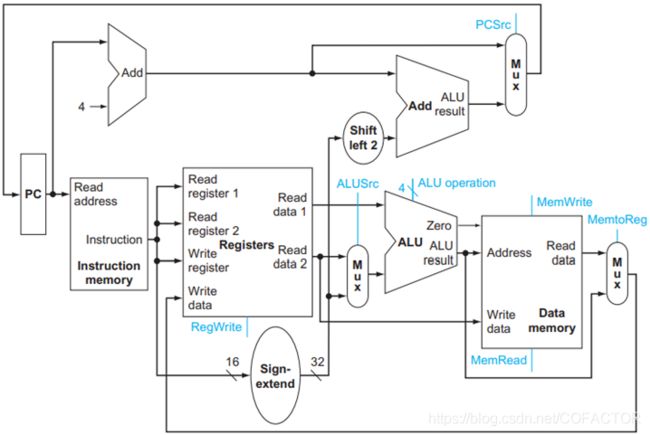

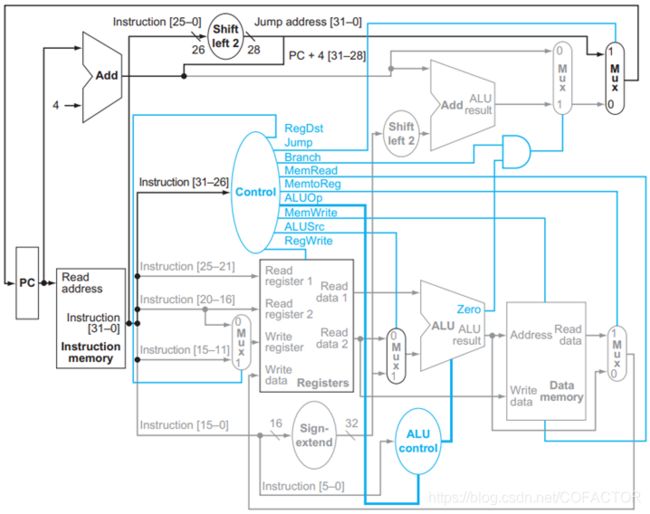

8、以下是基于MIPS的CPU的一条更完整的数据通路:

回忆MIPS的指令格式:

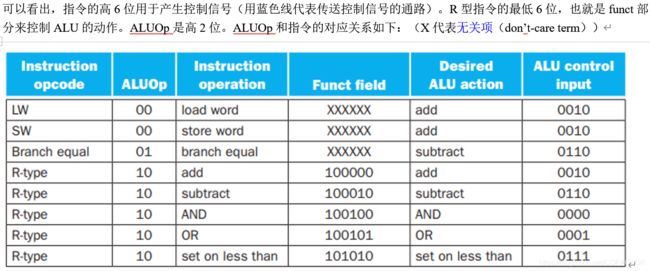

可以看出,指令的高6位用于产生控制信号(用蓝色线代表传送控制信号的通路)。R型指令的最低6位,也就是funct部分来控制ALU的动作。ALUOp是高2位。ALUOp和指令的对应关系如下:(X代表无关项(don’t-care term))

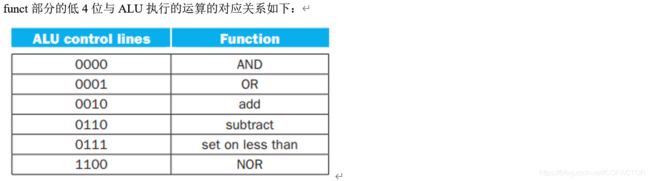

funct部分的低4位与ALU执行的运算的对应关系如下:

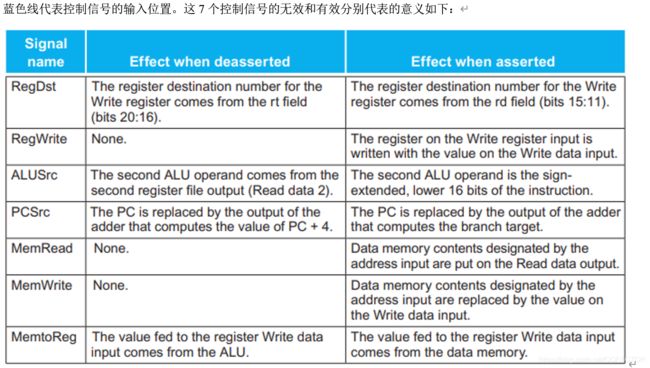

蓝色线代表控制信号的输入位置。这7个控制信号的无效和有效分别代表的意义如下:

电路图上没有标出控制信号PCSrc:这个信号改为由右上角的与门给出。当beq指令的分支条件满足时,Branch端和ALU的0输出端同时输出高电平,与门输出高电平,PC的值为分支的目标地址。

不同类型指令的操作码和控制信号如下:

至此,一个单周期的实现就基本完成了。这条数据通路已经可以正确执行绝大多数MIPS指令。

9、我们为上面的数据通路添加无条件跳转指令。MIPS的跳转指令j的格式如下:

添加该功能后,执行j的数据通路如下:

右上角多了一个MUX。取完j指令后PC已经加了4,这部分会与跳转的左移两位后的偏移合并为新的地址。

10、虽然上述单周期设计已经能正确工作,但现今的芯片中,除非芯片非常简单,否则一般不会使用这种设计了。一个芯片能跑多高的频率,是受最长的数据通路制约的。LOAD指令经过的数据通路一般最长,比如在上述设计中,执行一次要经过5个功能模块:指令内存、寄存器堆、ALU、数据内存、寄存器堆。虽这个指令能在1周期内完成,不过就因为这个周期最长的指令,我们不能把芯片的运行频率设定得过高,否则该指令就无法在1周期内正确执行完毕。下一节我们介绍流水线,这是进一步提升性能的重要方式。

![]()