基于FPGA的IIC的软硬件设计

基于FPGA的IIC的软硬件设计

IIC是多主设备的总线,IIC没有物理的芯片选择信号线,没有仲裁逻辑电路,只使用两条信号线——serial

data(SDA)和serial clock(SCL)。

IIC协议规定:

1、每一支IIC设备都有一个唯一的七位设备地址。

2、数据帧大小为8位的字节。

3、数据(帧)中的某些数据位,用于控制通信的开始、停止、方向(读写)和应答机制。

IIC数据传输速率有标准模式(100kbps)、快速模式(400kbps)和高速模式(3.4Mbps),另外一些变种实现了低速模式(10kbps)和快速+模式(1Mbps)。

物理实现上,IIC总线由两根信号线和一根地线组成。两根信号线都是双向传输的,。IIC协议标准规定发起通信的设备称为主设备,主设备发起一次通信后,其它设备均为从设备。

IIC的特色——用很轻盈的架构实现了多主设备仲裁和设备路由。这个是IIC的突出优点。

以AT24CM01为例实现FPGA的硬件和软件设计。

AT24CM01的大致参数:

电压输入范围:VCC = 1.7V

to 5.5V

存储容量:Internally

Organized as 131,072 x 8 (1M)

工业级温度范围:-40°C至+85°C

I2C兼容(双线)串行接口:

–100 kHz标准模式,1.7V至5.5V

–400 kHz快速模式,1.7V至5.5V

–1 MHz快速模式增强(FM+),2.5V至5.5V

256字节页写入模式:

–允许字节写入和部分页写入

随机和顺序读取模式

多片芯片可以采用级联的方式进行配合使用,通过设置不同的物理地址来实现通信。

由于只使用一片存储,电源电压为3.3V,数据线和时钟线上拉,硬件地址设置为00,时钟采用100KHz。原理图如下图

在完成硬件设计后需要进行时序逻辑的设计:

时序逻辑设计需要进行以下两部分设计:1、时钟和数据相对位置的设计。2、IIC交互协议设计。

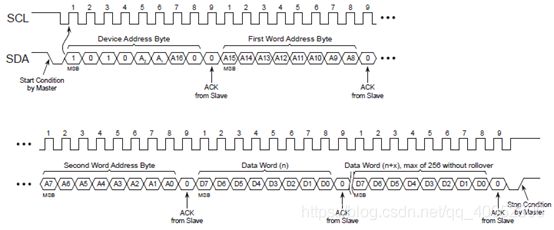

从上图可以看出一下信息:

1、数据是在时钟高电平有效,低电平时发生变化。

2、时钟频率,这里采用标准的100KHz作为芯片的时钟频率。这样时钟的高低电平时间为5000ns.

3、得到时钟频率后需要对时钟和数据信号质量进行约束,这里时钟上升沿和下降沿最大不超过300ns。

4、数据的开始和结束是在时钟为高电平时产生的,建立时间相对于时钟下降沿至少保持600ns,保持时间相对于上升沿至少保持600ns,这里在时序设计时数据线在时钟高电平中点出发生变化,这样可以满足开始时序的建立和保持时间。

5、相对于时钟下降沿时数据输出时间为50ns-900ns

6、在完成开始后,数据的建立时间相对于时钟上升沿至少保持100ns,保持时间相对于下降沿至少保持0ns,这里在时序设计时数据线在时钟低电平中点出发生变化,这样可以满足数据时序的建立和保持时间。

7、结束信号在时钟高电平时数据线为高电平,高电平保持时间最小为50ns.

2、IIC交互读写设计

Bit3-bit2:从设备硬件地址

Bit1:数据地址最高位

Bit0:读写标志,高电平读,低电平写。

![]()

Bit15-bit8:数据地址

![]()

Bit7-bit0:数据地址

读写操作的过程:无论读还是写,都需要先写入地址,然后根基读写标志位进行读写操作。

在进行页读写时,一页长度是256字节,所以页读写的时候最大长度是256.

1字节开始标志+1字节的设备地址字节+1bit的ACK+数据地址高8位+1bit的ACK+数据地址低8位+1bit的ACK+1字节的写入数据+ACK+结束位。

页写的写入顺序:

先写入起始地址,这里起始地址应该是256的整数倍,这样写入刚好写入一页。

单个字节的读方法与写稍微不同。若要读出数据,首先写入读出数据的地址,然后写入设备地址,收到从机ACK后开始接收从机数据,每次接收一个字节数据回应ACK,一直接收直至主机回复NACK,从机结束数据读出。

页读是在单个数据的读基础上,读出想要数量的数据后回复NACK。

在对IIC操作时可以读写分开来写状态机,也可以一起来实现。读写操作的状态机如下图所示,如何要进行页写或者任意长度读取时只需要在wr_data和rd_data两个状态加入读写数量判断即可。

在实现IIC的数据线三态门时这里推荐使用IOBUF原语来实现。原语如下:

// 单端双向缓冲器

IOBUF #(

.DRIVE(12),

.IOSTANDARD("DEFAULT"),

.SLEW("SLOW")

)

IOBUF_inst(

.O(iic_data_out), //输出

.IO(iic_dat),

.I(iic_data_in), //输入

.T(iic_data_in_en) //3-state enable input, high=input,

low=output

);

这个原语的用法可以去xilinx官网上去下载文档去看相关介绍。这个应用代码可以留言发送到邮箱,网页上不方便贴上去,也可以去看小梅哥的博客,那里有一些代码。IIC的仿真图和chipscope抓取数据如下图

![]()

经过多次测试可以正确的实现数据的写入和任意字节的读出。

在实际的调试中如果出现问题了也不用着急,这个总线速率较低,用示波器可以一点一点的去测试调试。