基于FPGA的DP83867IRRGZ网络芯片的配置和调试过程问题记录

在对DP83867IRRGZ网络芯片进行调试时出现一些异常,这是在调试中出现的异常的记录。现这些问题已经得到解决,主要是通过软件调制来解决,但是硬件存在的问题已经定位,下一版本硬件再进行更改。解决思路在我的博客文章“利用FPGA实现UDP网络高速可靠传输”中有详细的描述,并通过实际测试实现600M连续传输。利用wireshark测试百万包丢包率是1.3包。有需要详细了解的可以留言。链接是https://blog.csdn.net/qq_40052606/article/details/106954894。

1 遇到的问题

在调试过程中主要面临两种异常情况:

1、上电复位后出现ping不通的现象。

2、收到UDP命令,FPGA上发数据但上位机接收不到数据现象。

3、ARP请求一直是通的,但ICMP不通。

2 前期准备和可能存在的问题

首先根据FPGA代码了解到网络传输的五层结构模型,TCP/IP五层模型:

物理层:调制解调器 光导纤维 同轴电缆 双绞线等物理介质上传输的信号

数据链路层:Wi-Fi(IEEE 802.11) WiMAX(IEEE 802.16) ARP RARP 等

网络层协议:IP (IPv4 IPv6) ICMP ICMPv6 IGMP 等

传输层协议:TCP UDP TLS DCCP 等

应用层协议:DHCP DNS FTP Gopher HTTP IMAP4 等

根据上面的五层模型,结合实际的硬件和代码,对遇到的问题讨论结果如下:

1、 针对随机出现的ping不通现象,可能是硬件电压不稳定导致的。需要对PHY芯片外围电路电压进行测试。

2、 PHY芯片初始化配置有问题。

3、 底层代码MAC核配置有问题。

4、 UDP、ARP和ICMP代码存在问题。

3、问题分析

1 外围电压测试

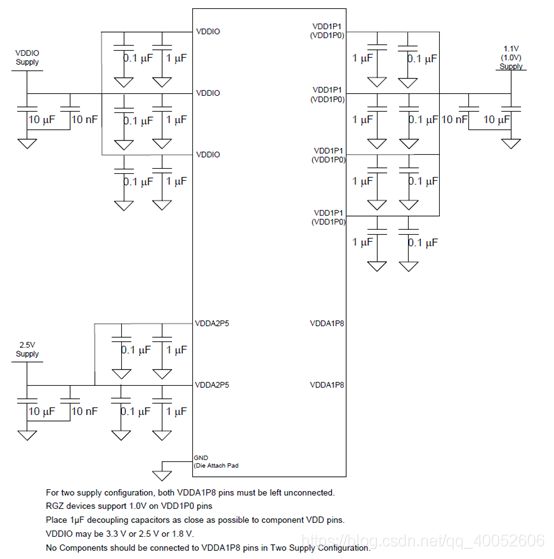

外围电压(如图所示)测试主要对3.3V 2.5V

1.8V和1.0V电压进行了测试。在对这几个电压测试时发现1.8V电压上叠加了一个波动为200mV的正弦电压,电压的不稳定可能会导致PHY进行数据交互时数据的错误和连接的突然断开。电压纹波较大对DDR数据影响较大。参考数据手册对电源输入的要求测试板卡实际的电压。最好使用示波器检测电压纹波。

2 PHY芯片初始化配置

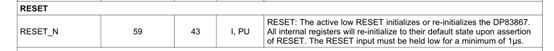

PHY芯片在使用时主要关心功能寄存器的配置和复位引脚的使用。根据数据手册复位引脚描述如下图2,也就是当外部给与一个大于1微秒的低电平信号时PHY芯片进行复位,系统复位后所有寄存器回复初始化,需要从新对寄存器进行配置。在FPGA底层代码里面也是在每次复位后对寄存器进行配置。

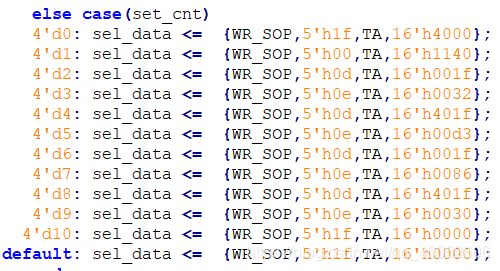

在对PHY芯片初始化配置代码时,对寄存器进行配置,寄存器配置如下图,配置逻辑是:

(1)首先对寄存器16’h001F写入16’h4000,这样保证了在外部复位的情况下不对寄存器数值复位,防止外部或者软件复位影响对寄存器的配置,如图所示。

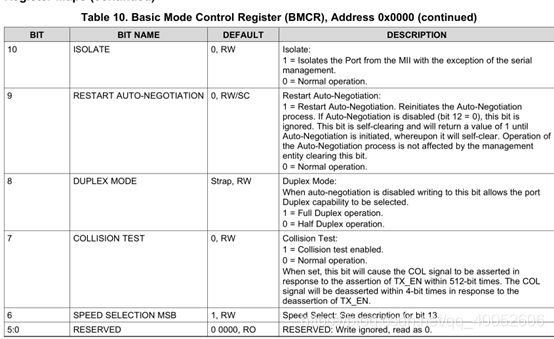

(2)配置16’h0000寄存器,这里写入16’h1140,使得PHY芯片自适应网络速度,但下面寄存器配置了数据通信为RGMII方式,如图所示。

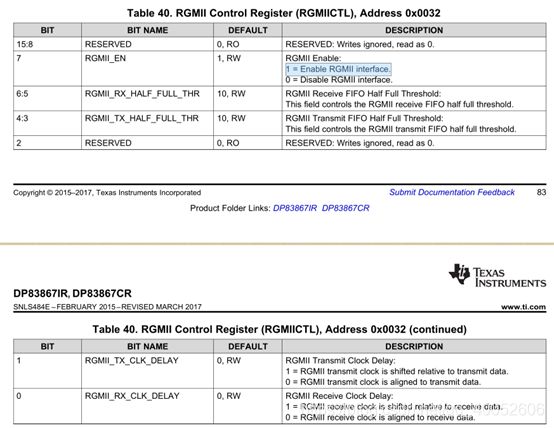

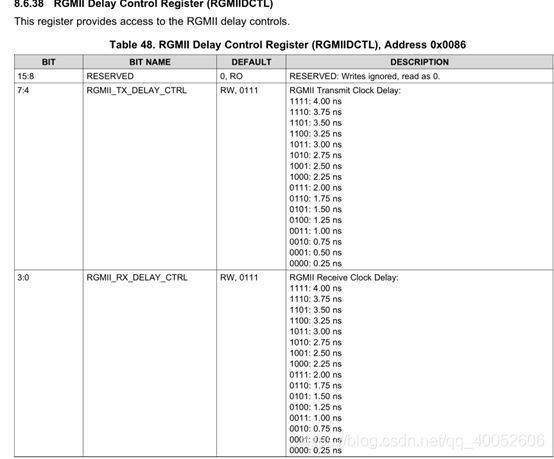

(3)regcr(0x000d)和addar(0x000e)配合使用间接寻址的方式对扩展寄存器集(地址高于0x001f)进行读/写访问。首先对regcr(0x000d)寄存器写入16’h001f,然后在addar(0x000e)寄存器写入要操作的扩展寄存器地址16’h0032,这样是选取寄存器地址为16’h0032,然后首先对regcr(0x000d)寄存器写入16’h401f,然后在addar(0x000e)寄存器写入要操作的扩展寄存器地址16’h0032的寄存器里面写入16’h00d3,这样实现了对寄存器地址为16’h0032写入16’h00d3的操作,这个操作是使能RGMII时钟和数据的偏移位置。同样的方式实现寄存器地址为16’h0086写入16’h0030的操,这个操作是调整RGMII时钟和数据的具体偏移时间的大小。

(4)最后对寄存器1F写入16’h0000,这样在配置完成寄存器后可以通过内外复位来实现PHY的复位操作。

上面寄存器初始化和网上查的资料是一样的,这里也可以主要对配置了PHY芯片进行速度的自适应、时钟和数据的上升下降沿的一个相对偏移位置。

3 UDP、ARP和ICMP代码

这部分代码分模块看没有什么问题,但是由于UDP、ARP、ICMP分属于不同的层级,在应用时需要符合网络数据传输的链路顺序来处理。而在底层代码上面这三个协议优先级是等价的,如果自己写与MAC

IP核功能相同的代码的话,可以把这三个协议同等对待,但由于采用的MAC IP核,这里在测试中就出现了一个很奇怪的现象就是ARP始终是通的,但ICMP确不通。

这里应当区分下这三个协议的响应应用逻辑。如果采用MAC

IP核的话需要对这三个协议响应逻辑进行处理。自己实现MAC IP核的话则需要根据代码进行应用的调整。

4 实际的测试

在前期分析的基础上重点对PHY核MAC IP核进出数据进行测试。测试流程如下图所示:

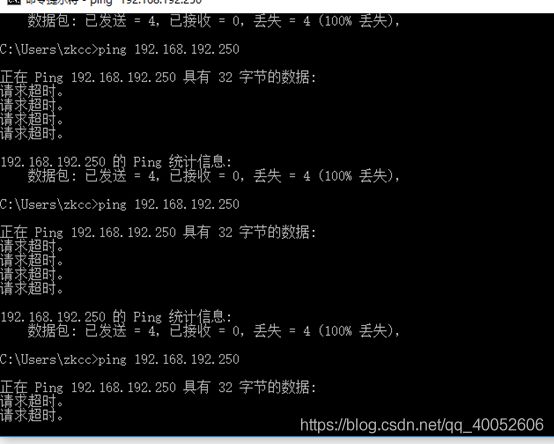

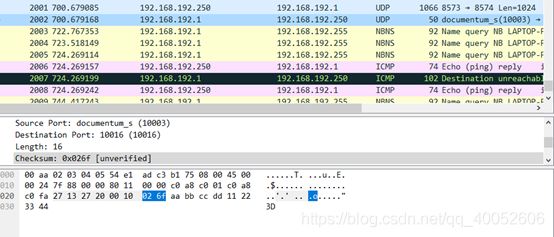

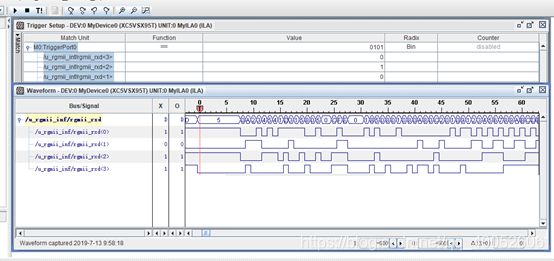

(1) 对板卡进行复位,然后通过ping来观察是否连通。在ping的同时观察wireshark和PHY芯片硬件输出数据,来判断PHY芯片输出数据是否正确。从图中CMD命令窗口可以看出ping超时但上位机发出来ICMP命令。从ChipScope数据的抓取可以看出数据通过PHY芯片正确的传输到FPGA引脚上,进入到MAC IP核,而FPGA中ICMP模块并没有收到正确的ICMP请求,那么数据就是在MAC IP核这里出了问题。

(2) 在ping超时的情况下ARP协议在一直是保持通畅的,上位机发出请求,下位机优ARP响应。

(3) 在ping超时的情况下通过上位机下发UDP包来测试UDP协议。通过网络调试助手和ChipScope数据的抓取对比发现,数据的传输是正常的。

5 总结

这次的测试主要是通过上位机下发数据对FPGA进行测试。

(1) 在测试中发现PHY芯片外围电压纹波较大,但目前不影响使用。

(2) 上位机无法通过下发数据与FPGA通信主要问题就是底层驱动代码存在问题,造上位机无法完成数据的下发。

(3) 对输入RGMII信号进行时序约束,通过输入输出OFFSET IN和OFFSET OUT使得信号和时钟对齐。

(4) 优化数据传输逻辑,尽量较少数据交互,减小数据发送量。

6 解决思路

(1) 重新对现有代码编写测试,并根据代码来对ARP、ICMP、UDP协议的管理和优化。(这种方法是代码完全自主可控,工作相对较大,需要一定的调试,只能针对特定的通信协议(比如RGMII协议),但无论在任何型号的FPGA上都可以不用修改的移植。

(2) 在原有的底层代码的基础上对MAC IP核进行重新配置(这种方法需要对IP核数据手册进行详读,并做一部分仿真测试,以后根据不同型号的FPGA选用相对于的IP核)。

(3) 对底层代码时序进行约束,根据ISE时序报告来对输入输出的时钟、控制和数据信号进行约束。

(4) 重新审查原理图和PCB观察差分线和数据线是否等长,阻抗匹配是否合适、静电防护芯片是否等效容值较大。