经过跟行业前辈的探讨和参考一些书籍,本文中的“个人理解”部分有误,即:

(个人理解:)在一个库中,尽管电路器件单元已经被综合映射,但是工具可以通过改变周围的环境来得到不同的单元延时,所以即使是同一个库,调用工艺参数不一样的情况下,其单元延时是不同的,因此就有了最快路径和最慢路径。 (这里有误)。

对于一个综合好的电路网表,在一个确定的pvt环境下(即只读入一个库的情况下)、约束好了端口的transition和load,那么电路网表中的某个器件的延时是唯一确定的(从库查表得到)。ovc模式下一个器件才有两个延时值。

因此下面的库分析(延时分析)过程中,存在认识错误,请读者们注意!!!以后我会专门写一篇文章来更正的。

学习数字设计(数字IC设计、FPGA设计)都必须学习静态时序分析(Static Timing Analysis ,STA)。然而静态时序时序分析是一个比较大的方向,涉及到的内容也比较多,如果要系统得学习,那得花费不少的心思。这里来记录一下关于静态时序分析的三种分析模式,这里的记录只是记录一下学习笔记,或者说是随笔,而不是系统地学习STA。本文是来自于前天遇到了一道静态时序分析的题目,感觉有点疑惑,于是发到群里请求解答。经过一番讨论、查找资料之后,真相渐渐露出水面。

先看一下题目:

一、时序路径分析模式及相关概念

1.最快路径和最慢路径

在求解这道题目之前,先来介绍一下时序路径分析模式及相关概念。

①最快路径(early- path):指在信号传播延时计算中调用最快工艺参数的路径;根据信号的分类可以分为最快时钟路径和最快数据路径。

②最慢路径(late path):指在信号传播延附计算中调用最慢工艺参数的路径;分为最慢时钟路径和最慢数据路径。

(个人理解:)在一个库中,尽管电路器件单元已经被综合映射,但是工具可以通过改变周围的环境来得到不同的单元延时,所以即使是同一个库,调用工艺参数不一样的情况下,其单元延时是不同的,因此就有了最快路径和最慢路径。(这里理解有误)

注意:

与数据路径不同,最快时钟路径、最慢时钟路径的选择在建立时间分析和保持时间分析中是不同的。

1)建立时间分析最快时钟路径和最慢时钟路径如下图所示:

在建立时间分析中,最快时钟路径是指时序路径中时钟信号从时钟源点到达终止点时序单元时钟端口的延时最短捕获时钟路径,而最慢时钟路径是指时序路径中时钟信号从时钟源点到达始发点时序单元时钟端口的延时最长发射时钟路径。

2)保持时间分析最快时钟路径和最慢时钟路径如下图所示:

在保持时间分析中,最快时钟路径是指时序路径中时钟信号从时钟源点到达达始发点时序单元时钟端口的延时最短发射时钟路径,而最慢时钟路径是指时序路径中时钟信号从时钟源点到终止点时序单元时钟端口的延时最长捕获时钟路径。

2.分析模式

静态时序分析工具提供3种分析模式进行静态时序分析,不同的设计需求通过选择对应的时序分析模式从而可以在合理的时序计算负荷范围内得到接近于实际工作的时序分析结果。这三种模式是:单一分析模式(single mode)、最好-最坏分析模式(BC-WC mode)、全芯片变化分析模式(OCV模式)。

我查阅了一些资料,在Synopsys公司的静态时序分析工具PrimeTime在早期的userguide中是有说明的,例如2010.06版本中:

但是在最近两三年的版本中,却忽略了BC_WC模式,变成了其他三种模式,比如2015.12版本中:

虽然在user guide中没有明确写出BC_WC模式,但是这种模式还是存在的,也就是还是可以使用这种模式的。

在Cadence的时序分析分析工具Encounter Timing System的2013.01的版本中,也是支持这三种分析模式的:

上面的工具默认的都是单一模式。回到题目中,查了一下,这道题目是5、6年前(甚至更早)的了,算是很经典的一道题目。很显然,题目要求的是在BC_WC模式先分析建立时间和保持时间。在求解题目之前,先来看一下这三种模式是如何分析建立时间和保持时间的。

对于PT的2010.06版本:

对于PT的2015.12版本:

可以看到,2015.12并没有给出WC-BC模式的描述,但是是支持的。

对于ETS:没有给出表格,但是和PT的差不多。

下面就来介绍这三种模式下是如何分析路径延时的,这里只进行介绍建立时间的分析,看情况介绍保持时间。

二、单一分析模式(工具默认的模式)

1.模式介绍

在该模式下,工具只会在指定的一种工作条件下检查建立时间和保持时间,该工作条件可能是最好的、典型的、最坏的中的一种,但只能是单一的一种,

![]()

而这里不进行配置:

![]()

(1)建立时间分析

对于触发器到触发器时序路径的建立时间的要求,转换成单一分析模式下建立时间的基本计算公式如下:

发送时钟最慢路径延时+最慢数据路径延时≤捕获时钟最快路径延时+时钟周期-终止点时序单元建立时间

进行建立时间检查时,始发点触发器的发射时钟路径延时、终止点触发器捕获时钟路径沿和从始发点到终止点的数据路径延时都是基于单一工作条件下所计算的路径延时。这是工作单一的一个库中,也就是工具在同一工艺进程、温度、电源下,调用其他不同的工艺参数,得到最快、最慢的时钟路径和数据路径。这是路径值是确定的。例如下面例子中(时间单位为ns):

假设上述电路是在典型库中进行综合的,那么在分析建立时间的时候,工具通过调用不同的工艺参数,得到最慢的发射时钟路径、最慢的数据路径和最快的捕获时钟路径:

时钟周期=4

发射时钟最慢延时 = U1+U2 = 0.8+0.6 = 1.4

最慢数据路径延时 =3.6

最快捕获时钟延时 = U1+U3 = 1.3

时序单元FF2的建立时间要求查库得到0.2

因此 :建立时间的slack为:

1.3 + 4-0.2 - 1.4 - 3.6 = 0.1

(2)保持时间分析

保持时间的计算思路是一样的,这里只给出保持时间需要满足的公式,不再举具体例子。单一模式下要满足的保持时间要求如下所示:

发射时钟最快路径延时 + 最快数据路径延时≥捕获时钟最慢路径延时 + 终止点时序单元保持时间

2.题目计算

对于前面的题目,由于题目的要求是在WC-BC模式下,但是假如是在单一模式,我们来看看该如何分析:

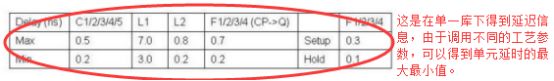

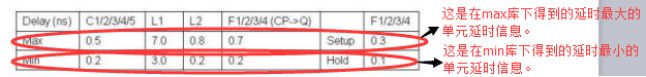

单一库下工具提取到延时信息的理解如下:

下面分析题目中的路径:

对于F1和F2之间的建立时间分析如下所示:

时钟周期 = 2*4 = 8

最慢发射时钟路径(延时) = C1max + C2max = 1

最慢数据路径 = F1cqmax+L1max = 0.7+7 = 7.7

最快捕获时钟路径 = C1min + C2min + C3min = 0.6

F2的D端口建立时间 = 0.3

因此建立时间slack 为 :

8 +0.6 - 0.3 - 1 - 7.7 = -0.4 (建立时间违规)

对于F1和F2之间的保持时间分析如下所示(题目没有要分析这条路径的保持时间):

最快发射时钟路径:C1min + C2min = 0.4

最快数据路径:F1cqmin+L1min = 3.2

最慢捕获时钟:C1max + C2max + C3max = 1.5

F2保持时间 = 0.1

因此保持时间slack为:

0.4+3.2 - 1.5 - 0.1 = 2

同理可以分析单一模式下F3-F4路径的保持时间:

最快发射时钟路径:C1min + C2min = 0.4

最快数据路径:F3cqmin + L2min = 0.4

最慢捕获时钟:C1max + C2max + C4max+C5max = 2

F2保持时间 = 0.1

因此保持时间slack为:

0.4 + 0.4 - 2 - 0.1 = -1.3(保持时间违规)

三、最好-最坏分析模式(BC-WC)

1.模式介绍

对于最好-最坏分析模式,静态时序分析工具会同时在PVT环境中的最好的和最坏的工作环境下检查建立时间和保持时间。也就是说,使用这个方式的时候,至少需要读入两个库(环境),一个用来设置最好的工作环境(或者说延时最小),一个用来设置最坏的工作环境(或者说延时最大)。

(1)建立时间分析

最好-最坏分析模式中建立时间的基本计算公式与单一分析模式下建立时间的基本计算公式一致,不同点在于计算建立时间所使用的工作环境不同,在计算建立时间过程中静态时序分析工具调用逻辑单元的最大(max)延时时序库,并用来检查时序路径最大延时是否满足触发器建立时间。

例如对下面电路进行建立时间分析:

时钟周期 = 4

发射时钟最慢路径延时(max库)=U1单元延时(max库)+U2单元延时(max库)=0.7+0.6=1.3

最慢数据路径延时(max库)=3.5

最快数据路径延时(max库) =1.9

捕获时钟最快路径延时值(max库) = U1单元延时(max库)+ U3单元延时(max库)=0.7+0.5=1.2

建立时间要求(max库) = 0.2

因此触发器之间路径的建立时间slack为:

1.2 + 4 - 0.2 -1.3 - 3.5 = 0.2

(2)保持时间分析

同样,最好-最坏路径分析模式中保持时间的基本计算公式与单一分析模式下保持时间的基本计算公式一致。不同点在于计算保持时间所使用的工作环境不同。在计算保持时间过程中,静态时序分析工具调用逻辑单元的最小(min)延时时序库,并用来检查时序路径最小延时是否满足触发器保持时间的约束。 即进行保持时间检查时,始发点触发器的发射时钟延时、终止点触发器捕获时钟延时和从始发点到终止点的数据路径延时都是基于最好工作条件下所计算的路径延延时

例如对下面电路进行保持时间分析:

时钟周期 = 4

发射时钟最快路径延时(min库)=U1单元延时(min库)+U2单元延时(min库)=0.5+0.4=0.9

最快数据路径延时(min库)=1

最慢数据路径延时(min库) =2.3

捕获时钟最慢路径延时值(min库) = U1单元延时(min库)+ U3单元延时(min库)=0.5+0.3=0.8

保持时间要求(min库) = 0.1

因此触发器之间路径的保持时间slack为:

0.9+1-0.8-0.1 = 1 (保持时间不违规)

2.题目计算

对于我们的题目,就是要求我们在BC-WC模式下进行分析建立时间和保持时间。现在就来分析一下。

首先我们分析工具提取到延时信息:

这里我们需要注意,本来我在读入max库的时候,应该有会得到max库下的单元延时的最大最小值;在读入min库的时候后,会得到min库下单元的最大最小值。题目中相当于只有一个库下单元延时的最大最小值,这个库取了max库的最大延时,同时取min库的最小延时。因此在进行WC分析的时候,我们就将max库中的单元延时最大和最小值看做相等进行处理,即max库中单元只有一个固定延时值(即上面的max列表里面)。同理BC分析的时候,min库中的单元也只有一个延时值(即上面的min列表里面)。

下面就对时序路径进行分析:

对于F1-F2路径的建立时间分析如下所示:

时钟周期 = 2*4 = 8

最慢发射时钟路径(max库) = C1max + C2max = 1

最慢数据路径(max库) = L1max = 7

最快捕获时钟路径(max库) = C1maxmin + C2maxmin + C3maxmin=C1max + C2max + C3max = 1.5 (maxmin表示max库下的最快路径)

F2的D端口建立时间 (max库)= 0.3

因此建立时间slack 为 :

8 +1.5 - 0.3 - 1 -0.7- 7 = 0.5

对F3-F4路径的保持时间分析如下所示:

最快发射时钟路径(min库):C1min + C2min = 0.4

最快数据路径(min库):F3cqmin + L2min = 0.4

最慢捕获时钟(min库):C1minmax + C2minmax + C4minmax+C5minmax =C1min + C2min + C4min+C5min=0.8 (minmax表示min库下的最慢路径)

F2保持时间 = 0.1

因此保持时间slack为:

0.4 + 0.4 - 0.8 - 0.1 = -0.1(保持时间违规)

四、OCV分析模式

在芯片变化相关工作模式下,与最好-最坏分析模式一样,静态时序分析工具也会同时在PVT境中的最好的和最坏的工作环境下检查建立时间和保持时间,也就是要读入两个库。

1.基本的OCV模式:

(1)建立时间的分析

OCV分析模式中建立时间的基本计算公式与其他分析模式下建立时间的基本计算公式一致,不同点在于计算最快路径和最慢路径所使用的工作环境不同,在计算建立时闻过程中静态时序分析工具调用时序单元的最大延时时序库来计算最慢路径的延时,同时调用逻辑单元的最小延时时序库来计算最快路径的延时,只检查时序路径的延时是否满足触发器建立时间的约束。

进行建立时间检查时。始发点触发器的发射时钟采用的是最坏条件下最慢时钟路径,终止点触发器的捕获时钟采用的是最好条件下最快时钟路径,而从始发点到终止点的数据路径的延时则是在最坏条件下最慢数据路径延时。

例如:

时钟周期 = 4

发射时钟最慢路径延时(max库)=U1单元延时(max库)+U2单元延时(max库)=0.7+0.6=1.3

最慢数据路径延时(max库)=3.5

捕获时钟最快路径延时值(min库) = U1单元延时(min库)+ U3单元延时(min库)=0.5+0.3=0.8

建立时间要求(max库) = 0.2

因此触发器之间路径的建立时间slack为:

0.8 + 4 - 0.2 -1.3 - 3.5 =- 0.2(时序违规)

·保持时间:类似,不进行详细描述

(2)题目计算

对于我们的题目,假设要在基本的OCV模式下进行计算,我们来看一下:

首先库的分析WC-BC模式一样,不重复说明:

然后对时序路径进行分析:

对于F1-F2路径的建立时间分析如下所示:

时钟周期 = 2*4 = 8

最慢发射时钟路径(max库) = C1max + C2max = 1

最慢数据路径(max库) = F1cqmax+L1max = 0.7+7 = 7.7

最快捕获时钟路径(min库) = C1min + C2min + C3min= 0.6

F2的D端口建立时间 = 0.3

因此建立时间slack 为 :

8 +0.6 - 0.3 - 1 -7.7= -0.4 (建立时间违例)

对F3-F4路径的保持时间分析如下所示:

最快发射时钟路径(min库):C1min + C2min = 0.4

最快数据路径(min库):F3cqmin + L2min = 0.4

最慢捕获时钟(max库):C1max + C2max + C4max+C5max =2

F2保持时间 = 0.1

因此保持时间slack为:

0.4 + 0.4 - 2 - 0.1 = -1.1(保持时间违规)

对于上面的题目,在基本的OCV模式中计算分析建立时间时,公共路径C1、C2在计算最慢发射时钟路径时,使用的是max库的最慢延时;而在计算最快捕获时钟路径的时候使用的是min库的最快延时。也就是说,该分析把公共路径的输出,当做两个不同传播延时的信号进行延时计算。然而在芯片实际工作时,公共路径的输出是一个信号驱动后续的发射时钟和捕获时钟,上面的检查分析太过于悲观,不太符合实际,因此延伸到下面两种模式。

2.考虑时序减免的OCV模式:

时序减免〔timing derate)的作用是很据减免(derating)系数,静态时序分析工具会在时序路径的每级逻辑门、连线和端口上都加上或减去一个原来延时值乘以减免系数值的延时作为最终的延时结果。设置时序减免值的目的是使时序分析结果更加符合实际情况。

使用这种方式需要设置derating系数,系数值需要通过实际工程经验总结出来,这里不进行深入探讨,而且题目中没有给出该系数,因此不进行深入介绍。

3.考虑时钟路径悲观移除(CPPR)的OCV模式:

可以分为 不考虑时序减免和考虑时序减免情况,这里不进行介绍,感兴趣可以参考有关资料。

其他先进的分析模式如AOVC、POCV等,涉及内容较多,就不写了,感兴趣可以参考有关资料。

参考资料:

《集成电路静态时序分析与建模》,刘峰,2016

《PrimeTime User Guide》,synopsys,2015

《PrimeTime Fundamentals User Guide》,synopsys,2010

《Encounter Timing System User Guide》,cadence,2013

![]()