Si基相控阵技术的相关进展

Si基相控阵技术的相关进展

-

- 一、技术背景

- 二、设计考虑

-

- 2.1模块化扩展(phased-array scaling)

- 2.2 封装挑战

- 2.3 波束控制

- 2.4 校准

- 2.5 电磁仿真

- 三、简要回顾(2014-2019)

- 四、发展趋势

-

- 4.1 更高EIRP

- 4.2 宽带波束合成

- 4.3 多功能与3D感知应用

- 4.4 高效散热

- 4.5 软件定义相控阵列

一、技术背景

最近这些年基于硅基工艺(主要是Si CMOS 和SiGe BiCMOS)实现的SOC(System on Chip)以及AiP(Antenna in Package)封装技术得到了长足的发展,使得相控阵技术相关产品能够实现低成本和大批量生产,因此有可能在5G毫米波通信、低轨卫星互联网等民用产品中广泛使用。

调研过程中翻到一篇不错的综述文献1,来自IBM的T. J. Watson Research Center,属于该技术领域顶级的研究团队(原文献)。后面将简要记录下几个主要的设计考虑因素包括:模块化扩展、封装挑战、波束控制、校准、电磁仿真,并进一步回顾下该技术短暂的历史,最后给出对未来研究趋势的探讨。

正如这篇文章名字所示“The More (Antennas), the Merrier: A Survey of Silicon-Based mm-Wave Phased Arrays Using Multi-IC Scaling”,拥有更多天线单元的大型阵列越来越受到关注。原因在于对于收发系统的两个核心指标:发射EIRP和接收SNR,通过增加阵列单元数量N,理论上二者能够分别得到N^2和N倍的增益。同时大型阵列所提供的窄波束及空域滤波能力对于通信而言同样不可忽略。

与化合物半导体相比,Si基集成的射频性能无论在发射功率还是低噪声性能上都没有明显的优势,特别是发射功率单通道饱和输出能力及其有限,就更需要阵列增益来进行系统能力的扩展。这也就引出了本文主要介绍的技术路径,模块化扩展“phased-array scaling”(根据自己理解起了个名字,直译应该是相控阵缩放)。

二、设计考虑

2.1模块化扩展(phased-array scaling)

大规模的硅基相控阵IC芯片虽然有很多优势,但其设计面临极大的挑战。

图1 单IC集成通道数量发展趋势1

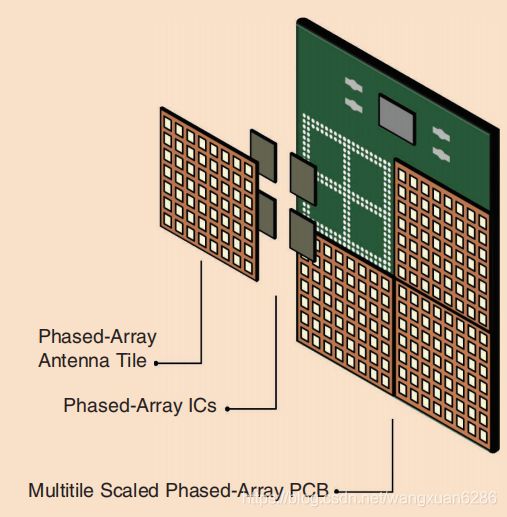

如图1所示,由于目前最高水准的集成只能做到单IC集成64通道,因此需要模块化扩展(phased-array scaling)来构成所需要的更大阵列。如图2,大概意思就是几片多通道IC与AiP封装构成小模块,很多小模块再装配到多层PCB(printed circuit board)载板上。这种集成方式在良率(Yield)、成本(Cost)、测试(Testing)及灵活性(Flexibility)上的优势使其成为主流,被绝大多数多头部研究团队所采用。

图2 单IC集成通道数量发展趋势1

使用这种扩展技术需要考虑整个阵列功能在IC间的分配、本振及时钟源分配和相关的同步问题。

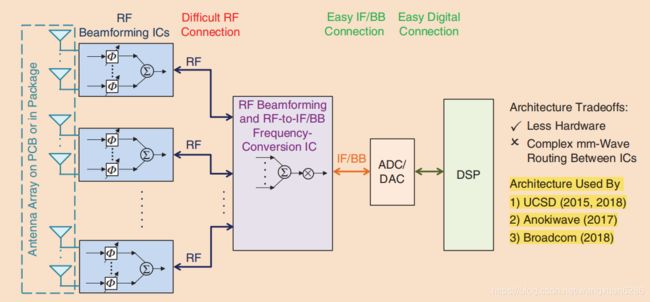

波束成形可以在RF、LO、IF及数字域进行,而Si基相控阵研究大多采用RF即模拟波束合成或混合波束合成方式,这样片上电路数量较少。RF波束合成架构的主要功能模块包括:模拟波束合成、频率变换、模数转换及数字信号处理。不同架构可以选择将不同功能进行IC集成,比如将模拟波束合成和频率变换进行IC集成,IC输入RF信号输出IF信号,就可以减少工作于毫米波的板间或电缆互联,从而减低成本。这种方案被IBM、Qualcomm、Nokia Bell Labs、and Intel等公司采用。而由此带来的问题是需要处理频率变换所需的本振分配网络和本振同步问题。

图3 RF连接困难的功能划分1

图4 RF波束合成与模拟变频集成的功能划分1

波束合成的基本要求是相位或时延匹配,而LO分配是相位误差的来源之一。在硅基阵列中,通常采用较低频率的参考信号在不同IC芯片间进行同步分配,再在IC内部进行倍频或利用锁相环产生所需的毫米波本振信号。这种同步会有温度和时间漂移,从而导致不同IC无法相干合成,因此通常都需要进行IC间和模块间的校准。校准应该是核心技术之一,这在后面专门介绍。这里涉及到的是IC上到底是选择倍频方案还是锁相环方案产生本振信号,文中给出的是用倍频方案,但其给出的分析我却有所疑惑,留两篇参考文献2在此3,后面看明白再补上。

2.2 封装挑战

首先需要考虑的是集成封装方案,Si基相控阵IC与天线集成有如图5所示的三种方式可选择:(a)On-PCB;(b)In-Package;(c)On-Wafer。

图5 与天线集成的三种技术路径1

第一种方法直接在PCB上集成天线(On-PCB),这种成本最低。 相控阵芯片可以是裸芯片,也可以预先封装在芯片级模块中,通过倒装焊、键合或球栅阵列(BGA)表贴到PCB天线阵辐射方向相反的一侧上。由于制造工艺和公差限制,这种方法的挑战包括高增益高效率天线,解决天线、电路电源布板的工艺限制。

第二种在第一级封装上安装天线,该封装与倒装芯片结合的IC一起形成了一个单元瓦片模块(In-Package)。通过BGA将模块连接到二级PCB,以形成更大的阵列。根据应用的不同,有许多基板技术(LTCC等)可用于实现带有嵌入式天线的封装。 AiP方法以复杂性为代价提供了模块级设计和测试灵活性,是目前最流行的集成方法。

第三种直接在晶圆上安装天线(On-Wafer)。比如将包含金属贴片天线的玻璃(石英)基板堆叠在芯片上4。 该方式挑战在于提高良率(如堆叠成功率),克服热机械可靠性问题(如热膨胀系数不匹配),以及解决互连性能。

其次要考虑的是布阵问题,本质上与传统相控阵面临的问题和处理方法基本相同。由于单元间距以波长为变量,而相控阵IC的尺寸相对固定,因此在微波和毫米波低端,阵列天线与相控阵IC的封装较简单也很容易进行模块化扩展,而当工作频率扩展到毫米波高端后模块化集成和扩展就面临比较大的挑战。比如28GHz的相控阵,能够轻松地将双极化收发IC与天线集成。 但对于94GHz和60GHz系统则无法在天线阵列的封装区域内容纳双极化TR收发功能。

可以将传统相控阵领域的一些方法引入来折衷这一问题:引入虚拟天线单元来扩大天线阵面的面积,并通过填充系数来衡量,由此带来的问题是组成大阵时会产生栅瓣;另一种方法是先进行一级天线合成,导致的问题是扫描角度下降。另外还有采用稀疏布阵等。

此外要考虑的是散热,图5所示封装同样实现了散热结构,IC的一侧完成与天线的互联,而另一侧可通过与散热器连接进行散热。相关研究的功率密度如图6所示,大概在1-22W/cm^2左右。相比于CPU/GPU等属于小儿科,所以应该采用成熟的商用散热方式(风冷、液冷等)。

2.3 波束控制

硅基相控阵最显着的优势之一就是集成了数百万个数字控制晶体管。 几乎所有商用的基于Si的相控阵都使用片上光束表。 一个典型的基于静态随机存取存储器(SRAM)的波束表把每一个波束状态存为一行配置,配置主要包括每个通道移相器和衰减器的控制状态,然后通过SPI在不同配置行间切换。如图7(a)所示。不同IC的独立控制通过地址位和总线寻址完成。

对于高速数字控制,保持时钟和IC中数据I / O的所需输入阻抗也很重要。对于穿行和并行两种方式图7(b),穿行前后驱动比较容易但会导致延时;而并行虽然解决了延时问题,但对于高速信号而言,阻抗问题可能会降低信号完整性。所以大型阵列通常选择二者的组合。此外数字模拟的电磁兼容也需要通过电源隔离和地隔离来给予考虑。

2.4 校准

大型相控阵实现幅相匹配很具有挑战性,不同好在从统计学角度控制均值和方差即可使失配控制在一定程度。需要控制的失配来源很多,除了天线本身,还包括进出IC的各种通路(例如,天线馈源,基带(BB)/ IF / RF,I / O和LO)。 此外,还需要减少天线之间的耦合,以减少元件之间的失配(可用技术包括虚拟阵元,接地环,屏蔽,地孔等)。

波束形成对幅相一致的要求更高,对于两个重要的波束形成功能:波束控制和旁瓣抑制。这两个功能分别对应移相和幅度加权,理想情况下二者的控制需要相互独立,互不影响(文中用词正交orthogonal),以保证波束扫描时仍能保持旁瓣抑制,而旁瓣抑制时仍能保持波束控制。而实际上对于独立的器件移相器在不同移相状态下,插入损耗是会变化的,因此这个正交性需要通过校准和设计来实现。考虑到温度和电磁兼容因素,整个校准过程会比较复杂,对相关算法和校准环境的要求也很高。

而实际上,通过文献5中64单元能够实现±50°扫描和相对20dBc幅度加权的可缩放阵列验证。通过幅相匹配和正交幅相控制设计能够不需要阵列校准(calibration-free 这个待我仔细研究下)。如果需要校准可采用互耦技术实现在线闭环校准(over-the-air loopback calibration),如文献6。

2.5 电磁仿真

数值电磁仿真在设计和验证Si基毫米波相控阵天线的每个步骤中都起着至关重要的作用。仿真和建模需要在多个层级进行:1)单个天线与互联馈电; 2)天线阵列封装,以及3)阵列级仿真。

对于第一层级的仿真:单个天线元件的仿真根据基板材料和工艺规则优化单元天线设计。同时模型还用于确定层堆叠,以支持整个集成方案所需的必要互联设计(RF,IF,LO和数字信号)。从单元天线仿真获得的关键天线参数包括频率匹配带宽,跨频增益,天线效率和辐射方向图。

对于第二层级的仿真:整个天线阵列瓦片封装的EM仿虽然是可行的,但计算量大得多。它通常用于测量数据的布局后验证和交叉检查。

对于第三层级的仿真:对于由多个模块组成的较大相控阵,如果考虑所有参数,从EM仿真建模和计算角度都不切实际。 可以采用域分解方法高度精确地模拟较大的有限阵列孔径。 另外天线阵列的分析通常采用解析公式,其中天线被视为各向同性辐射器。还可以进行的另一种数值近似方法将模块封装EM解决方案复制为一个封装单元以形成更大的阵列。

三、简要回顾(2014-2019)

要深入理解一项技术的好办法是了解其发展历史,幸好Si基相控阵技术的历史不算很长,以频率(大于28GHz毫米波)、天线单元数(至少大于64单元)、和Si基集成工艺(SiGe BiCMOS and CMOS)为标准,以经过同行审议的公开文献为标记,该技术的开山之作为发表于2014年的7,该研究可以说为后续的相关研究提供了一个模板。(文中是这么说的,不过不知有没有自夸之嫌?)

如图8和图9所示,后面开启了各大研究机构的你追我赶,不断在集成通道数量、EIRP、填充系数(fill factor,有源通道/天线单元总数量-包含虚元)以及功能集成密度(主要指收发功能和任意极化控制功能)(integration density)等核心指标上打破记录。不过到本文发表为止,还没有关于全双工多IC相控阵列的发表工作(双工的问题还是比较困难)。

图8 不同研究机构的相关报道1

图9 集成密度(上)和集成单元数(下)的相关数据1

更详细的比较在下图10中给出。(没有基础工艺,这些个研究成果还真是渴望而不可及…)

图10 详细的结果比较1

四、发展趋势

在过去的五年中,基于硅的可扩展毫米波相控阵已从研究挑战发展为商业应用,而且还在进一步向更广阔的应用发展。文中指明:更高EIRP,宽带波束合成,多功能与3D感知应用,高效散热以及软件定义阵列是需要进一步研究的技术方向。

4.1 更高EIRP

当前方案硅基IC的集成规模能够满足短距离移动通信的需求。如果要扩大覆盖范围,就需要提高阵列的EIRP性能(增加天线单元数量或更高功率放大器)。前面说了目前Si集成放大器的输出功率有限,大概在20dBm以下,而化合物半导体放大器的输出功率更高,不过从集成方式来说可能需要完全不同的集成工艺,比如异质集成。所以到底是选择增加天线数量还是采用其它工艺放大器可能需要进一步的研究支撑。

4.2 宽带波束合成

无线通信有对更高速率的要求,对应相控阵系统更大的瞬时带宽。而相移技术基于窄带假设,当用于宽带系统时,会出现波束倾斜和阵列码间串扰(类似孔径渡越),这时需要用时延来代替相移。而相移与时延最主要的区别是相移可以周期循环,而时延不行,因此可能需要很多位来实现大型阵列的波束合成,这将给IC集成带来一定的挑战,如何将硅基相控阵扩展到硅基时延阵列是需要进一步研究的方向。

4.3 多功能与3D感知应用

自动驾驶汽车需要的3D感知推动了传感器技术的发展。目前基于光的激光雷达技术得到广泛的关注和投资,但全天候的感知系统可能仍需要依赖毫米波系统,低成本的硅基相控阵提供了一条可行途径。可以通过更多数量的天线单元提高角分辨率和范围,通过更大的信号带宽来提高范围分辨率。通信应用与3D感知雷达应用对相控阵有相同的技术需求,因此可以相互促进。

4.4 高效散热

散热对于阵列来说也是需要考虑的问题。实现高效散热和一体化集成所需要的研究方向包括:1)关于更高效波束合成的电路级研究; 2)能够兼容当前Si基及化合物半导体阵列集成工艺的新型散热方案 ,3)结合散热和电气性能的多物理场仿真。

4.5 软件定义相控阵列

最后比较重要的一点是,相控阵系统硬件还需要同软件结合才能构成最终的应用系统。可以将软件无线电的思想扩展到相控阵系统,这需要在(1)射频-数字联合设计来实现可配置和适应性;(2)大规模阵列的捷变波束控制以及(3)集成的控制软件界面。(好吧,这部分我没看懂)。

个人感觉下面的这些发展需求目前看都不是很迫切,写的也不是很明确,最开始怀疑作者大概率是为了凑篇幅。不过对于3D感知应用、软件定义阵列8、集成方面9确实看到了该团队后续的研究报道。

B. Sadhu, X. Gu and A. Valdes-Garcia, “The More (Antennas), the Merrier: A Survey of Silicon-Based mm-Wave Phased Arrays Using Multi-IC Scaling,” in IEEE Microwave Magazine, vol. 20, no. 12, pp. 32-50, Dec. 2019. ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎ ↩︎

T. Höhne and V. Ranki, “Phase Noise in Beamforming,” in IEEE Transactions on Wireless Communications, vol. 9, no. 12, pp. 3682-3689, December 2010. ↩︎

A. Puglielli, G. LaCaille, A. M. Niknejad, G. Wright, B. Nikolić and E. Alon, “Phase noise scaling and tracking in OFDM multi-user beamforming arrays,” 2016 IEEE International Conference on Communications (ICC), Kuala Lumpur, 2016, pp. 1-6. ↩︎

S. Zihir, O. D. Gurbuz, A. Kar-Roy, S. Raman and G. M. Rebeiz, “60-GHz 64- and 256-Elements Wafer-Scale Phased-Array Transmitters Using Full-Reticle and Subreticle Stitching Techniques,” in IEEE Transactions on Microwave Theory and Techniques, vol. 64, no. 12, pp. 4701-4719, Dec. 2016. ↩︎

B. Sadhu et al., “A 28-GHz 32-Element TRX Phased-Array IC With Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications,” in IEEE Journal of Solid-State Circuits, vol. 52, no. 12, pp. 3373-3391, Dec. 2017. ↩︎

S. Shahramian, M. J. Holyoak, A. Singh and Y. Baeyens, “A Fully Integrated 384-Element, 16-Tile, W W W -Band Phased Array With Self-Alignment and Self-Test,” in IEEE Journal of Solid-State Circuits, vol. 54, no. 9, pp. 2419-2434, Sept. 2019. ↩︎

X. Gu et al., “A compact 4-chip package with 64 embedded dual-polarization antennas for W-band phased-array transceivers,” 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, 2014, pp. 1272-1277. ↩︎

A. Valdes-Garcia, A. Paidimarri and B. Sadhu, “Hardware-Software Co-integration for Configurable 5G mmWave Systems,” 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 2020, pp. 1-2. ↩︎

X. Gu, D. Liu and B. Sadhu, “Packaging and Antenna Integration for Silicon-Based Millimeter-Wave Phased Arrays: 5G and Beyond,” in IEEE Journal of Microwaves, vol. 1, no. 1, pp. 123-134, winter 2021. ↩︎