【原创】流水线处理对比实例

一、引言

本文以8输入与门为例,展示在 Vivado 下对 纯8输入与门的组合逻辑链 和 两级流水线处理后的8输入与门 的静态时序分析(STA)报告,来直观地体现流水线技术在数字设计中的重要性。

二、纯8输入与门组合逻辑链

Verilog代码如下:

`timescale 1ns / 1ns

module test (

input clk , // Clock

input rst_n, // Asynchronous reset active low

input a ,

input b ,

input c ,

input d ,

input e ,

input f ,

input g ,

input h ,

output reg out

);

reg a_ff;

reg b_ff;

reg c_ff;

reg d_ff;

reg e_ff;

reg f_ff;

reg g_ff;

reg h_ff;

// 源寄存器

always@(posedge clk or negedge rst_n) begin

if(!rst_n)begin

a_ff <= 1'b0;

b_ff <= 1'b0;

c_ff <= 1'b0;

d_ff <= 1'b0;

e_ff <= 1'b0;

f_ff <= 1'b0;

g_ff <= 1'b0;

h_ff <= 1'b0;

end

else begin

a_ff <= a;

b_ff <= b;

c_ff <= c;

d_ff <= d;

e_ff <= e;

f_ff <= f;

g_ff <= g;

h_ff <= h;

end

end

// 目的寄存器

always@(posedge clk or negedge rst_n) begin

if(!rst_n)begin

out <= 1'b0;

end

else begin

out <= ( (a_ff&b_ff) & (c_ff&d_ff) ) & ( (e_ff&f_ff) & (g_ff&h_ff) );

end

end

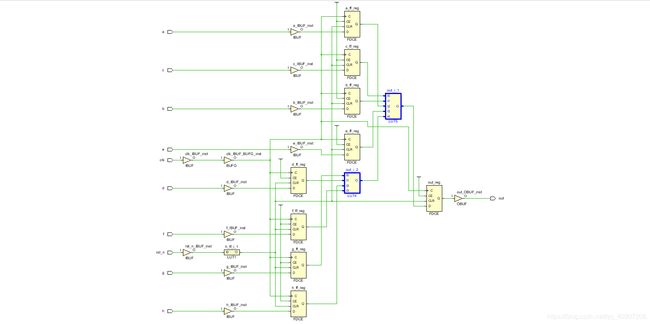

endmodule代码综合后的 RTL 图如下所示。

可见标蓝框的两个方框就是由两级 LUT 构成的8输入与门、左半面八个 ff_reg 是数据通路的源寄存器、右面一个 out_reg 是目的寄存器。

在 .xdc 文件中对电路进行位置约束和时序约束 ,其中时序约束仅需要进行主时钟约束,主时钟约束的 Tcl 命令如下。经过测试,选用 2GHz 的工作频率对电路进行静态时序分析。

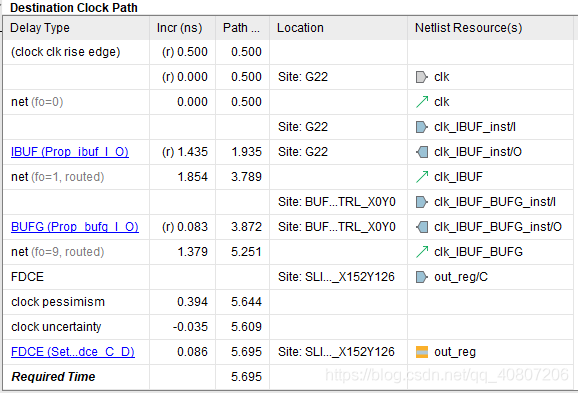

create_clock -period 0.500 -name clk -waveform {0.000 0.250} [get_ports clk]时序报告如下所示。可以发现在2GHz工作频率下,在一些关键路径的苛刻条件模型下仍是存在了 setup 时序违例。

由下图可见 ,Vivado 对目的时钟路径做了走线延迟加大的处理来试图增加 setup slack ,但在 2GHz 的高频率下也无能为力。

三、两级流水线处理

流水线技术就是打断长组合逻辑链,在组合逻辑链中插入寄存器缓存中间数据,以减小触发器间的组合链延迟,可以有效解决 setup 时序违例的问题。

本文在每个与门后插入一个触发器,即使用两级流水线对8输入与门进行处理。

Verilog代码如下:

`timescale 1ns/1ns

module pipeline (

input clk , // Clock

input rst_n, // Asynchronous reset active low

input a ,

input b ,

input c ,

input d ,

input e ,

input f ,

input g ,

input h ,

output reg out

);

reg ff_ab;

reg ff_cd;

reg ff_ef;

reg ff_gh;

reg ff_u ;

reg ff_d ;

// 第一级流水线

always @(posedge clk or negedge rst_n) begin

if ( rst_n == 1'b0 ) begin

ff_ab <= 1'b0;

ff_cd <= 1'b0;

ff_ef <= 1'b0;

ff_gh <= 1'b0;

end

else begin

ff_ab <= a & b;

ff_cd <= c & d;

ff_ef <= e & f;

ff_gh <= g & h;

end

end

// 第二级流水线

always @(posedge clk or negedge rst_n) begin

if ( rst_n == 1'b0 ) begin

ff_u <= 1'b0;

ff_d <= 1'b0;

out <= 1'b0;

end

else begin

ff_u <= ff_ab & ff_cd;

ff_d <= ff_ef & ff_gh;

out <= ff_u & ff_d;

end

end

endmodule代码综合后的 RTL 图如下所示。

可见,原来触发器间的两级 LUT 被拆分成一级 LUT ,触发器间的组合链缩短了。

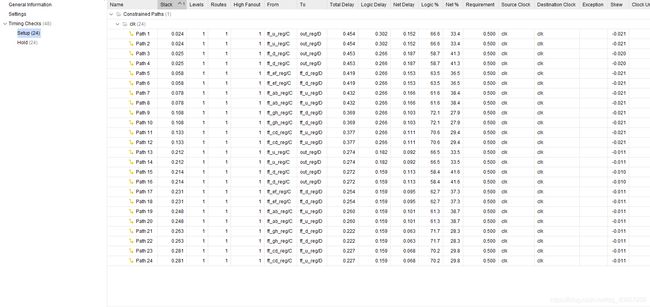

时序报告如下所示。在相同工作频率下已经没有 setup 违例的现象了,说明最大工作频率得到了提高。这也就表明了流水线技术从提高电路最大工作频率的方向上来提高电路的吞吐率。

四、功能验证

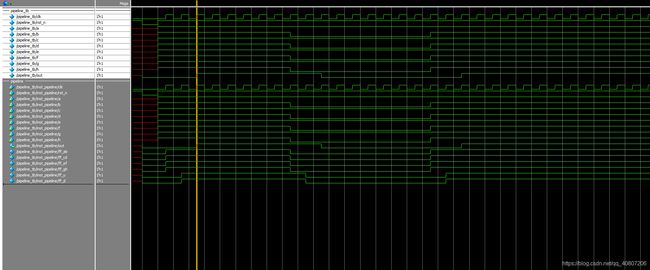

使用 Modelsim 验证两级流水线8输入与门的逻辑功能。

仿真结果如下图所示,可见8个输入全部置位后经过两个时钟周期的延时后输出了正确的结果,并且之后的逻辑结果不需要再等待两个时钟的延迟。