CPU处理器:

计算机的大脑就是CPU,它从内存中取指令->解码->执行,然后再取指->解码->执行下一条指令,周而复始,直至整个程序被执行完成。

每个CPU都有一套可执行的专门指令集,任何软件的执行最终都要转化成CPU的指令去执行。所以Pentium(英特尔第五代x86架构的微处理器)不能执行SPARC(另外一种处理器)的程序。

因访问内存以得到指令或数据的时间比CPU执行指令花费的时间要长得多,所以,所有CPU内部都有一些用来保存关键变量和临时数据的寄存器,这样通常在CPU的指令集中专门提供一些指令,用来将一个字(可以理解为数据)从内存调入寄存器,以及将一个字从寄存器存入内存。CPU其他的指令集可以把来自寄存器、内存的操作数据组合,或者用两者产生一个结果,比如将两个字相加并把结果存在寄存器或内存中。

寄存器的分类

除了用来保存变量和临时结果的通用寄存器外,多数计算机还有一些对程序可见的专门寄存器,其中之一便是程序计数器,它保存了将要取出的下一条指令的内存地址。在指令取出后,程序计算器就被更新以便执行后期的指令

另外一个寄存器便是堆栈指针,它指向内存中当前栈的顶端。该栈包含已经进入但是还没有退出的每个过程中的一个框架。在一个过程的堆栈框架中保存了有关的输入参数、局部变量以及那些没有保存在寄存器中的临时变量

最后 一个非常重要的寄存器就是程序状态字寄存器(Program Status Word,PSW),这个寄存器包含了条码位(由比较指令设置)、CPU优先级、模式(用户态或内核态),以及各种其他控制位。用户通常读入整个PSW,但是只对其中少量的字段写入。在系统调用和I/O中,PSW非常非常非常非常非常非常重要

寄存器的维护

操作系统必须知晓所有的寄存器。在时间多路复用的CPU中,操作系统会经常中止正在运行的某个程序并启动(或再次启动)另一个程序。每次停止一个运行着的程序时,操作系统必须保存所有的寄存器,这样在稍后该程序被再次运行时,可以把这些寄存器重新装入。

内核态与用户态

除了在嵌入式系统中的非常简答的CPU之外,多数CPU都有两种模式,即内核态与用户态。

通常,PSW中有一个二进制位控制这两种模式。

内核态:当CPU在内核态运行时,CPU可以执行指令集中所有的指令,很明显,所有的指令中包含了使用硬件的所有功能,(操作系统在内核态下运行,从而可以访问整个硬件)

用户态:用户程序在用户态下运行,仅仅只能执行CPU整个指令集的一个子集,该子集中不包含操作硬件功能的部分,因此,一般情况下,在用户态中有关I/O和内存保护(操作系统占用的内存是受保护的,不能被别的程序占用),当然,在用户态下,将PSW中的模式设置成内核态也是禁止的。

多线程和多核芯片

摩尔定律指出,芯片中的晶体管数量每18个月翻一倍,随着晶体管数量的增多,更强大的功能称为了可能,如

I.第一步增强:在CPU芯片中加入更大的缓存,一级缓存L1,用和CPU相同的材质制成,CPU访问它没有时延

II.第二步增强:一个CPU中的处理逻辑增多,intel公司首次提出,称为多线程(multithreading)或超线程(hyperthreading),对用户来说一个有两个线程的CPU就相当于两个CPU,我们后面要学习的进程和线程的知识就起源于这里,进程是资源单位而线程才是CPU的执行单位。

多线程运行CPU保持两个不同的线程状态,可以在纳秒级的时间内来回切换,速度快到你看到的结果是并发的,伪并行的,然而多线程不提供真正的并行处理,一个CPU同一时刻只能处理一个进程(一个进程中至少一个线程)

III.第三步增强:除了多线程,还出现了傲寒2个或者4个完整处理器的CPU芯片,如下图。要使用这类多核芯片肯定需要有多处理操作系统

存储器

存储器有许多种类,按照存储速度由高到低排名:寄存器->高速缓存->内存->固态硬盘->磁盘->磁带。

寄存器:

即L1缓存,与CPU相同材质制造,速度一样快,因而CPU访问它无时延。

高速缓存:

即L2、L3缓存,二级缓存是CPU性能表现的关键之一,在CPU核心不变化的情况下,增加二级缓存容量能使性能大幅度提高。而同一核心的CPU高低端之分往往也是在二级缓存上有差异,由此可见二级缓存对于CPU的重要性。

CPU在缓存中找到有用的数据被称为命中,当缓存中没有CPU所需的数据时(这时称为未命中),CPU才访问内存。从理论上讲,在一颗拥有二级缓存的CPU中,读取一级缓存的命中率为80%。也就是说CPU一级缓存中找到的有用数据占数据总量的80%,剩下的20%从二级缓存中读取。由于不能准确预测将要执行的数据,读取二级缓存的命中率也在80%左右(从二级缓存读到有用的数据占总数据的16%)。那么还有的数据就不得不从内存调用,但这已经是一个相当小的比例了。目前的较高端的CPU中,还会带有三级缓存,它是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

主存:

再往下一层是主存,此乃存储器系统的主力,主存通常称为随机访问存储RAM,就是我们通常所说的内存,容量一直在不断攀升,所有不能在高速缓存中找到的,都会到主存中找,主存是易失性存储,断电后数据全部消失。

非易失性随机访问存储:

除了主存RAM之外,许多计算机已经在使用少量的非易失性随机访问存储如ROM(Read Only Memory,ROM),在电源切断之后,非易失性存储的内容并不会丢失,ROM只读存储器在工厂中就被编程完毕,然后再也不能修改。ROM速度快且便宜,在有些计算机中,用于启动计算机的引导加载模块就存放在ROM中,另外一些I/O卡也采用ROM处理底层设备的控制。

EEPROM(Electrically Erasable PROM,电可擦除可编程ROM)和闪存(flash memory)也是非易失性的,但是与ROM相反,他们可以擦除和重写。不过重写时花费的时间比写入RAM要多。在便携式电子设备中中,闪存通常作为存储媒介。闪存是数码相机中的胶卷,是便携式音译播放器的磁盘,还应用于固态硬盘。闪存在速度上介于RAM和磁盘之间,但与磁盘不同的是,闪存擦除的次数过多,就被磨损了。

CMOS:

还有一类存储器就是CMOS,它是易失性的,许多计算机利用CMOS存储器来保持当前时间和日期。CMOS存储器和递增时间的电路由一小块电池驱动,所以,即使计算机没有加电,时间也仍然可以正确地更新,除此之外CMOS还可以保存配置的参数,比如,哪一个是启动磁盘等,之所以采用CMOS是因为它耗电非常少,一块工厂原装电池往往能使用若干年,但是当电池失效时,相关的配置和时间等都将丢失。

磁盘:

磁盘低速的原因是因为它一种机械装置,在磁盘中有一个或多个金属盘片,它们以5400,7200或10800rpm(RPM =revolutions per minute 每分钟多少转 )的速度旋转。从边缘开始有一个机械臂悬在盘面上,这类似于老式黑胶唱片机上的拾音臂。信息写在磁盘上的一些列的同心圆上,是一连串的2进制位(称为bit位),为了统计方法,8个bit称为一个字节bytes,1024bytes=1k,1024k=1M,1024M=1G,所以我们平时所说的磁盘容量最终指的就是磁盘能写多少个2进制位。

每个磁头可以读取一段换新区域,称为磁道, 把一个戈丁手臂位置上所以的磁道合起来,组成一个柱面,每个磁道划成若干扇区,扇区典型的值是512字节。数据都存放于一段一段的扇区,即磁道这个圆圈的一小段圆圈,从磁盘读取一段数据需要经历寻道时间和延迟时间。

虚拟内存:

许多计算机支持虚拟内存机制,该机制使计算机可以运行大于物理内存的程序,方法是将正在使用的程序放入内存取执行,而暂时不需要执行的程序放到磁盘的某块地方,这块地方成为虚拟内存,在linux中成为swap,这种机制的核心在于快速地映射内存地址,由CPU中的一个部件负责,成为存储器管理单元(Memory Management Unit MMU)

磁带:

价钱相同的情况下比硬盘拥有更高的存储容量,虽然速度低于磁盘,但是因其大容量,在地震水灾火灾时可移动性强等特性,常被用来做备份。(常见于大型数据库系统中)

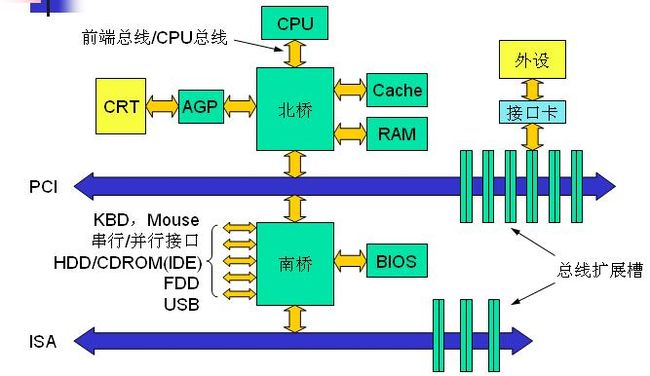

总线

北桥,南桥是主板上芯片组中最重要的两块了。相对的来讲,北桥要比南桥更加重要。北桥连接系统总线,担负着 CPU访问内存的重任。同时连接这AGP插口,控制PCI总线,割断了系统总线和局部总线,在这一段上速度是最快的。南桥不和CPU连接通常用来作I/O 和IDE设备的控制。所以速度比较慢,一般情况下,南桥和北桥中间是PCI总线。