基于fpga的ov7670摄像头采集及实时显示_「学术论文」基于深度学习的实时识别硬件系统框架设计...

摘要:

设计了一种基于深度学习的实时识别硬件系统框架。该系统框架使用Keras完成卷积神经网络模型的训练并提取出网络的参数,利用ZYNQ器件的FPGA+ARM软硬件协同的方式,使用ARM完成对实时图像数据的采集、预处理及显示,通过FPGA实现卷积神经网络的硬化并对图像进行识别,再将识别结果发送至上位机进行实时显示。系统框架采用MNIST和Fashion MNIST数据集作为网络模型硬化试验样本,实验结果表明,在一般场景下该系统框架能够实时、准确地完成图像数据的获取、显示及识别,并且具有可移植性高、处理速度快、功耗低的特点。

中文引用格式:王昆,周骅. 基于深度学习的实时识别硬件系统框架设计[J].电子技术应用,2018,44(10):11-14.

英文引用格式:Wang Kun,Zhou Hua. Design of real-time recognition hardware system framework based on deep learning[J]. Application of Electronic Technique,2018,44(10):11-14.

❖

0 引言

近年来随着深度学习的迅速发展[1-3],卷积神经网络(Convolutional Neural Network)被广泛使用[4-5],特别是在图像识别场景中的应用[6-7]。为满足更多场景应用,需要设计出一种能够根据实际场景需求可替换不同CNN网络模型的系统框架。虽然CNN的使用广泛,但是目前应用CNN的硬件平台主要是通过普通处理器CPU来实现的[8-9],其电路架构并不适合作为CNN实现的计算平台,因为CNN当中的模型结构,其内部的每层卷积运算都只与当前卷积层的卷积核相关,与其他层的运算是互相独立的,所以CNN的结构是一种并行的,使得CPU整体的计算效率较低。而现场可编程门阵列(FPGA)作为一种高度密集型计算加速器件,具有可重配置特性,利用硬件描述语言完成相关结构设计实现,因此可使用FPGA的硬件结构特性实现CNN的计算加速。

ZYNQ是Xilinx公司设计的一种FPGA+ARM的芯片,该芯片通过使用AXI总线互联技术将FPGA与ARM整合在一起,从而可充分发挥出两种器件结构的优势。

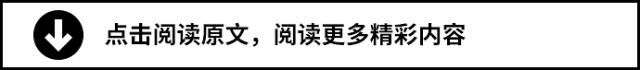

本文使用ZYNQ作为实现平台,采用软硬件协同的方式,通过ARM完成输入图像数据的实时采集、存储和显示,利用FPGA的硬件电路特性完成卷积神经网络的硬化实现,设计出了一种基于深度学习的实时识别硬件系统框架,从而可根据实际需求选择合适的网络模型。为了验证系统硬件框架设计的功能性,本文采用MNIST和Fashion MNIST数据集训练的两个CNN网络模型作为系统框架的功能验证。整体系统框架结构如图1所示。

1 图像采集存储及显示

1.1 图像采集存储

系统设计使用OV7670 CMOS摄像头进行系统视频图像数据的实时获取,并且将其分辨率配置为320像素×240像素,输出数据为RGB565色彩格式。由于不同模块之间的工作时钟不同,因此需要根据图像采集模块的控制信号和摄像头的时钟信号,将采集到的实时视频数据流存储至双口FIFO中进行跨时钟域处理,然后通过数据总线将图像数据存储在ZYNQ的双端口的BRAM当中,从而使得整个系统能够对采集的图像数据进行读取和处理。

1.2 图像显示

系统框架设计中使用ILI9341作为控制芯片,分辨率为320×240的2.8寸TFT显示屏作为视频图像数据的输出显示,然后通过SPI总线接口协议完成对摄像头模块获取到的每一帧图像数据进行发送传输。图像显示模块通过数据总线将TFT显示屏的ILI9341控制模块连接在双端口的BRAM上,根据双口BRAM当中的存储数据量进行图像数据的高速读取,将读取到的图像数据存储至双口FIFO当中进行存储及读取,从而实现将摄像头采集的视频图像数据进行显示。同时根据CNN网络模型的帧控制信号及运算完成控制信号,将图像数据读取至CNN网络模型当中进行运算识别,识别完成后也将运算结果更新至双端口FIFO进行结果输出显示。

2 卷积神经网络硬件设计及实现

系统框架中的可替换网络模块设计实现了两个结构一致的CNN网络模型,其结构如图2所示,该CNN网络模型结构由1个输入层、6个卷积层、3个池化层、1个全连接层和 1个输出层共12层构成。

其中第1层、第12层为输入层和输出层。输入层完成经过预处理调整后的一帧图像数据输入,由于用来验证系统框架设计的两种训练数据集为MNIST和Fashion MNIST数据集,因此网络的输入层均为28×28的窗口,输入数据为784个。输出层连接的权重个数为16×11=176个,输出结果为11种,其中一种为无效。

第2、3、5、6、8、9层均为卷积层。输出特征图的个数分别为4、4、8、8、16、16个,每层卷积核大小为3×3,移动步长均为1,并且卷积运算结果的图像尺寸大小与输入图像一致,激活函数选择便于硬件实现的ReLU作为激活函数且无偏置,每一层的参数分别为:

第2层:权重为3×3×4=36个

第3层:权重为3×3×4×4=144个

第5层:权重为3×3×4×8=288个

第6层:权重为3×3×8×8=576个

第8层:权重为3×3×8×16=1 152个

第9层:权重为3×3×16×16=2 304个

因此整个卷积层总共有4 500个参数。

第4、7、10层为池化层。在池化层也采用卷积运算,卷积核大小为2×2,使用最大池化方法。

2.1 网络模型参数

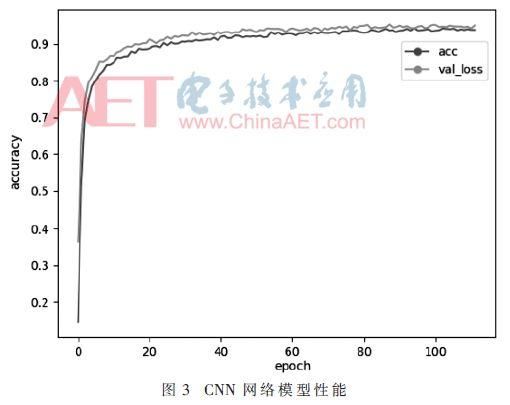

根据设定的网络结构及选用的方法,通过使用Keras深度学习库的函数式模型来进行CNN整体网络结构的搭建,同时将网络的学习率设置为0.001,选择随机梯度下降法SGD作为学习方法,经过130次迭代训练后完成两种CNN网络模型的建立,并且将训练好的网络模型参数进行存储。最终建立的整体网络性能如图3所示,可以看出随着迭代次数的增加,网络的性能逐渐提升,并经过测试后,CNN网络的整体精度可以达到97.14%,其性能基本能够满足实际应用的需要。

由于FPGA本身并不适合进行浮点运算,因此为了实现FPGA的网络硬化,必须将所生成的网络模型参数

进行定点数处理,但因为所生成的网络模型参数数值范围较大,会使得定点数所需位数较多从而消耗大量的硬件逻辑资源,所以本文首先对网络模型中的权值参数进行归一化处理,然后寻找出最优定点数表示的位数使得权值参数所需位数最小且不影响整体网络的精度。通过Python读取网络参数并进行最优寻找后系统设计使用12位位宽进行定点数表示,并将转换后网络模型的权值参数按照一定的顺序存储至片内BRAM中。

2.2 卷积层硬件实现

在系统框架设计的卷积层中,为了实现卷积运算,需要将BRAM中存储的图像数据进行缓冲处理。因为要进行卷积运算,其过程是将输入的每一帧图像数据与每一层所对应卷积层的卷积核Kernel所重叠的部分进行对位相乘相加,所以必须使得输入的数据与卷积核的大小相匹配。在系统设计中利用移位寄存器(Shift Register)来实现对图像数据的缓冲处理,通过移位寄存器能够将BRAM当中的图像数据进行缓存处理并且能够进行移位操作,使得图像数据与对应的卷积核进行对位卷积运算。由于设计中的输出图像与输入图像数据大小一致,因此还需要对输入图像数据进行填充操作以保证输出后的特征图大小保持不变,且通过移位寄存器使得系统能够在运行时实现单周期的卷积运算,提升了系统的计算效率。当卷积运算完成后还需要经过激活函数,系统设计中使用了ReLU函数作为输出激活函数,该函数的输出取决于输入数值大小,当输入数值大于零时输出原输入值,小于零时输出零,因此硬件容易实现,系统中使用比较器实现激活函数,从而完成卷积层的计算,进而提取当前层的输入图像特征。

2.3 卷积层运算并行优化

由于整个CNN网络模型中的每个计算模块是互不相关且独立的,充分体现出了其结构能够进行并行运算的特性,尤其是在进行卷积运算时,而FPGA本身的硬件电路结构,也使其具有进行并行运算的特点。因此在整体系统框架设计中均采用了并行化的实现方法,框架设计中为每个卷积层的卷积核进行了卷积核组的设定,根据特征图输入和运算后特征输出的个数来确定卷积核组的数量,来并行地对设定的每个卷积核组进行卷积运算,获取输入图特征。因为系统框架设计中对池化层中的最大采样也采用了卷积运算来完成,所以本系统框架设计能够实现单时钟周期528次卷积运算,与普通CPU的运算时间相比较,本系统框架的计算效率得到了明显提高。系统框架卷积运算优化设计具体结构如图4所示。

图4中xi为特征数据输入,wij分别是卷积核组中的不同卷积核权值,ki为不同的卷积核组,ci为特征数据输出。

2.4 Softmax函数分类器

输入图像数据通过整体网络中的卷积层和采样层计算后完成对输入图像数据的特征提取,然后还需要将其与最后的输出层进行全连接才能最终获取图像数据的分类结果。系统框架设计中使用了Softmax函数作为分类器来实现对图像数据的分类结果输出。由于Softmax函数的概率分布计算是通过指数运算得出的,且概率分布的计算结果为浮点数,而FPGA本身的硬件结构会使指数计算耗费较长时间,因此设计中通过查表法将计算后的指数运算结果存储至BRAM当中,然后根据输入图像数据的特征值作为地址来查找所对应的指数结果。当一帧输入图像数据经过CNN网络模块计算识别后,将结果更新至显示模块的BRAM当中,并且也会通过蓝牙控制模块同时将结果发送至上位机进行识别结果显示。

3 系统测试与分析

系统设计中的具体硬件使用Xilinx公司的ZYNQ-7000 xc7z010clg400-1芯片作为试验平台,该芯片内部拥有28k个逻辑单元,2.1 Mb的嵌入式存储器,80个嵌入式乘法器,片内资源较为丰富,基本能够满足系统框架中的CNN模型硬件设计所需要的资源。CPU软件训练平台使用Core i7-8700k处理器,主频为3.4 GHz。使用Vivado 2018.1开发工具完成整个硬件平台工程。

测试过程中,分别使用对应MNIST和Fashion MNIST数据集的测试样本进行实际测试,通过摄像头对200个20种类别的图像数据进行实时视频采集、显示及识别,部分测试结果如图5所示。

可以看出整个系统框架设计能够完成对图像数据的实时采集和显示,同时可根据实际需要替换不同的CNN网络模型且均能够实现对结果的正确识别,从而实现了多场景下的需求并增加了一定的灵活性。

系统框架设计中主要的硬件资源消耗及功耗估算如表1所示。

系统设计因为中使用了大量的BRAM和FIFO进行权值数据与图像数据的存储,使得BRAM的硬件逻辑资源消耗较多,但可以看出实验所用使用的ZYNQ器件基本能够满足本文所设计的系统框架。

4 结论

本文设计了一种基于深度学习的实时识别硬件系统框架,采用软硬件协同的方式,利用ZYNQ中的ARM部分实现了对图像数据的采集及显示,通过FPGA部分实现了CNN网络模型的硬件设计,并对整个卷积层进行了并行运算优化,使得整个系统能够在单时钟周期内同时处理所有卷积层中的528次卷积运算,提升了运算速度。实验结果表明,该系统框架能够根据不同的场景应用需求选择适合的CNN网络模型进行图像实时采集、显示与准确识别,结合ZYNQ器件中高度模块化设计使得整个系统框架具有移植性高的特性,且系统整体运行时识别速度快、所需功耗低。

参考文献

[1] Pei Jifang,Huang Yulin,Huo Weibo,et al.SAR automatic target recognition based on multiview deep learning framework[J].IEEE Transactions on Geoscience and Remote Sensing,2018,56(4):2196-2210.

[2] LECUN Y,BENGIO Y,HINTON G.Deep learning[J].Nature,2015,521(7553):436-444.

[3] 朱虎明,李佩焦,李成,等.深度神经网络并行化研究综述[J].计算机学报,2018,41(2):1-23.

[4] 王海,蔡英凤,贾允毅,等.基于深度卷积神经网络的场景自适应道路分割算法[J].电子与信息学报,2017,39(2):263-269.

[5] 蒋兆军,成孝刚,彭雅琴,等.基于深度学习的无人机识别算法研究[J].电子技术应用,2017,43(7):84-87.

[6] 许少尉,陈思宇.基于深度学习的图像分类方法[J].电子技术应用,2018,44(6):116-119.

[7] 胡振,傅昆,张长水.基于深度学习的作曲家分类问题[J].计算机研究与发展,2014,51(9):1945-1954.

[8] 张榜,来金梅.一种基于FPGA的卷积神经网络加速器的设计与实现[J].复旦学报(自然科学版),2018,57(2):236-242.

[9] 周飞燕,金林鹏,董军.卷积神经网络研究综述[J].计算机学报,2017,40(6):1229-1251.

作者信息:

王 昆,周 骅

(贵州大学 大数据与信息工程学院,贵州 贵阳550025)