《破解数字VLSI验证面试》翻译计划——第一章

前言

本文基于《破解数字VLSI验证面试》翻译计划——综述展开翻译的!

第一章:数字逻辑设计

理解数字逻辑设计的基本原理是执行VLSI行业任何工作的基本技能。因此,无论面试是针对ASIC设计工作、验证工作还是任何后端设计或布局工作,测试逻辑设计技能的问题都是面试的重要部分。因此,这是在超大规模集成电路(VLSI)工业中获得工作的最基本和最重要的课题。本节列出了访谈中最常见的一些问题,并给出了答案和概念的详细解释。一旦你通过这些问题掌握了这些概念,同样的概念和逻辑方法也可以用于相关的问题。

1.1 数字系统、算术和代码

数字系统是数字系统中传递和量化信息的基础。本节包括与十进制、二进制、八进制和十六进制(hex)等常用数制有关的问题,不同数制中的算术运算,不同表示法之间的转换等。

1. 使用最小可能位数将以下十进制数转换为有符号的二进制、八进制和十六进制数。

a) 17 b) -17

十进制数由十进制数字(0到9)组成,二进制数由二进制数字(0,1)组成,八进制数由八进制数字(0到7)组成,十六进制数由16位数字(0到9,A,B,C,D,E和F)组成。十进制数字可以通过以下三个简单步骤转换为任何其他基:

- 将十进制数除以基数(即2表示二进制,8表示八进制,16表示十六进制)

- 余数将构成转换后的表中的最低位数

- 重复上述步骤1和步骤2,直到没有除数保留MSB表示“符号”信息。对于负数,MSB为1;对于正数,MSB为0。

使用上述步骤,我们将得到十进制数17的二进制值10001、八进制值21和十六进制值0x11。

十进制数-17表示为:二进制=101111,八进制=57,十六进制=0x2f

2. 十六进制数0x3A转换为十进制是多少?

0x3A=[0xA·160]+[0x3·161]=[10·1+3·16]=58

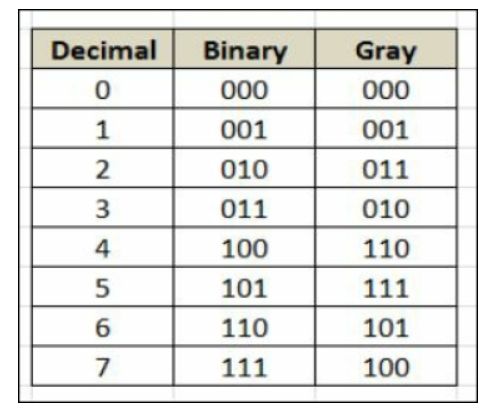

3. 什么是格雷码?使用格雷码(与二进制码相比)有什么好处?

格雷码是一种二进制数系统,其中两个连续值只有一位不同。它也被称为反射二进制代码

在二进制代码中,两个值之间的转换可能会在两个以上的位上进行转换,如果不同的位需要不同的时间进行转换,这有时会导致歧义。例如:在二进制(011到100)中从3转换到4需要切换所有位。这可能导致一些中间值,如果说三位有不同的切换时间。

而在格雷码中,由于每次只有一个比特发生变化,因此不可能出现这种模糊。

使用格雷码的另一个优点是:由于格雷码切换的比特位较少,使用格雷码的设计将比使用二进制代码的设计消耗更少的能量。

4. 什么是奇偶校验位,它是如何计算的?

奇偶校验位是加在二进制代码字符串末尾的位,它表示字符串中值为“1”的位数是偶数还是奇数。因此,奇偶校验码有两种变体-偶数奇偶校验和奇数奇偶校验。

为了计算奇偶校验位,计算二进制代码中具有值“1”的位的总数。如果“1”的数目是奇数,如果我们使用偶数奇偶校验,那么奇偶校验位被设置为1,这样包括奇偶校验位在内的“1”的总数就变成偶数。如果“1”的数目是奇数,并且如果我们使用奇数奇偶校验,那么奇偶校验位被设置为0,这样包括奇偶校验位在内的“1”的总数计数为奇数。

奇偶校验位是通过取二进制字符串中所有位的异或来计算的。奇偶校验位是检错码的最简单形式。

5. 对于给定的二进制字符串:111001,计算适当的奇偶校验位。

给定的二进制字符串:111001,有四个“1”。使用奇偶校验,二进制字符串中1的总数(包括奇偶校验位)必须是奇数。

因此,该字符串的奇偶校验位将为1。

6. What are 1’s complement and 2’s complement? Where are they used?(什么是反码和补码?它们怎么使用?)

If all bits in a binary number are inverted by changing each 1 to 0 and each 0 to 1, the resulting binary number is called the 1’s complement.

For example: The one’s complement of a binary number 110010 is 001101

The 2’s complement of a binary number is obtained by adding a 1 to the one’s complement of the number.

For example: The two’s complement of a binary number 110010 is 001101+1

The two’s complement of a number is used to represent signed binary numbers. It is also used for subtraction of binary numbers. The one’s complement is an intermediate step to get to two’s complement.

7. 什么是BCD码?它和二进制码有什么不同?十进制数27的BCD码和二进制码是什么?

BCD是二进制编码的十进制,是一种四位二进制代码,可用于表示任何十进制数字(从0到9)。二进制代码是十进制数的二进制表示,二进制代码所需的位数取决于十进制数。对于十进制数字0到9,BCD和二进制代码都是相同的。

数字27可以用BCD表示,2和7都使用四位代码。

因此,27的BCD将是0010 0111,而27的二进制代码将是11011

8. 以下哪种代码可以表示数字、字符和特殊字符?

BCD、Gray、EBCDIC code、ASCII code、Alphanumeric code

Alphanumeric code(字母数字代码)是字母和数字字符的组合,可用于表示数字以及字符/特殊字符

1.2 基本门电路

9. 以下哪一个门被称为万能门(通用门)?为什么?

AND(与)、NAND(与非)、OR(或)、NOR(或非)、XOR(异或)

通用门是可以实现任何布尔函数而不需要使用任何其他门类型的门。

与非门和或非门是通用门。

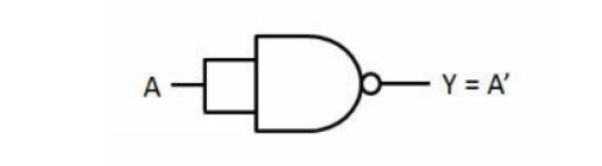

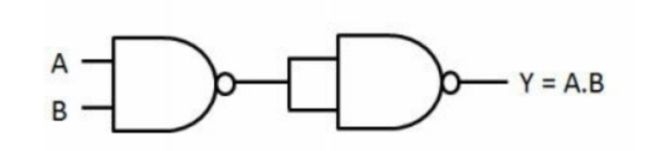

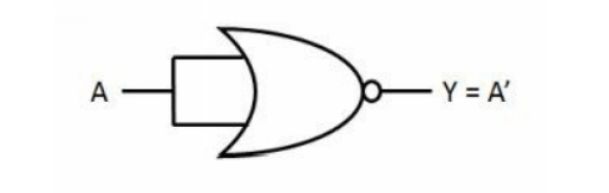

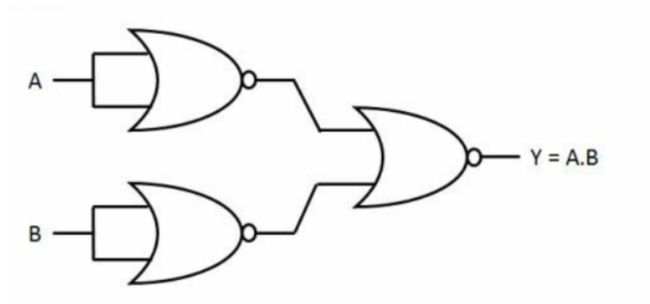

10. 如何使用两个输入与非门实现:双输入或门、双输入与非门和单输入非门?

如果A和B是与非门的两个输入端,那么与非门的输出方程是,Y=(A.B)’

- 非门:非门可以用输出方程Y=(A)’来描述。所以,如果一个与非门的输入端A和B被连接到同一个输入端,那么我们得到一个非门。

- 与门:与门由输出方程Y=A·B来描述。因此,将非门连接到与非门的输出将实现与门。

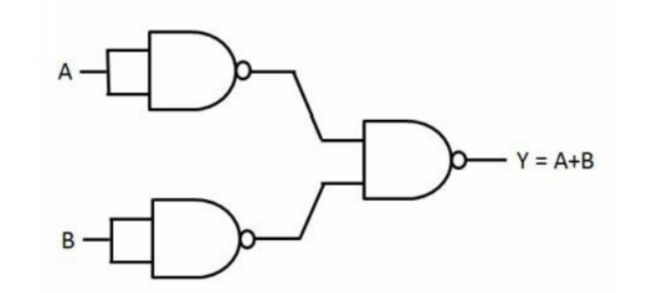

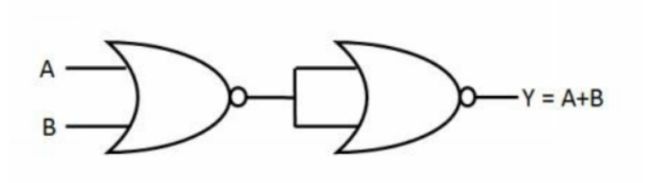

- 或门:用德摩根定律,或门可以描述为Y=A+B=(A’)’’+(B’)’’=(A’B’)’。因为A’和B’可以表示为非门,所以上面的方程可以表示为下面给出的或门。

11. 如何使用两个输入或非门实现:双输入AND、双输入OR和单输入非门?

NOR门用以下等式描述:Y=(A+B)’。

- 1)非门:非门是用Y=A’来描述的。如果一个或非门的两个输入端连在一起Y=(A+A)’=A’

- 2)与门:与门由方程Y=A·B=(A’)’(B’)’ = (A’+B’)'描述。因此,我们可以使用输入为A’和B’的NOR门。A’和B’可以使用A和B的NOT门来实现,如下所示。

- 3)或门:或门由Y=A+B=((A+B)’)’ 描述。因此,可以使用NOR门来实现(A+B)’,并且可以使用如下所示的后续NOT门来实现相同的反转

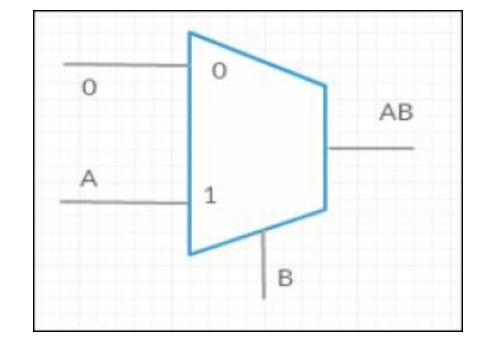

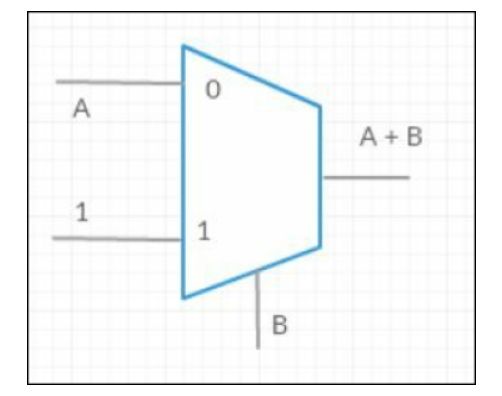

12. 如何使用2:1多路复用器实现以下门?

- a)单输入非门(NOT)

- b)两输入与门(AND)

- c)两输入或门(OR)

- d)两输入或非门(NOR)

- e)两输入与非门(NAND)

- f)两输入异或门(XOR)

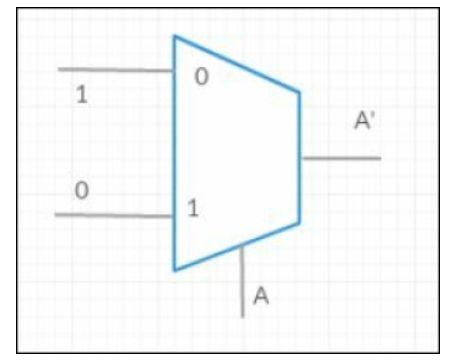

多路复用器是一种组合逻辑,可以使用选择线将两个输入多路复用到单个输出通道上。一个2:1的多路复用器将有一个单一的选择输入,并根据值(0或1),它将驱动输出与任何一个输入。

- a)单输入非门(NOT)

- b)两输入与门(AND)【联发科某次笔试题】

- c)两输入或门(OR)

- d)两输入或非门(NOR)

NOR门可以通过从上面使用OR门和NOT门的组合来实现

- e)两输入与非门(NAND)

NAND门可以通过从上面使用AND门和NOT门的组合来实现

- f)两输入异或门(XOR)

13. “异或”门在数据通信中的典型用途是什么?

异或门用于奇偶校验、CRC和ECC等检错码的计算。它也用于伪随机数发生器。

14. 3输入与非门的输出何时可以为零?

- a)当至少一个输入为0时

- b) 当所有输入为0时

- c) 当至少有一个输入是1时

- d) 当所有输入为1时

只有当所有输入都为1时,与非门才能获得零输出。所以,d)是正确的答案。

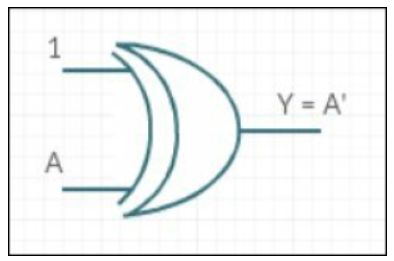

15. 如何使用异或门(XOR)设计反相器(inverter)?

用方程Y=AB’+A’B描述异或门。如果其中一个输入与1相连,如下图所示,那么我们得到:Y=A.1’+A’.1=0+A’=A’,这是非门或反相器。

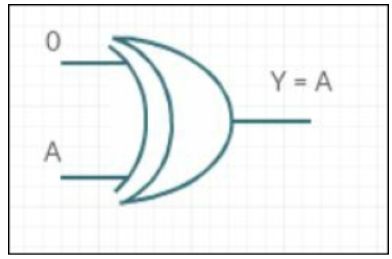

16. 如何使用异或门设计通过门或缓冲区?

传递门或缓冲区将输入按原样传递到输出。如果A是输入,Y是输出,这可以用Y=A来表示。因此,这可以使用异或门来实现,通过连接一个始终为零的输入,如下所示:Y=0·A’+0’·A。A=0+1·A=A

17. 如果其中一个输入未知(x),下列门的输出是什么?

-

a)或门

-

b)与门

-

c)非门

-

d)异或门

-

a)或门:如果或门的一个输入是x,那么输出取决于另一个输入。如果其他输入为1,则“或”门的输出为1,对于任何其他值,输出为x。

-

b)与门:如果与门的一个输入是x,那么输出取决于另一个输入。如果其他输入为零,则与门的输出为零,对于任何其他值,输出为x。

-

c)非门:如果非门的输入为x,则输出也为x。

-

d)异或门:如果异或门的输入之一是x,那么输出也将是x。

18. 楼梯间的灯泡有两个开关,一个在首层,另一个在其他层。无论另一个开关的状态如何,灯泡都可以通过任何一个开关打开和关闭。灯泡打开时,这个逻辑与哪个门相似?

让我们把S0和S1作为两个开关。如果已经有一个开关关闭(0),那么将另一个开关更改为1将给出ON=1。如果已经有一个开关处于ON(1)位置,则将另一个开关更改为1应关闭灯泡(off=1)。

| S0 第0页 | S1 | ON | OFF | |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 0 | (S0 was off, S1=1 causes bulb to turn on) |

| 1 | 0 | 1 | 0 | (S1 was off, S0=1 causes bulb to turn on) |

| 1 | 1 | 0 | 1 | (either S0/S1 was on and changing other switch to 1causes bulb to be off) |

因此,灯泡的开启行为类似于异或门。

1.3组合逻辑电路(Combinational Logic Circuits)

19. 组合电路和时序电路有什么区别?

-

组合电路:在任何时刻的输出只取决于当前时刻的输入的电路称为组合电路。 因此,这些电路不包含任何存储器元件。组合电路的一些例子有半加器、全加器、多路复用器、解码器等。

-

时序电路:任何时刻的输出既取决于当前时刻的输入,又取决于过去时刻的输出值的电路称为时序电路。因此,这些电路具有某种形式的记忆元件来记忆过去的值。时序电路的一些例子有触发器、寄存器、计数器等。

20.What is the difference between a Multiplexer and Demultiplexer?(多路复用器和解多路复用器的区别是什么?)

一个n对1的多路复用器,简称MUX,是一个设备,它允许您选择n个输入之一,并直接将其输出到一个单一的。

解复用器(简称DeMUX)基本上是输入和输出相反的多路复用器。对于1到n的解复用器,您有一个输入,可以选择n个输出来定向输入。

【思考】这不就是编码器与译码器吗?

21.Design a 4:1 MUX using 2:1 multiplexers?(使用2:1多路复用器设计4:1多路复用器?)

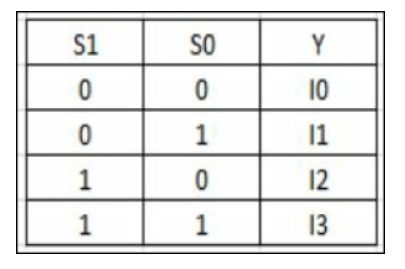

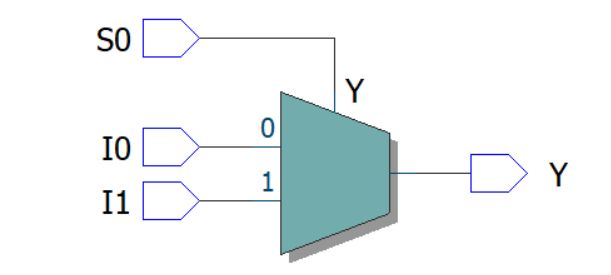

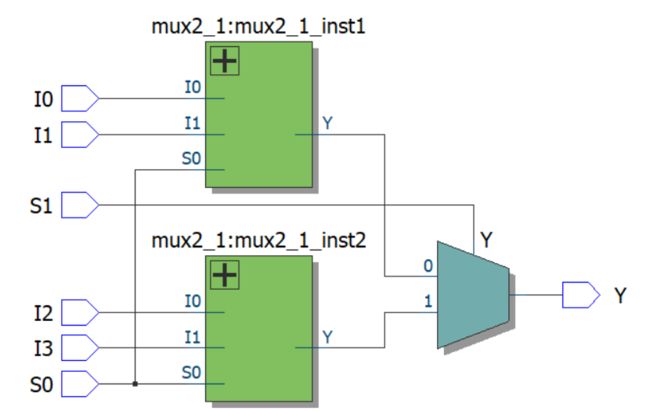

可以使用2:1多路复用器设计4:1多路复用器,如下所示。下面是4:1多路复用器的真值表(S1、S0是选择线,I0-I3是4条输入线,Y是输出)。

所以你可以看到,S1可以用来选择一半的输入,在每一半中,S0可以用来选择其中两个输入中的一半。

mux2_1的设计代码与综合电路图

module mux2_1(

input I0,

input I1,

input S0,

output Y

);

assign Y = S0 ? I1 : I0;

endmodule

mux2_1的设计代码与综合电路图

module mux4_1(

input I0,

input I1,

input I2,

input I3,

input S0,

input S1,

output Y

);

wire Y0,Y1;

mux2_1 mux2_1_inst1(

.I0(I0),

.I1(I1),

.S0(S0),

.Y(Y0)

);

mux2_1 mux2_1_inst2(

.I0(I2),

.I1(I3),

.S0(S0),

.Y(Y1)

);

assign Y = S1 ? Y1 : Y0;

endmodule

module mux2_1(

input I0,

input I1,

input S0,

output Y

);

assign Y = S0 ? I1 : I0;

endmodule

22. 设计2n:1多路复用器需要多少个2:1多路复用器?

正如我们在前面的问题中所看到的,4:1 MUX可以使用三个2:1 MUX来实现。这包括一个用于选择两半输入的MUX和两个用于在每一半输入的两个输入之间进行选择的MUX。

如果我们将这个概念扩展到8:1 MUX,我们将需要一个2:1 MUX在两个半部分(每个4个输入)之间进行选择,然后我们将需要两个4:1 MUX(每个需要三个2:1 MUX)。

因此,对于“2n:1”MUX,我们需要一个2:1 MUX和两个“n:1”MUX。如果我们对n:1mux应用相同的逻辑,进一步,我们将得到以下方程,这是一个几何级数。

所需的MUX总数=1+2+4+8+……+2(n-1)=2n-1

23. 编码器和解码器有什么区别?

解码器是将给定数量的输入信号解码为给定数量的输出信号的组合电路。

例如:3到8解码器将3位输入信号解码为8位输出信号,如下所示

000=>输出0

001=>输出1

010=>输出2

011=>输出3

100=>输出4

101=>输出5

110=>输出6

111=>输出7

编码器是一个组合电路,它的工作方式正好相反。它接受给定数量的n个输入,并将它们编码为较小数量的输出

例如:一个8到3的编码器可以完全反转上述3到8的解码器。可以有8个输入,每个输入都可以编码成3位二进制输出。

24. 编码器和多路复用器有何不同?

编码器与多路复用器类似,区别在于多路复用器只有一个输出,其中n个输入被多路复用,而编码器通常有2n个输入(或更少)和n个输出。

25. 什么是优先编码器,它与简单编码器有何不同?

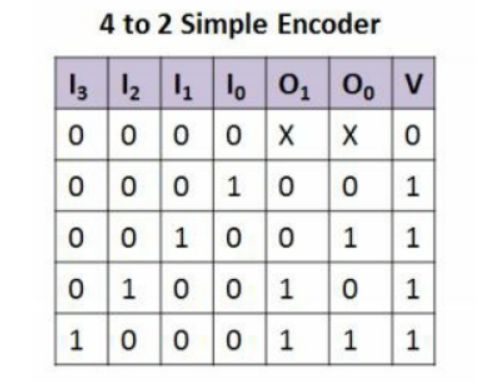

A simple encoder is a circuit that converts a 2n bit one-hot vector to an n-bit output.

For example: a 4 to 2 simple encoder encodes as per following table. The simple encoder expects the inputs to be one hot and if more than one input is high, then the outputs becomes X.

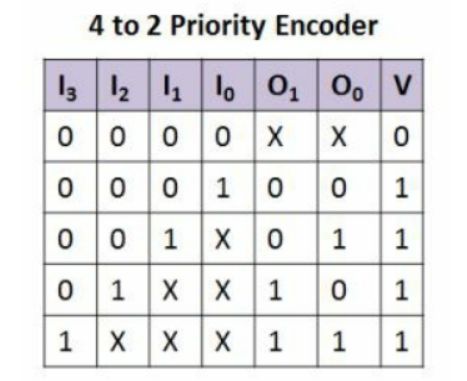

A priority encoder on the other hand encodes inputs with more than one bit being high using a priority. For example: a 4 to 2 priority encoder will encode a 4 bit input and if more than one bit is high, the MSB takes priority. Hence, it can be represented as table shown below.

26. 什么是环形振荡器?如果每个门有2ps的延迟,那么使用三个非门实现的环形振荡器的频率是多少?

环形振荡器是一种由奇数个非门组成的器件,其输出在两个电压电平之间振荡,表示真与假。非门或反相器连接在一个链中,最后一个反相器的输出反馈给第一个反相器。

如果三个非门连接在一个链中,那么从输入到输出的值需要三倍的反相器延迟。因此,两次转换需要6倍的反相器延迟。因此,时钟频率将为1/[6x(反相器延迟)]。对于我们目前的情况,时钟频率将为=1/(6x2)THz=1000/12 GHz=83.33 GHz。

1.4 时序电路与状态机(Sequential Circuits and State Machines)

27. 同步电路和异步电路有什么区别?

时序电路可以有两种类型:同步电路和异步电路

-

同步时序电路在离散的时刻改变它们的状态和输出值,这些时刻由时钟信号的上升沿(从0到1的转换)或下降沿(从1到0的转换)来指定。一个简单的例子是一个触发器,它存储一个二进制值,并且可以根据输入值在时钟边缘改变。

-

在异步时序电路中,从一种状态到另一种状态的转换是由主输入的变化引起的,而不需要像时钟边缘那样的任何外部同步。它可以看作是带反馈环的组合电路。由于逻辑门之间的反馈,异步时序电路有时会由于瞬态条件而变得不稳定,因此不常用。一个简单的例子:RS Latch。

28. Explain the concept of “Setup” and “Hold” times?(解释“建立”和“保持”时间的概念?)

-

建立时间是时钟进行有效转换之前,数据信号稳定的最短时间。

-

保持时间是时钟进行有效转换之后,数据信号稳定的最小时间。

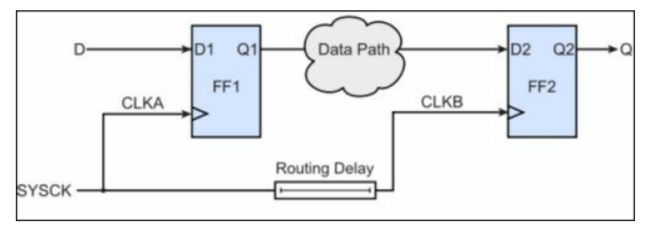

29. What is meant by clock skew?(时钟偏斜是什么意思?)

在相互作用的任意两个触发器上,时钟信号到达时间的差异称为时钟偏斜

例如,在上图中,来自第一触发器的D输入通过组合数据路径电路传播到第二触发器。来自一个公共源(SYSCK)的时钟被路由到两个触发器,但是由于布线或路由延迟,当两个触发器的边缘被看到时,可能会有一个小的差异。这个时间的差异被称为时钟偏斜。

时钟偏差只在两个触发器之间重要,其中一个触发器输出由第二个触发器采样。

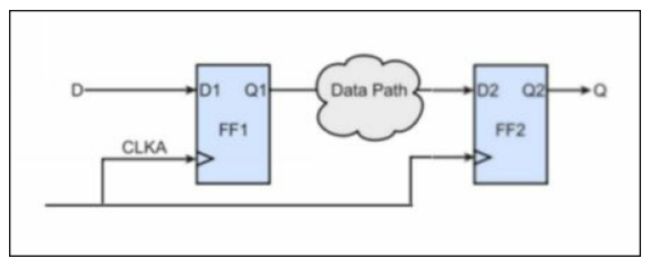

30. 对于如下所示的给定时序电路,假设两个触发器的时钟输出延迟为10ns,设置时间为5ns,保持时间为2ns。还假设组合数据路径的延迟为10ns。计算CLKA的最大频率,使设计能够正确运行?

为了使该时序电路正确工作,第一个触发器的输出应通过组合数据路径传播,并且应在下一个时钟边缘之前,在与第二个触发器的建立时间相等的最小持续时间内保持稳定。

如果TCLKA是时钟周期,TCQ是时钟到输出的延迟,TPD是数据路径的传播延迟,TSET是触发器的建立时间,那么我们得到这个条件TCLKA≥TCQ+TPD+TSET

因此,本例中的时钟周期需要>=10+10+5=25ns,并且最大频率将为1/25ns=40MHz。

31. 触发器和锁存器的区别是什么?

锁存器和触发器是存储信息的基本元件。一个锁存器或触发器可以存储一位信息。

锁存器和触发器之间的主要区别在于,对于锁存器,只要使能信号被断言,它们的输出就会不断地受到输入的影响。换句话说,当使能信号高时,当输入改变时锁存器的内容立即改变。

另一方面,触发器只在使能信号(通常是时钟信号)的上升沿或下降沿改变内容。在时钟的上升或下降沿之后,即使输入发生变化,触发器内容也保持不变。

32. 什么是竞争?什么时候会出现?如何避免?(What is a race condition? Where does it occur and how can it be avoided?)

当输出对不同事件的相对顺序或计时具有意外的依赖性时,将发生竞争条件。关于数字电子和SystemVerilog,竞争条件可分为两类:

-

硬件引起的竞争(Hardware race condition)

-

仿真引起的竞争(Simulation Induced race condition)

硬件竞争条件:如果我们看下面的SR锁存器(基于与非门),如果两个输入都是1(S=1和R=1),Q和Q’都会变成1,然后反馈到与非门。现在,如果S和R都立即变为0,Q和Q’都将进入竞争条件(值将开始振荡:1到0,0到1,1到0,依此类推…)。

通过适当的设计技术可以避免硬件竞争情况。示例:在SR锁存的情况下,我们可以通过如下所示的使能/控制信号来避免竞争条件:

always @(posedge clk or posedge reset)

if (reset) X1 = 0; // reset

else X1 = X2;

always @(posedge clk or posedge reset)

if (reset) X2 = 1; // reset

else X2 = X1;

SystemVerilog仿真器不保证多个always块之间的任何执行顺序。在上面的例子中,由于我们使用的是阻塞赋值,因此可能存在竞争条件,并且我们可以在多个不同的模拟中看到X1和X2的不同值。这是竞争的一个典型例子。如果第一个always块在第二个always块之前执行,我们将看到X1和X2为1。如果第二个always块在第一个always块之前执行,我们将看到X1和X2都为零。

有许多编码准则,遵循这些准则我们可以避免模拟引起的竞争条件。例如:这种特殊的竞争条件可以通过使用非阻塞分配而不是阻塞分配来避免。

33. 使用2:1多路复用器实现D触发器

让我们以下降沿触发D触发器为例。下降沿触发D触发器只在下降沿将输入(D)传输到输出。在所有其他时间,输出没有变化(Q保留其值)。要使用2:1 MUX实现此功能,我们需要两个2:1 MUX,如下图所示。

这里,一个MUX的选择线是CLK信号,另一个MUX的选择线CLK’信号(反向CLK)。现在,当CLK为1时,第一MUX的选择线(左侧的一个)选择D(连接到i1),并且D因此被传送到第一MUX的输出(该输出进一步被反馈到第一MUX并且也连接到第二MUX的i1)。因为,当CLK为1时,CLK’为0,所以D不传输到Q(因为第二个MUX选择了i0)。因此,直到CLK保持为1为止,D中的任何变化都反映在第一MUX的输出上,但是不反映在第二MUX的输出上,因为为第二MUX选择了i0(这只是Q,因为Q连接到第二MUX的i0)。现在,当CLK从1转换到0时,不再选择D(对于第一个MUX,i0是活动的),并且在时钟的负边缘转换到输出Q之前出现的D的值。

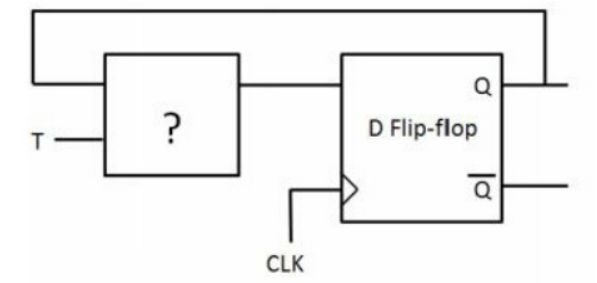

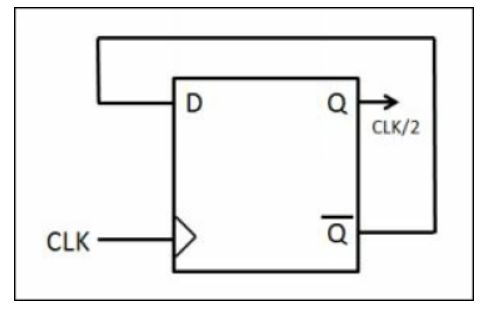

34. 如何将D触发器转换为T触发器?

T触发器,T为0时输出不变,1时翻转。写出真值表就能看出来,将输入和Q异或再输入到D端。

为了将任何触发器(比如说D触发器)转换成任何其他触发器(比如说T触发器),写下目标触发器行为(在这种情况下是T触发器)的激励表,并实现一个执行以下操作的组合逻辑:

将T触发器的输入转换为D触发器的正确输入,使其共同起到T触发器的作用。下图说明了这一点。

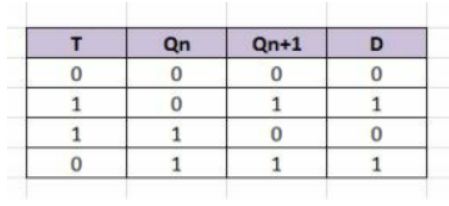

下表包括T触发器的激励表(以下前3列),最后一列显示输出Qn变为Qn+1所需的D值。

在上表中,我们使用K-映射将D实现为T、Q(n)和Q(n+1)的函数。这将给我们:D=T.Qn’+T’.Qn,这是一个异或门。

35. 将JK触发器转换为D触发器。

遵循上述问题中描述的原则,我们确定转换所需的组合逻辑。答案是:J=D和K=D’

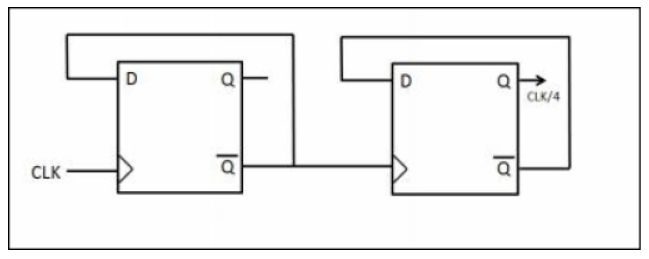

36. 同步计数器和同步计数器的区别是什么?

计数器是一种按循环顺序计数的时序电路,循环顺序可以是递增计数,也可以是递减计数。计数器是使用一系列触发器和组合逻辑实现的,这些逻辑将一个触发器的输出反馈给另一个触发器。有两种类型的计数器-同步和异步。

在同步计数器中,所有触发器的时钟输入都连接到一个公共时钟信号,因此所有触发器都是同步变化的。

在异步计数器中,时钟输入只连接到第一个触发器,第一个触发器的输出连接到第二个触发器的时钟输入,类似地,其他每个触发器都由前一个触发器的输出进行时钟计时。

同步计数器的一些例子是环形计数器和约翰逊计数器,而异步计数器的一些例子是升降计数器。

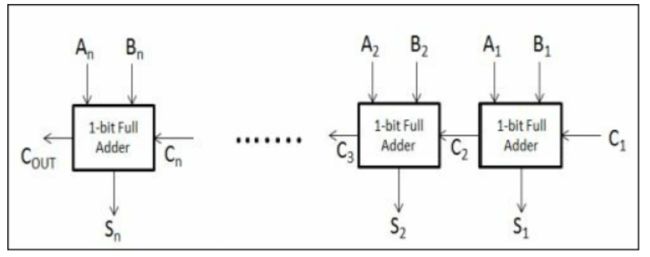

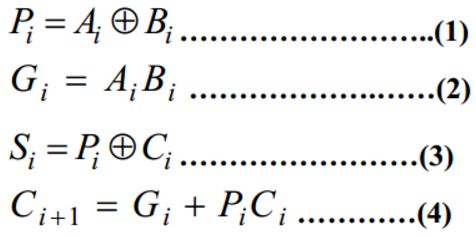

37. What is the difference between “Ripple Carry adder” and “Carry Look-ahead adder”?(行波进位加法器和超前进位加法器的区别是?)【参考了摸鱼范式推文】

- 行波进位加法器是慢加法器,因为输入(A1…AN, B1 BN)和进位s (C1 CN)向左波动,直到生成最后的进位(COUT)和最高有效位(即SN)。这是因为每个进位都是与和位一起计算的,每个位都必须等到上一个进位计算完毕后,才能开始计算自己的和位和进位。如下图所示。

- 超前进位先行加法器是快速加法器,因为它们减少了计算进位所需的时间。它在求和位之前计算进位,这减少了求和中其他有效位的等待时间。为了便于此操作,使用了中间的“Propagate”和“Generate”函数,其中Generate(Gi)=AiBi,Propagate(Pi)=Ai^Bi当从位置i有进位时,生成函数Gi生成1,当传入进位被传播时,传播函数Pi为真。因此,Ci+1= Gi + PiCi

事实上,在以下两种情况中,Ci=1:

- Ai和Bi都为1

- Ai和Bi有一个为1,且Ci-1为1

其对应的表达式为

递归后

可以看出每一级的进位信号可以不通过上一级的结果产生,只与输入有关系。因此减少了时间。

38. N位行波进位加法器的最长路径是什么?

(2N+1)门

为了更好地理解这一点,请考虑1位和2位行波进位加法器。对于1位行波进位加法器,最长路径有3个门。

对于2位行波进位加法器,最长路径有5个门。

39.同步和异步复位有什么区别?

同步复位:在时钟边缘采样时复位。当复位是同步的。此时,复位信号就像任何其他输入信号,在时钟沿采样。

异步复位:没有时钟也可以进行复位,此时,复位信号具有最高优先级,可以随时发生。

40. 实现一个32位寄存器需要多少触发器?

每个触发器可以保存一位信息。因此,要实现32位寄存器,我们需要32个触发器。

41. Mealy和Moore有限状态机有什么区别?

Mealy机是一种有限状态机,其输出既依赖于当前状态,也依赖于当前输入。

Moore机是一种有限状态机,其输出仅依赖于当前状态。

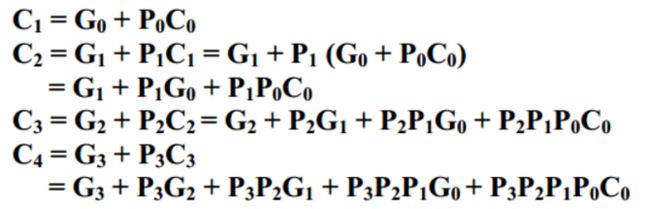

42. What is an Excitation table?(什么是激励表?)

激励表显示了当前状态已知时生成下一状态所需的最小输入。例如:下面是D、T和JK触发器的激励表。当前状态由Q(t)标识,而下一个状态为Q(t+1)。

43. 如果有选择的话,你会用哪个触发器来实现同步电路(比如序列检测器)?D还是JK?

取决于使用场景。

JK触发器可以导致一个更简单的电路,因为有许多不关心的值,触发器的输入,以实现下一个状态从目前的状态。

D触发器的优点是我们根本不需要设置触发器输入,因为D触发器的下一个状态等于输入。

44.在实践中,哪个触发器更常用于实现同步电路?D还是JK?

在实践中,D触发器的使用更为频繁,因为:

- 没有需要担心的激励表(下一个状态=输入)

2)每个触发器只有一个输入(与JK相比不是两个)

3)与JK相比,D触发器更易于实现。

45. 设计一个序列检测器状态机,从输入串行流中检测模式“10110”。使用D触发器。【之前用verilog实现过】

-

构造一个状态图和一个状态表,

-

将二进制代码分配给所有定义的状态,

-

使用当前状态、下一个状态和触发器激励表找出正确的触发器输入值,可以帮助从当前状态和输入中获得下一个状态,

-

为触发器输入和输出编写方程(使用电路最小化技术(如K图)简化方程),

-

建造电路。

46. 实现一个具有9种状态的数字同步电路所需的触发器的最小数目是多少?

每个触发器可以存储一位信息。因此,一个触发器可用于实现要求最多2个状态的同步电路,两个触发器用于要求最多4个状态的同步电路,三个触发器用于要求最多8个状态的同步电路,四个触发器用于要求最多16个状态的同步电路。因此,对于具有9个状态的同步电路,我们必须使用4个触发器。

47. 设计一个电路,当另一个计数器从0到255计数时,它将计数1。

48. 使用最少数量的D触发器实现以下逻辑:

1.5 Other Miscellaneous Digital Design Questions(其他各式各样的数字设计问题)

49. ASIC和SOC有什么区别?

专用集成电路(ASIC)是为特定应用而设计的组件,由特定公司在特定系统中使用,或出售给单个公司用于特定用途。例如:为非常特定的系统设计的特定24x24 10G交换机特定于应用的标准产品(ASSP)是一种更通用的设备,它是使用ASIC工具和技术创建的,但打算由多家公司在更广阔的市场上为不同的系统使用。例如:音频/视频编码器/解码器芯片,也用于特定应用,但目标市场更广。

片上系统(SoC)是集成整个子系统的芯片,包括微处理器或微控制器、存储器、外围设备、自定义逻辑等。

ASIC或ASSP可以是SOC,也可以是基于芯片中存在的不同设计元素的非SOC。

50.典型的ASIC或SOC设计流程中有哪些不同的步骤?

下面的框图描述了ASIC、FPGA或SOC设计的典型设计流程。

-

- Specification规范:这是设计过程中的第一个阶段,我们定义了系统的重要参数,这些参数必须设计成规范。

-

- High level Design顶层设计:在这个阶段,定义了设计架构的各种细节。在此阶段,定义了不同功能块的细节以及它们之间的接口通信协议等。

-

- Low level Design低层次设计:这个阶段也称为微体系结构阶段。在这一阶段,设计了每个功能块实现的底层设计细节。这可以包括诸如模块、状态机、计数器、mux、解码器、内部寄存器等细节。

-

- RTL codingTL编码:在RTL编码阶段,微设计采用Verilog/VHDL等硬件描述语言进行建模,使用可综合的语言结构。可综合的结构是这样RTL模型就可以输入到一个综合工具中,以便以后将设计映射到实际的门级实现。

-

- Functional Verification功能验证:功能验证是通过产生不同的输入刺激并检查设计实现的正确行为来验证设计的功能特性的过程。

-

- Logic Synthesis逻辑综合:综合是一个综合工具(如设计编译器)将RTL、目标技术和约束作为输入,并将RTL映射到目标技术原语的过程。在综合后还进行了功能等价性检查,以检查输入RTL模型和输出门级模型之间的等价性。

-

- Placement and Routing放置和路由:从合成工具中获取门级网表,并以Verilog网表格式导入位置和路由工具。所有的门和触发器被放置,时钟树合成和复位被路由。在每个块被路由之后,P&R工具的输出是一个GDS文件,由铸造厂用于制造ASIC。

-

- Gate level Simulation门级仿真:布局和布线工具生成包含门的时序信息的SDF(标准延迟文件)。这与门级网表一起被向后注释,并运行一些功能模式来验证设计功能。像黄金时段这样的静态时序分析工具也可以用于执行静态时序分析检查。

-

- Fabrication制造:在布局和布线阶段之后,一旦门级仿真验证了门级设计的功能正确性,那么设计就可以进行制造了。最终的GDS文件(一种二进制数据库文件格式,是集成电路或IC布局图数据交换的默认行业标准)通常被发送到制造硅的铸造厂。一旦制造完成,正确的封装就完成了,芯片就可以进行测试了。

-

- Post silicon Validation硅后验证:一旦芯片从制造中恢复,它需要在一个真实的测试环境中进行测试,然后才能在市场上广泛使用。这个阶段包括在实验室使用真正的硬件板和编程芯片的软件/固件进行测试。由于RTL模拟的速度比用真实硅在实验室进行测试的速度慢,所以总是有可能的找到硅验证中的缺陷,因此在确定设计是否适合市场之前,这是非常重要的。

后记

冲冲冲!