UVM笔记

一、UVM基本 概念

验证计划

功能覆盖率,结构覆盖率

模块机/芯片级/系统级

白盒/灰盒/黑盒

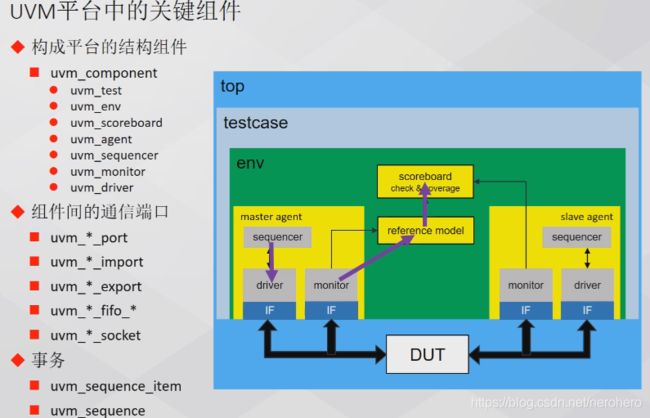

二、构建简化的UVM平台

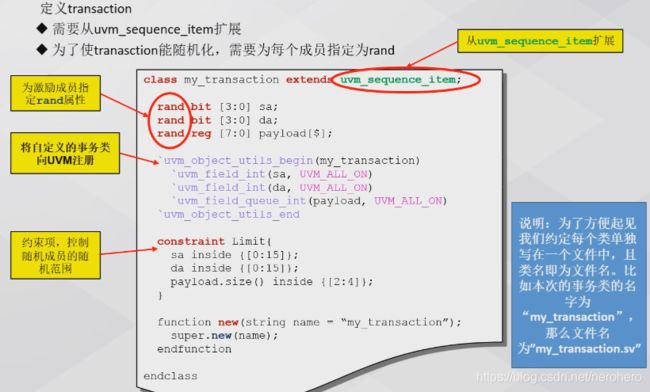

2.1、创建transaction

2.2、创建sequence

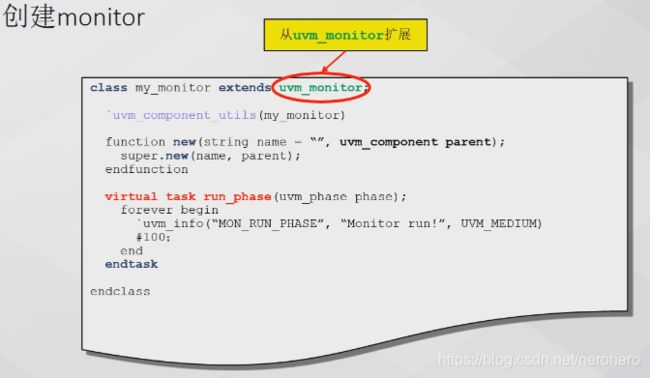

2.3、创建agent(sequencer,monitor、driver,phase顺序)

UVM平台中所有的组件具有phase概念,它们按照一定顺序执行的任务或函数产生。

2.4、创建agent

2.5、创建env

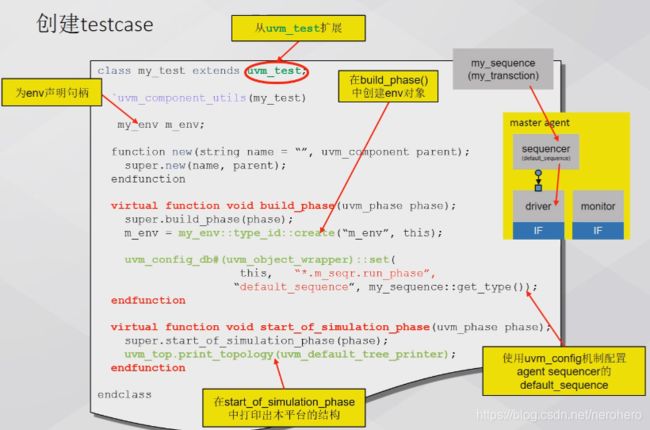

2.6、创建testcase

2.7、运行仿真

三、UVM平台组件

3.1、UVM库

UVM库-在类库中使用继承和封装

基本要素的三个层次:

1、TLM:TLM是组件之间的通信标准

2、Structural Elements:不同方法学的通用类:组件、信息系统、仿真阶段等等

3、Methodology:这个时用户实现平台重要的主要接口。使用这些接口用户可以在不改变测试平台代码的情况下更改平台的配置、替换平台组件、更换不同的激励甚至改变仿真行为等。

UVM package包含了三个主要的类

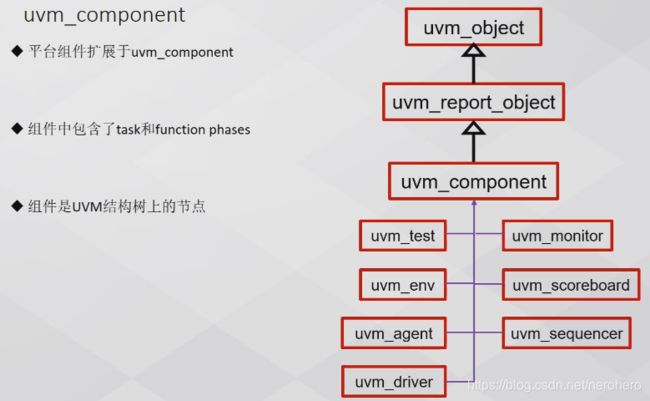

1、uvm_component:是用来构建UVM testbench层次结构最基本的类

2、uvm_object:作为UVM的一种数据结构,课作为配置对象来配置测试平台

3、uvm_transaction:用来产生激励和收集响应

3.2、uvm_component

3.3、UVM结构树

1、agent包含driver

2、env包含agent

3、test_case实例化env

简化的UVM结构树

顶层名字总为uvm_test_top

uvm的实际顶层为uvm_root,系统自己产生。

UVM构建这种结构的原因:

1、为config机制提供搜索路径

2、为override机制提供搜索路径

3、时phase自动执行的需要

3.4、UVM phase

UVM中为平台组件定义了一套phase流程来控制仿真平台的执行过程。

phase是uvm_component的属性

Task phase & Function phase。Task phase消耗仿真时间,图中黄色为Task phase其余都为Function phase。

build_phase自顶向下执行,其他phase都是自下向上执行。

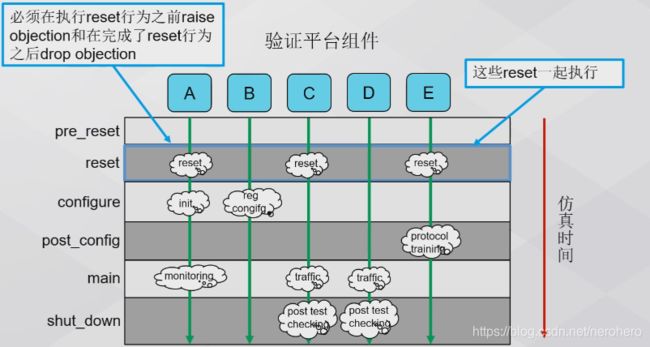

黄色区域为12个run-time pahse,这12个之间按顺序执行。相同组件的task phase同一时刻进行。

注意:

1、只有当所有component的同名phase都执行完毕时,才会执行下一个phase。

2、同名phase在不同的component中的顺序执行。

3、run phase与12个run time phase的关系。同时存在可以同时使用

从验证平台的构建,到配置,到连接,再到运行,最后停止需要有一定的先后顺序。

每一个component中都有一个任务或者函数与某个phase相对应,这些任务或者函数会在该phase阶段被自动的执行。

依次调用buile phase。

每个phase的功能:

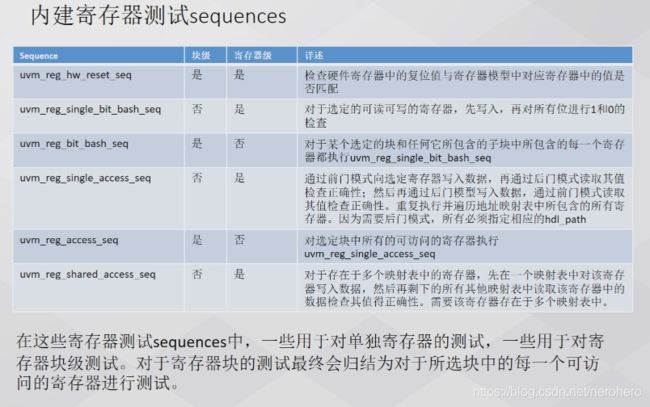

12个run-time phase

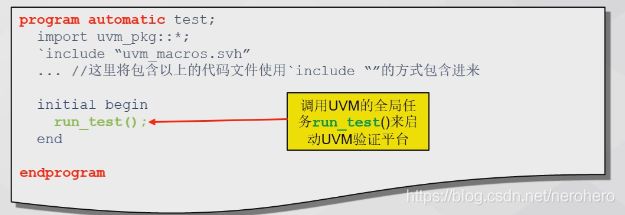

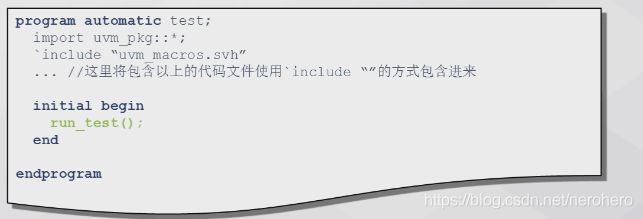

uvm_phase的启动

-使用run_test()启动UVM平台

3.5、UVM object

UVM phase具有objection属性

UVM phase的objection属性有两个作用:

1、控制task phase的运行与终止

2、同步各个components同名的task phase

objection的使用方法:

1、在task phase中调用raise_objection()和drop_objection()。

2、task phase中其他需要执行的语句放在这两个方法之间。

UVM objection注意事项:

1、objection对于task phase才有意义,控制task phase的运行和终止。

2、必须在执行消耗仿真时间的语句之前raise objection。如果在raise之前加入消耗仿真时间的语句,会导致raise失效,延时过后直接结束当前task。

3、在task phase结束时drop objection。否则将用于不会执行下一个phase,一直停留在当前phase。

4、在一个component中的某个task phase中raise和drop objection会影响到其他component中相同名字的task phase。

5、建议在每个task phase中都raise和drop objection一次。

示例对比:

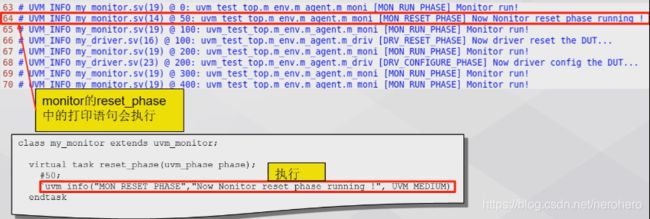

因为按顺序执行phase,所以如果reset_phase的执行了,那么configure_phase的打印就会变成在200延时打印。

修改代码后,在reset_phase添加raise和drop objection。

注意事项4和5:

monitor中的reset_phase没有raise和drop objection,但打印还是被执行了,原因在于,在driver中有同名的reset_phase

各组件中相同的task phase会并行执行。并且会同时开始,同时退出。

但是如果monitor中执行打印时的延时高,比如#50变成#150那么将不会有打印。因为在driver #100时结束了drop_objection,而monitor中又没有raise objection,那么monitor的objection会被终止。

四、UVM factory

4.1、什么是factory

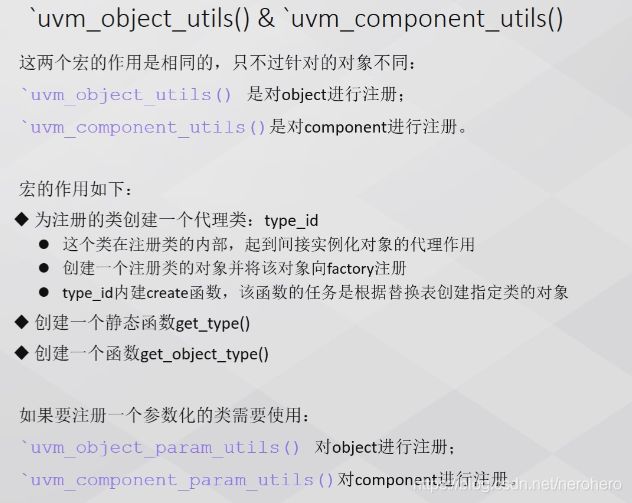

4.2、使用factory(uvm_component_utils,uvm_object_utils)

4.3、factory机制与override机制

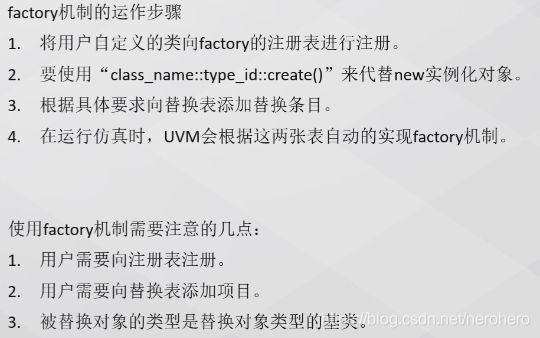

factory机制要与override机制结合使用。

factory是基础。override机制是为实现第三步而存在的,即要想factory的替换列表中添加替换项。

常见的override函数有两个:

set_type_override_by_type(original_class_name::get_type(),target_class_name::get_type());

set_inst_override_by_type(“original_inst_path”,original_class_name::get_type(),target_class_name::get_type());

这两个函数存在于component中,并且一般需要在build_phase()中调用。

第一个为全局替换,第二个为替换指定的路径,比如只替换master_agent中的类。

第一个为全局替换,第二个为替换指定的路径,比如只替换master_agent中的类。

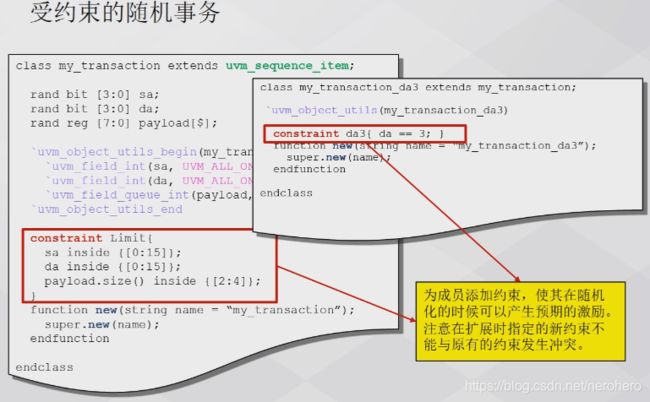

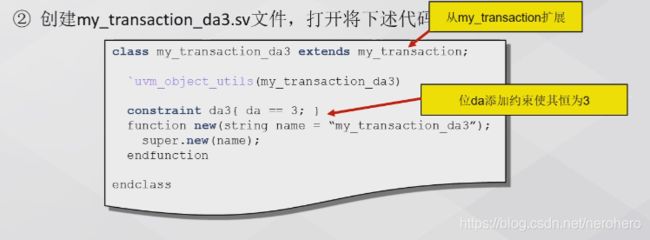

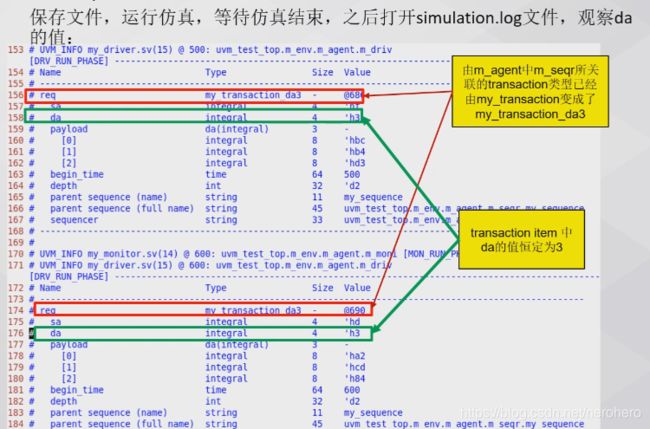

问题1:要将transaction中的da值约束为3

解决:

问题2:

仅仅希望替换master_agent中sequencer中的transaction类型而不是整个平台的呢?

解决:

UVM平台的重要性:在不改变原来平台的代码的情况下即可实现不同激励的产生。

五、事物级建模

5.1、什么是事物级建模

事物是一系列具有一定关系和功能的数据集合。

比如满足PCI协议的称为PCI事物,满足AMBA AXI协议的称为AMBA AXI事物。

是各个组件通信的基本单元。

5.2、从uvm_sequence_item扩展事物

5.3、UVM field automation机制

uvm_field_automation可以使用打印,复制,对比,记录,打包,解压等功能。

![]()

六、UVM信息服务

6.1、信息服务机制

6.2、安全等级及信息行为

七、UVM configuration

7.1、什么是UVM configuration机制

configuration机制的特点:

1、半个全局变量,避免全局变量带来的风险

2、高层组件可以通过configuration机制实现在不改变代码的情况下更改它所包含子组件的变量

3、在各个层次上都可以使用configuration机制

4、支持通配符和正则表达式对多个变量进行配置

5、支持用户自定义的数据类型

6、可以在仿真运行的过程中进行配置

configuration的原理:

UVM configuration机制的实现由两部分组成

1、设置配置资源

2、获取配置资源

7.2、如何使用configuration

八、UVM sequence机制

8.1、什么是UVM sequence机制

控制和产生一系列的事物,并将事物发送给driver的一套机制。

UVM sequence将事物的产生和驱动互相分离。

8.2、UVM sequence机制的原理

sequence机制在driver、sequenc、sequencer中完成。

8.3、如何使用UVM sequence机制

1、driver中实现 sequence机制:

2、sequencer中实现sequence机制:

UVM已经实现sequencer全部功能,只需要拿来实现即可。

3、sequence中实现sequence机制:

如果不用uvm_do宏,使用上述分解步骤完成可实现同样功能。

8.4、如何启动sequence

有两种方法:1、默认default启动 2、手动启动

一般使用方法2(手动启动)

8.5、sequence机制其他知识

九、UVM TLM

9.1、什么是UVM TLM

TLM -Transaction Level Model事物级建模,用于组件之间通信。

9.2、为什么要使用TLM

建立专门的通信通道,避免通信出现混乱。

各个通道独立,互不影响。

9.3、UVM TLM原理

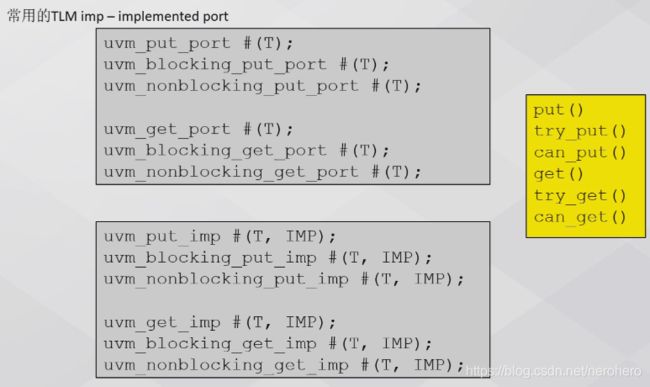

9.4、常用的UVM TLM port/import/export

T:该参数代表port所要传输的transaction的类型

TMP:指定所在的component

put():是一个task,可能会阻塞当前进程直到transaction传输成功。

try_put():是一个function,不会阻塞当前进程,不管transaction传输是否完成都会立刻返回。

can_put():是一个function,不会阻塞当前进程,不会发生transaction传输,只会检查对方是否准备好了接收。

*get():同理,传输变成接收。

port和import成对使用

uvm_put_port 支持 put(),try_put(),can_put()

uvm_blocking_put_port支持put()

uvm_nonblocking_put_port 支持 try_put(),can_put()

uvm_get_port 支持 get(),try_get(),can_get()

uvm_blocking_get_port 支持 get()

uvm_nonblocking_get_port 支持 try_get(),can_get()

export通常作为中间端口使用

示例:

![]()

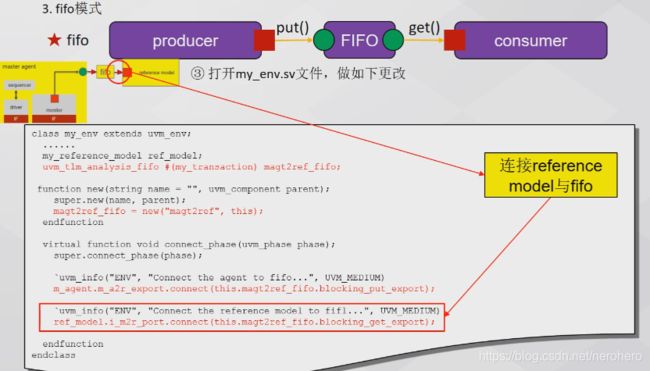

9.5、普通TLM端口的使用方法(PUT、GET、FIFO)

1、PUT模式

lab08

2、GET模式

lab08-a

3、FIFO模式(在PUT基础上修改)

lab08-b

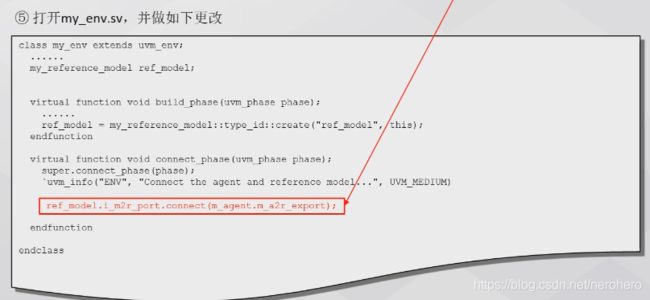

十、UVM analysis component

lab09

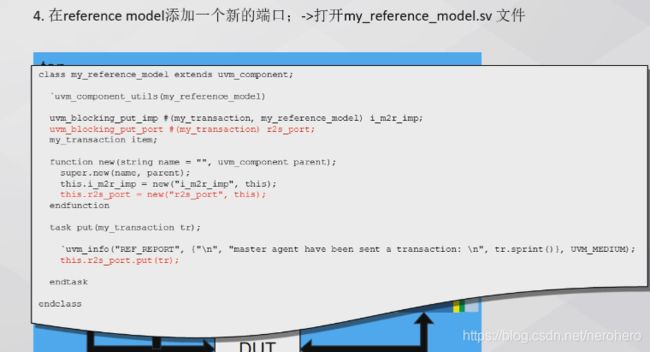

analysis component:1、reference model 2、scoreboard

实现步骤:

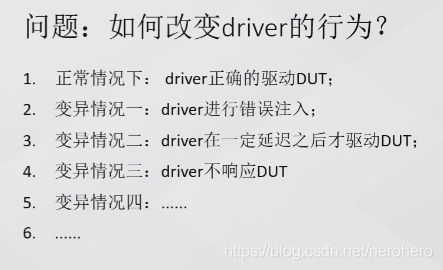

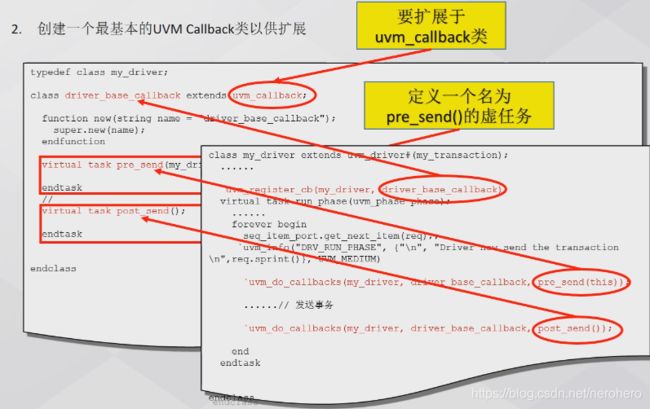

十一、UVM callback

11.1、什么是UVM callback

11.2、如何使用UVM callback

前三步都为定义,第四步为实例化使用。

上图这个示例没有载入post_send方法(post_send也会执行),所有post_send没有任何功能。

十二、UVM Advanced

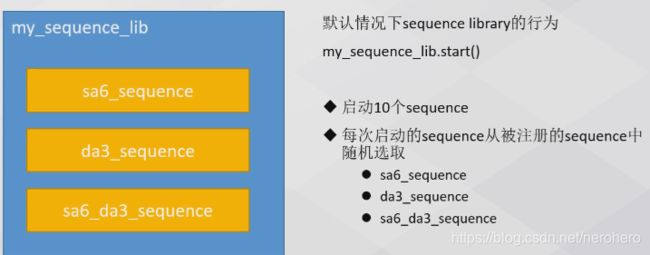

12.1、什么是UVM sequence library

sequence library其本质是一个sequence,相对于普通的sequence,sequence library有以下功能:

1、其他sequence可以想sequence library注册

2、可根据配置产生并且执行已经在其注册过的sequence

3、具有多种内嵌的选择sequence的算法

4、支持用户自定义的sequence选择算法

5、注册方式的多样化

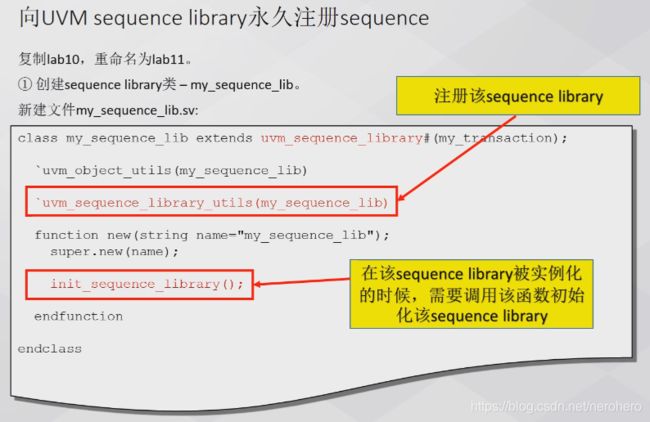

向UVM sequence library永久注册sequence

如何将sequence临时添加到UVM sequence library中

临时注册方法1:

上图为临时添加,在不同test中控制添加对应的sequence。

临时注册方法2:

sequence library内置的变量,作用是控制sequence library的行为

sequence library相关变量

例:

执行仿真

本技术在项目中使用较少。

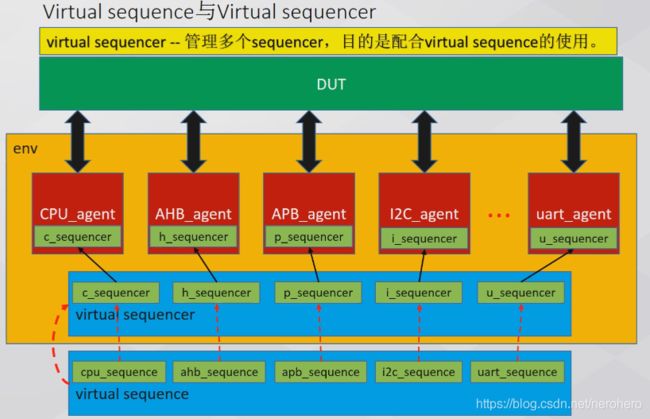

12.2、什么是Virtual sequence

代码实现:

与普通sequencer基本没区别

与普通sequence基本没区别

在env实例化它们并进行连接

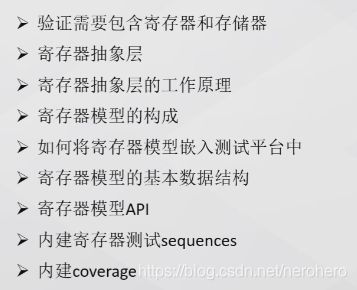

十三、UVM寄存器抽象级-RAL

13.1、寄存器抽象级概念

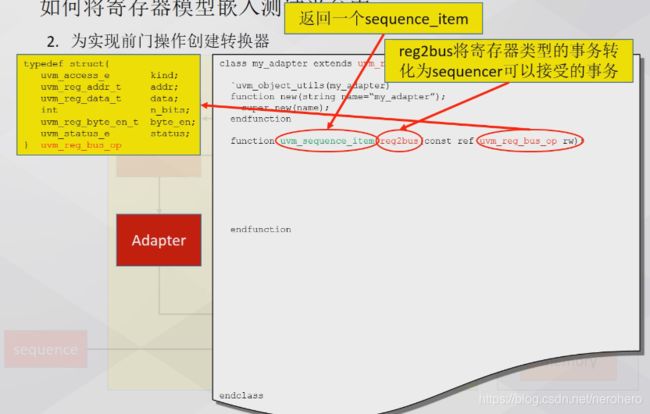

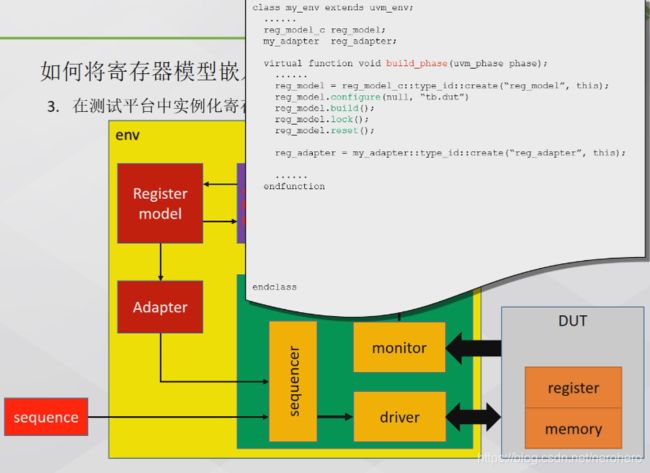

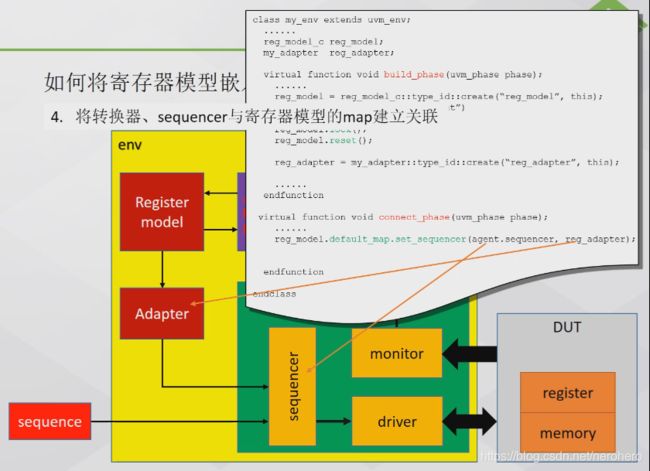

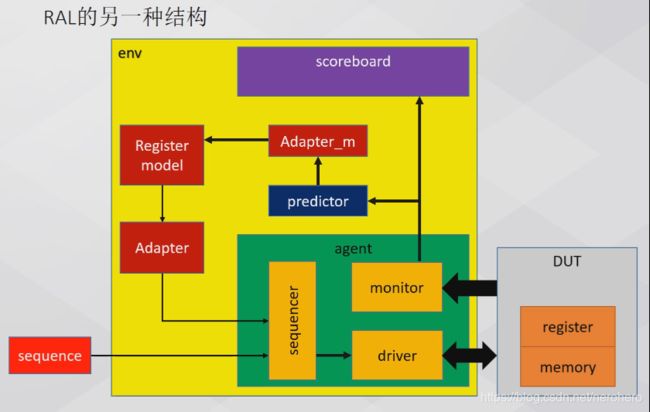

13.2、frontdoor实现?

13.3、寄存器模型的基本数据结构

14.4、寄存器模型API

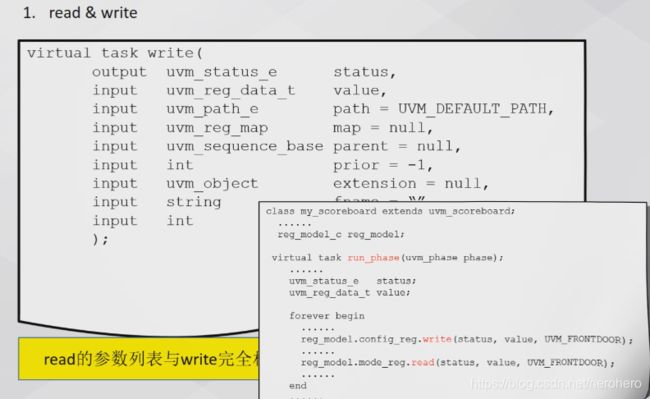

1、read&write

2、peak&poke

3、randomize&update&mirror

read&write默认一般使用前3个参数,其他使用默即可