数字锁相环的FPGA实现(一)

电赛著

开篇之前,感谢杜勇老师,和他所著的《数字通信同步技术的MATLAB与FPGA实现,Altera/Verilog版》

[TOC]

说到锁相环,相信大家都熟悉.锁相环路(Phase Locked Loop,PLL)是一个闭环的相位控制系统.这博客分成两篇,第一篇讲锁相环的基本原理和参数设置,第二篇写实战.

锁相环的环路模型

可以先看锁相环的组成再跳回来看这里.

假设输入信号和本地振荡器的输出信号是

我们通过这个来得到他们的瞬时相差和瞬时频差:

锁定与跟踪

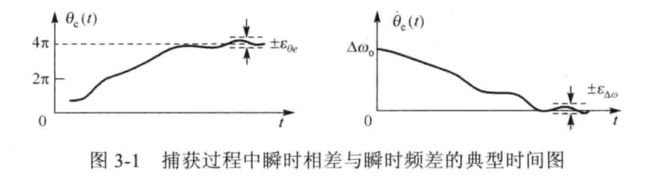

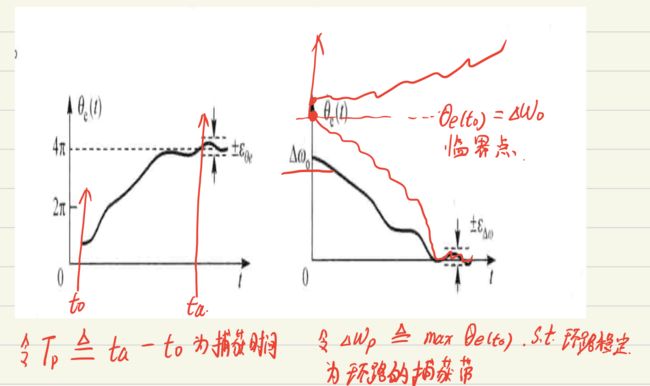

总所周知,我们一般假设输入信号的频率和本地振荡器的初始频率(也叫作自由振荡频率)是不同的,也就是说在这种情况下两者会存在固定频差,如果没有进行相位追踪的话,显然两信号的相差就会爆炸.如果我们可以控制固定频差在一个很小的范围,就能保证两个信号的相位差在左右一个很小的范围震荡,这个就是锁相环路的捕获过程,如下:

当瞬时相差稳定在附近,频差接近为0的时候,称锁相环进入同步状态,或称为跟踪状态

所以我们可以定义同步态的定义为:

再定义两个锁相环的参量,捕获时间和捕获带

环路的基本性能要求

如上所述,锁相环路存在两种状态,捕获状态和同步状态,就两种不同的工作状态下会有不同的性能参数:

- 捕获状态下的捕获时间

因为捕获时间其实和是有关系的,毕竟不同时间切入的瞬时相差是不一样的,在这里我们取起始频差等于的初始状态来计算最大捕获时间 - 环路的捕获带,即环路能通过捕获状态进入同步状态的最大固有频差

- 稳态相差,反映环路的跟踪精度

- 对已经锁定的环路,若改变其固有频差环路所能最大稳定的频率称为同步带

我们可以看看捕获带和同步带之间的关系,应该注意到在捕捉带外,同步带以内的频带,一旦出现失锁,是不能够重新捕获的

显然,不介绍基本结构和动态方程之前谈性能是没意义的,所以:

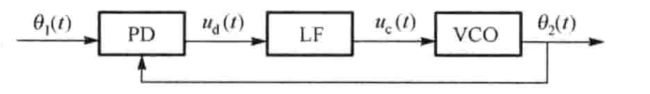

锁相环的组成

因为我们需要锁相环来实现相位跟踪,最终的目的是为了实现输出信号和输入信号的同步,出于此来考虑的话,我们需要这个系统的相位误差是可收敛的,即锁相环的系统模型是一个相位的负反馈控制系统,他的基本组成大家也清楚:

分别有:

- PD(Phase Detector)鉴相器

- LF(Loop Filter)环路滤波器

- VCO(Voltage-Controlled Oscillator,VCO)压控振荡源

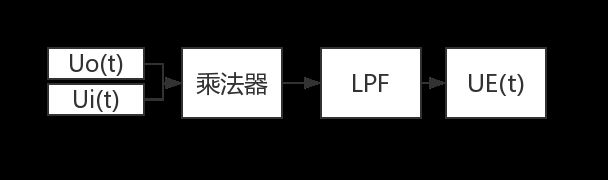

鉴相器(PD)

名副其实,鉴相器就是用来进行相位比较的,

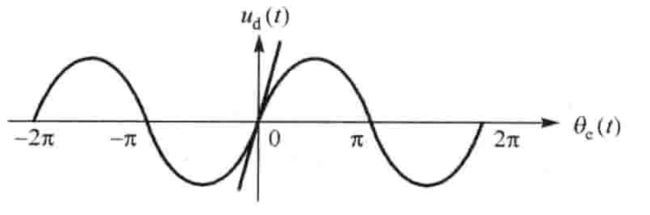

比较常用的就是我们上课所讲过的乘法器加低通滤波器所构成的正弦型特性的鉴相器:

但实际上到后面实现数字锁相环的时候可能就有不一样的方法了,敬请期待.

不妨推导一下:(设乘法器增益为)

经过LPF滤除的高频分量之后,得到:

其中:

环路滤波器(LF)

环路滤波器具有低通特性,一方面起着LPF的作用,另一方面是调节锁相环的参数的重要环节之一.对环路滤波器来说,他是一个线性电路,所以在时域分析中可用一个传输算子来表示,其实p是微分算子,在频域中就可以用来表示:

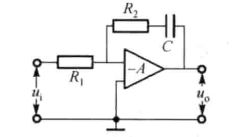

在这里我们不妨直接举一个我们都熟知的又有源比例积分滤波器:

可用较为轻松地算出他的传输算子:

其中:

其中A为运放开环增益,假设非常大,那么我们可用代入进行一些近似:

所以经过近似后,我们可用得到:

其中:

这个简化模型,特别如果有的时候,性能会接近无源比例积分滤波器

压控振荡器(VCO)

显然,对压控振荡器来说,他的本征方程是:

其中

表示输出瞬时角频率,为控制灵敏度或增益系数,单位是

我们可以轻松看出,他的控制特性依然是线性的.

而压控振荡器输出到鉴相器中,我们所需要考虑的是他所变化的相位情况,即:

所以我们可以看出鉴相器输出的相位误差信号和压控振荡器的电压控制信号中存在一个积分关系,而这个积分关系自然而然是在压控振荡源中完成的,对锁相环整体的性能也有比较大的影响.

锁相环的动态方程

现在要把刚刚介绍的三个部分综合起来一个系统来看了

非线性相位模型

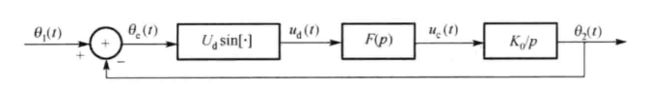

锁相环在时域上的传输流程是这样的

在考虑相位模型前,我们可以先反过来考虑稳态相差的问题,因为这涉及到锁相环稳定的可能性.显然在锁相环捕获的时候会逐步接近到同步状态的时候有,但是两个信号间存在稳态误差(相位)使得控制电压不为0,从而使输出频率在输入频率间震荡.但实际上对理想二阶环(A无穷大)来说,当环路锁定时,稳态相差理论上为0.但具体的分析还看后头

从上述模型中不难得出:

代入得锁相环路动态方程的一般形式:

不妨定义环路增益

显然这个环路增益表示的是VCO的最大频偏量,因为是误差信号的最大值,是增益系数(见上)

因为经过环路滤波器之后输出的误差信号是直流的,所以稳态误差很容易就可以解出:

这时考虑环路滤波器的传递因子,当A>>0时,有下列近似

其中:

所以容易得,这也是刚刚所说的理想二阶环没有稳态误差的来源.

但是实际上,因为A不可能无穷大,上式也只是近似得来的,所以上面的式子成立的可能性几乎也为0...

不妨将代入锁相环的动态方程:

因为环路滤波器只有一个极点,传输算子是一阶的,所以相应的环路动态方程是二阶非线性微分方程,所以这种锁相环路称为二阶锁相环路.本博客缺少了对RC积分滤波器和无源比例积分滤波器的分析,有兴趣的pong友可以自行回去看书

线性相位模型

线性相位模型就是将 非线性相位模型 近似得出的,因为显然动态方程是一个高阶的非线性微分方程(特别是加上噪声之后),而又由于瞬时相差一般是很小的,回顾一下高等数学的等价无穷小,我们容易想到sin(x)~x:

也就是说,我们可以把正弦换成:

斜率是的直线代替,代入式得:

再令环路增益:

则得到线性模型:

环路的传递函数

事先说明一点就是,这里对环路传递函数的建模是基于线性模型的,也就是说他同样存在上述的等价无穷小代换问题,所以不适应瞬时相差过大的情况.

不妨对线性模型做拉普拉斯变换:

- 考虑开环状态下(无反馈支路),输入相位驱动所引起的输出相位的响应:

解得:

- 考虑闭环状态下,输入相位驱动所引起的输出相位的响应:

- 考虑闭环状态下,输入相位驱动所引起的误差相位的响应:

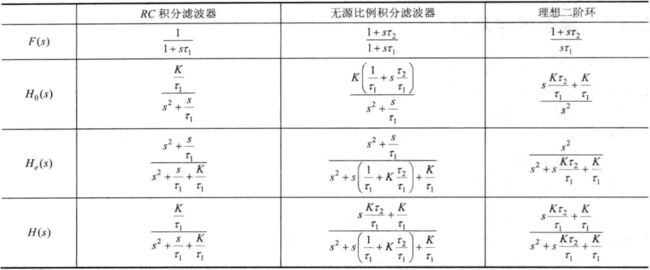

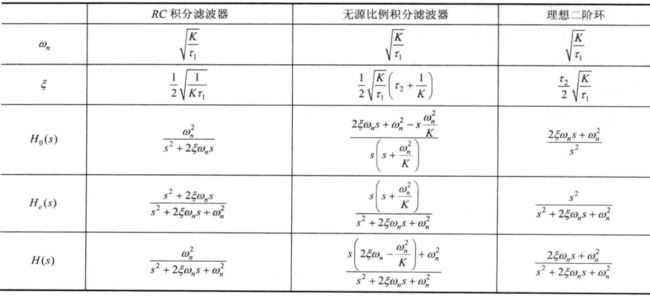

不妨将不同的环路滤波器的传递函数代入得下表:

显然此时的二阶系统经线性化后变成二阶线性系统,这个的话我们在学校学的知识就已经足以应付了(特别是电路),此时定义描述二阶线性系统的两个系统常量:无阻尼振荡频率和阻尼系数来描述系统的响应,对应关系见下表:

结语

这里先省略锁相环的性能分析,搞这个有点累,放到下一篇(或下几篇)博客再讨论,或者边实战边讨论吧.因为电赛这次做得题目最多就做一个位同步而已,根本就没有这么多的东西要看.我也只是先做一点基础铺垫,以免后面出问题.

想我尽早更新的方法之一