HDLBits之Verilog学习记录 Day8

1 Adder 1

作业:

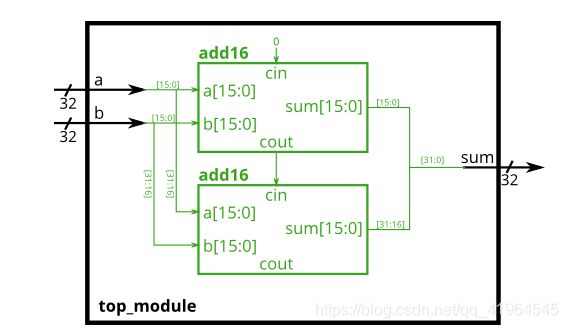

给出了一个可以做16bit加法的模块add16,实例化两个add16以达到32bit加法的。一个add16模块计算结果的低16位,另一个add16模块在接收到第一个的进位后计算结果的高16位。此32bit加法器不需要处理输入进位(假设为0)和输出进位(无需进位),但为了内部模块为了结果的正确仍要处理进位信号。(换句话说,add16模块执行16bit的a+b+cin,而顶层模块执行32bit的a+b)

如下图所示将模块连接在一起。提供的模块add16具有以下声明

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout1;

add16 instance1(.a(a[15:0]),.b(b[15:0]),.cin(1'b0),.sum(sum[15:0]),.cout(cout1));

add16 instance2(.a(a[31:16]),.b(b[31:16]),.cin(cout1),.sum(sum[31:16]),);

endmodule

2 Adder 2

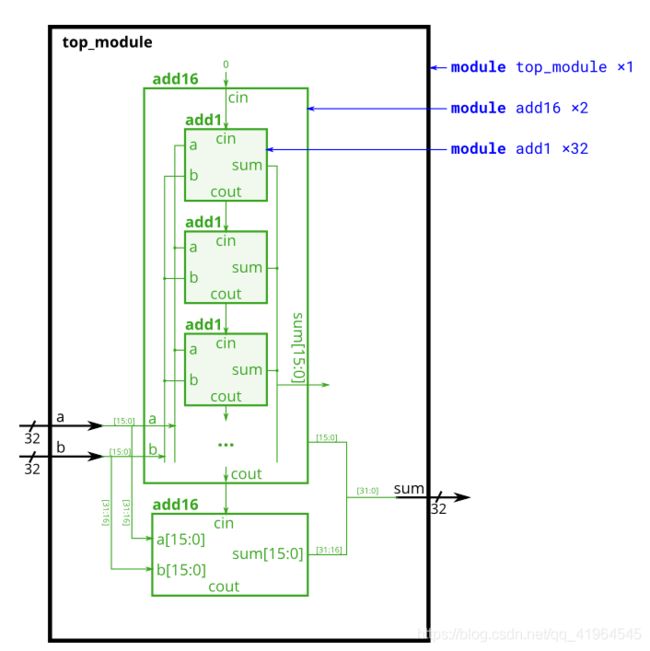

在本练习中,您将创建一个具有两个层次结构的电路。您top_module将实例化add16(提供)的两个副本,每个副本将实例化add1(您必须编写)的16 个副本。因此,您必须编写两个模块:top_module和add1.

与Problem 24: Adder 1(Module add)一样,提供给您一个执行16bit的加法的模块。您需要实例化两个16bit加法模块来实现32bit加法器。一个add16计算加法结果的低16位,另一个计算结果的高16位。您的32位加法器同样不需要处理进位输入(假设为0)和进位输出(无需进位)信号。

如下图所示,将add16模块连接在一起,给出的add16模块如下:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

在每个 中add16,16 个全加器(模块add1,未提供)被实例化以实际执行加法。您必须编写具有以下声明的完整加法器模块:

module add1 ( input a, input b, input cin, output sum, output cout );

回想一下,全加器计算 a+b+cin 的总和和进位。

综上所述,本设计共有三个模块:

- top_module — 包含两个16位加法器的顶级模块;

- add16, 提供 — 一个16bit的加法器,由16个全加器构成;

- add1 — 1 位全加器模块。

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire cout1;

add16 instance1(a[15:0],b[15:0],1'b0,sum[15:0],cout1);

add16 instance2(a[31:16],b[31:16],cout1,sum[31:16],);

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

assign sum = a ^ b ^ cin;

assign cout = a&b|a&cin|b&cin;

endmodule