基于 xilinx vivado 的PCIE ip核设置与例程代码详解

1.概述

本文是用于总结PCIE ip例程的学习成果。主要是从ip的设置,ip核的例程代码构成及其来源两方面介绍pcie的使用情况。

2.参考文档

《pg054-7series-pcie》

《PCI_Express_Base_Specification_Revision_3.0》

3. pcie ip设置

3.1 本例程使用环境

编译环境:vivado 2017.4

选用FPGA:xc7k325t-2ffg900i

3.2 IP界面设置情况

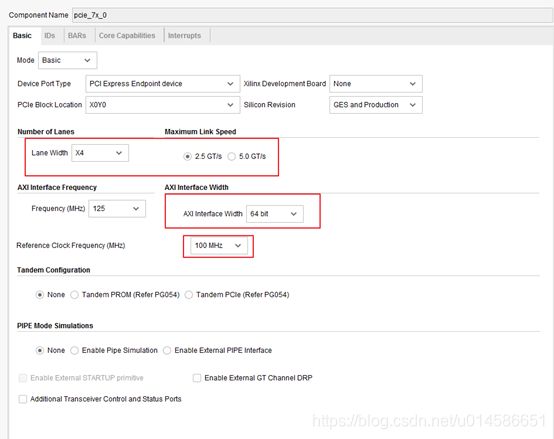

本例程主要是使用Basic模式,下面是IP设置情况。

3.2.1 IP第1页设置情况

- Devie port type:即设备的类型,一般用FPGA这边做的PCIE板卡都是endpoint device;

- Lane width:即常说的x几的几,对应接口连接就是高速GTX的对数;

- Link speed:即lane rate,这个速度与使用pcie版本相关,最大值有限制;

- AXI Frequency:不用自己设置,其值是根据link speed自动变化设置的;

- AXI interface width:即传输数据的位宽,此位宽受限于link speed,2.5G时只能选择64bit;

- Reference clock frequency:即GTX上的参考时钟;

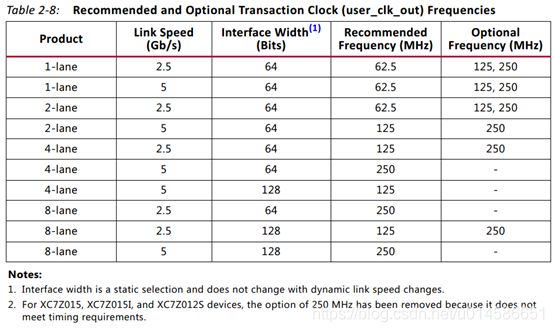

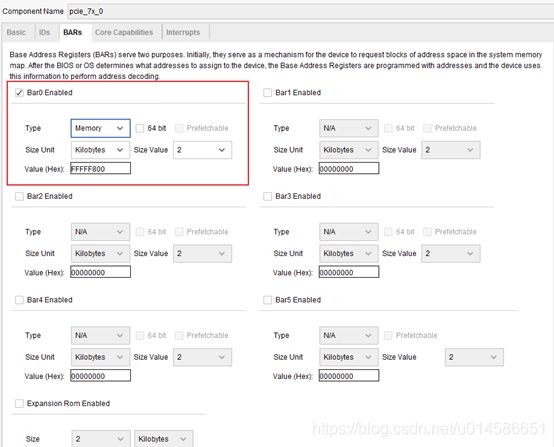

3.2.2 IP第2页设置情况

- ID initial values:是一个PCIE卡的识别码,只有一张板子时可以不修改;

- Class code:种类等级码,根据使用修改base class menu即可,其他可以不修改;

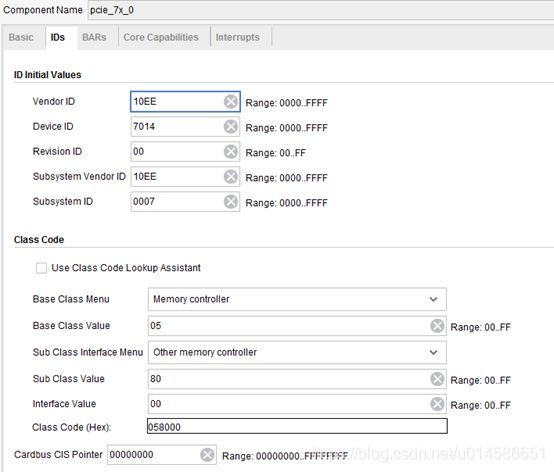

3.2.3 IP第3页设置情况

这一页主要是BAR的设置,即办卡内存的大小设置,数量设置,与使用位数设置;

这里选择64bit,则程序中选择使用的为4DW头,若没勾选则使用的是3DW头;

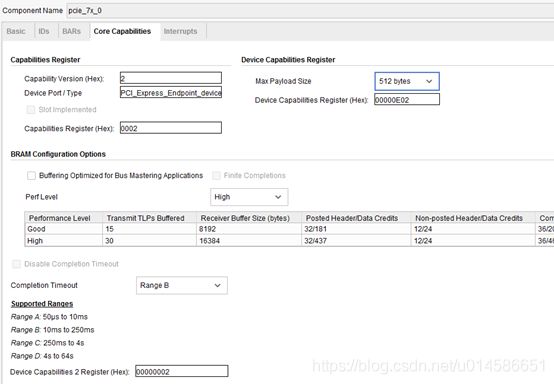

3.2.4 IP第4页设置情况

这一页主要是PCIE device的buff能力的设置与设备类型的总结;基本上可以不做改变;

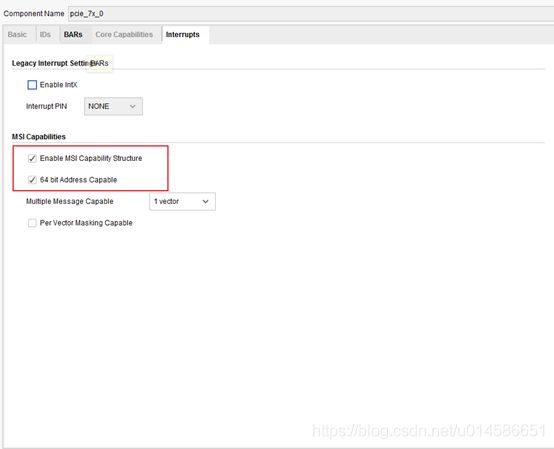

3.2.5 IP第5页设置情况

这一页主要是中断的选择,常用的是下面的MSI中断;

4. IP例程代码情况

这里例程的代码结构是PIO形式的,所谓PIO就是Programmed Input/Output,更通俗的解释就是从机模式,无论是读写都是需要CPU发送信号过来,FPGA这边根据接收到的命令进行读或者写。

此外本例程是每次只发送一个数据长度的数据,即一个包只发送32bit的数据。

这里用3DW头,64bit数据位宽作为讲解。4DW头、128bit数据位宽的类容基本类似,类推即可。

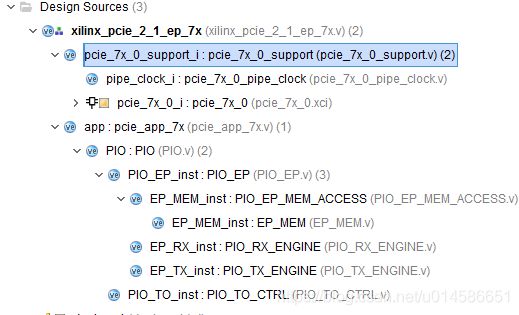

4.1 代码结构

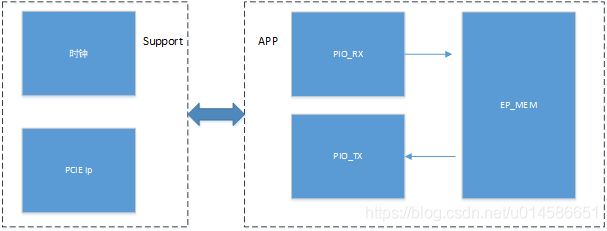

由上图可以知道PCIE的例程是由两部分组成,一个是support模块,一个是app部分。主要结构如下图所示:

Support模块主要是由PCIE的ip与时钟两部分组成,这一部分是不用修改的,直接沿用即可,所以这里不做过多介绍。

APP模块主要是由3部分组成:

- PIO_RX:用于接收CPU发送过来的命令与数据;

- PIO_TX:用于向CPU发送数据;

- EP_MEM:内存情况,即IP设置中BAR的对应区域,也是缓存数据的区域;

4.2 PIO_RX模块介绍

在实际运用过程中PIO_RX模块是很可能改变的一个模块,我们并不是要把接收到的数据存储在mem中,也可能将其发送到其他地方,比如说通过DAC发给其他设备,因此这里作为一个重点讲解。

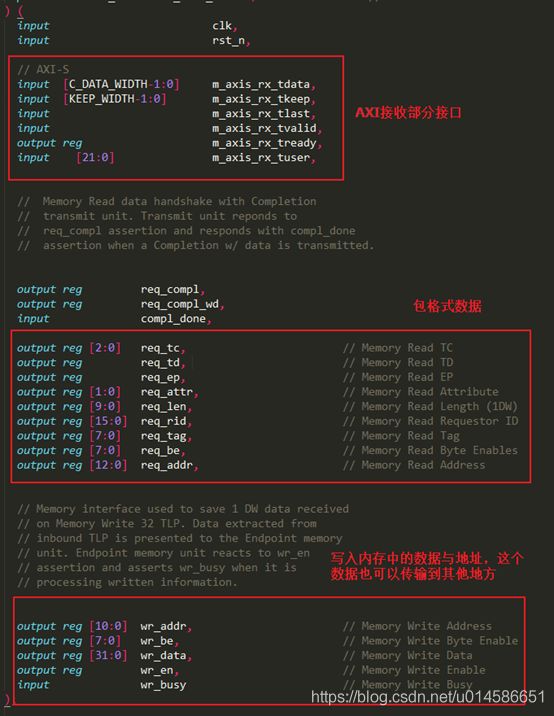

4.2.1 PIO_RX接口部分说明

4.2.2 PIO_RX代码内容说明

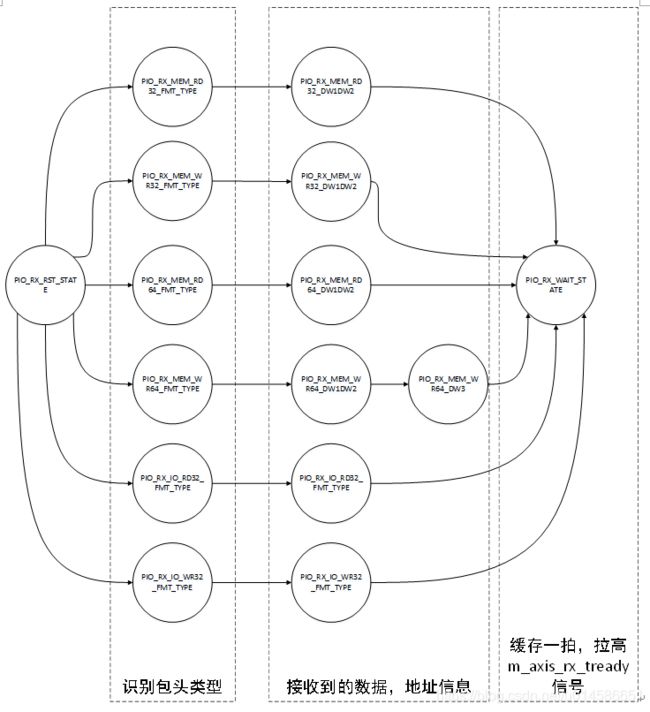

RX里的代码主要是分两部分编写,首先识别是哪一种包,然后根据包的类型接收数据。

其代码流程如下图所示:

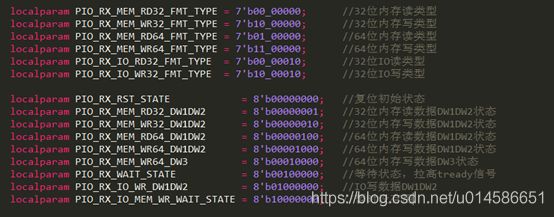

其包头类型识别状态机说明如下图所示:

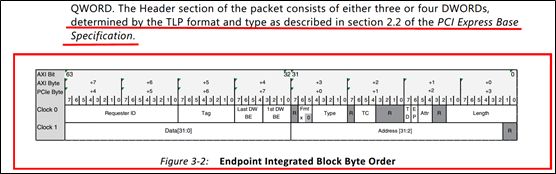

接收包的数据格式如下图所示:

需要注意的是这个“endpoint integrated block byte order”中的包格式只是32位的格式,即这个头是3DW的头。若是64位的格式(4DW)则途中的data[31:0]换成address[63:32],数据放到下一个时钟去(这也是PIO_RX_MEM_WR64_DW3状态的来源)。

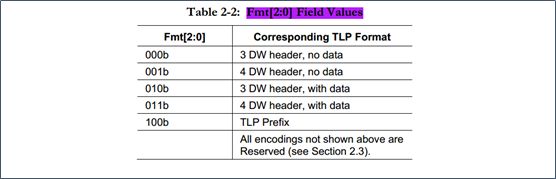

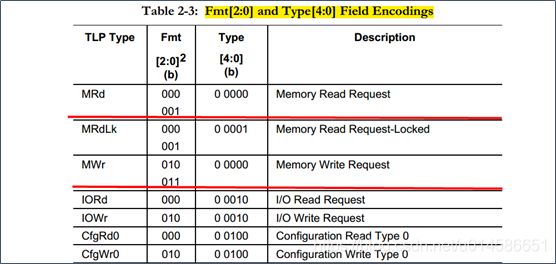

其包头类型的划分依据如下所示:

4.3 PIO_TX模块介绍

PIO_TX模块也是实际使用中很可能改变的模块,因为在实际使用中不一定只是上传内存中的数据,还可能是上传其他地方过来的数据,比如上传ADC采集到的数据。

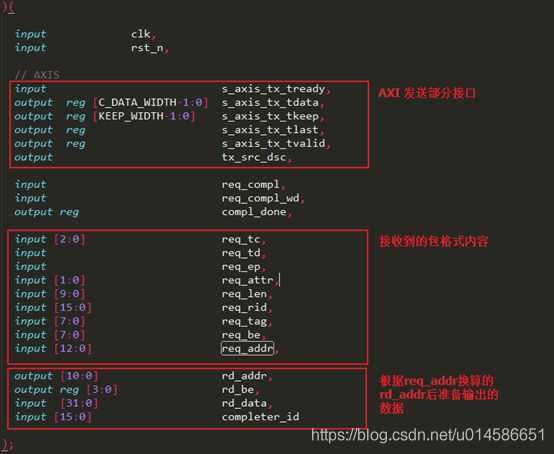

4.3.1 PIO_TX接口部分说明

4.3.2 PIO_TX代码内容说明

TX部分代码得到了整合,无论是回传带数据的格式包还是不带数据的包格式都相同,因为可以用用有效位区分开。

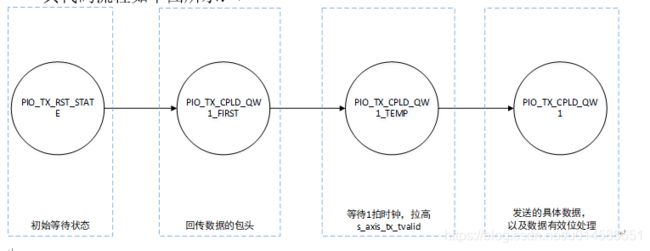

其代码流程如下图所示:

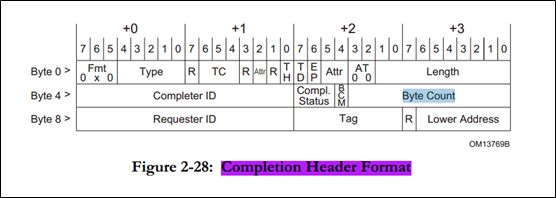

其回传数据的包头依据如下图所示:

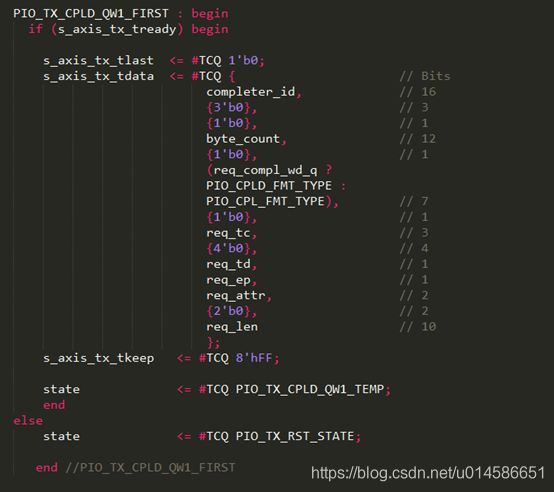

回传数据的帧头部分代码如下图所示:

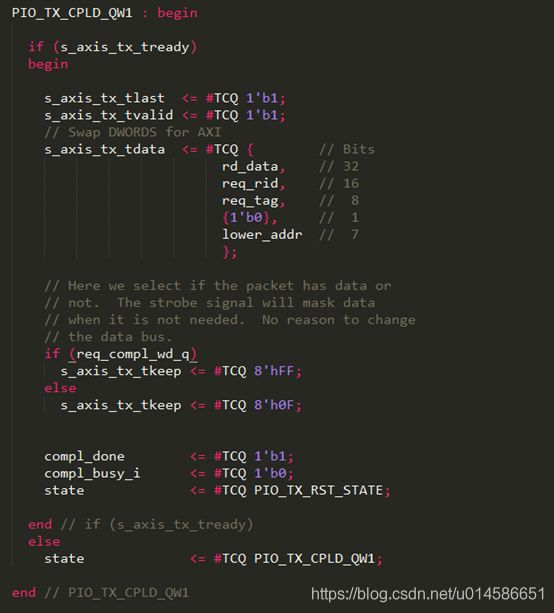

其回传的数据包部分如下所示:

下面我们来说说代码中的信号来源:

代码中的req_tc,req_td,req_ep,req_attr,req_len,req_rid,req_tag都比较清楚,它们是来自RX模块从CPU那边接收过来的数据。

rd_data:是我们要回传的数据。

completer_id:是来至于cfg_completer_id = { cfg_bus_number, cfg_device_number, cfg_function_number };即ip的cfg_status输出的状态;

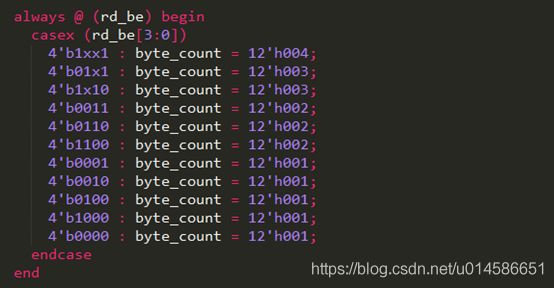

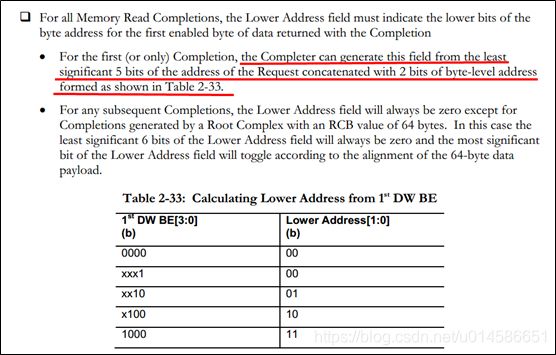

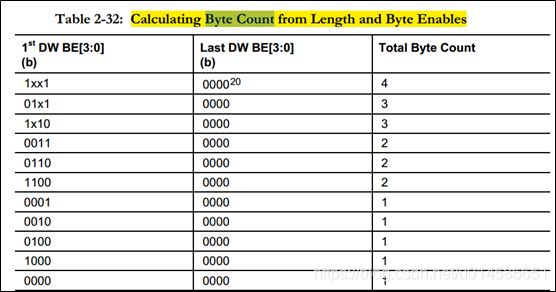

byte_count:是根据length与byte enables计算的。其计算的依据是:

其计算的代码为:

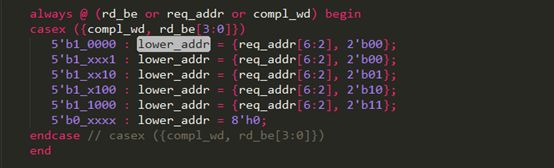

lower_addr:是来至于接收到的请求地址的5位+(1st DW BE)计算出来的值。

其计算依据为:

其代码组成为:

5. 代码注意事项

需要注意的是:

2017.4版本vivado基于K7的FPGA 产生的IP其数据(s_axis_tx_tdata,m_axis_rx_tdata)中的高32位低32位与《PCI_Express_Base_Specification _Revision_3.0》中的包格式相反;